Способ измерения электрических напряжений

Иллюстрации

Показать всеРеферат

) СПОСОБ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКИХ НАПРЯЖЕНИЙ, заключающийся в том, что формируют первое и второе образцовые напряжения, суммируют измеряемое напряжение с первым образцовым , отличающийся тем, что, с целью повышения точности, измеряют полученную сумму,, измеряют .первое и второе образцовые напряжения , затем находят разности первого и втор.ого, а также третьего и второго результатов измерений, делят первую из указанных разностей на вторую, умножают на разность второго и первого образцовых напряжений и по полученному результату судят о вели (Л чине измеряемого напряжения.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ ,.РЕСПУБЛИК (51)4G 01 R 19/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

110 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ.

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3611773/24-21 (22) 11.03.83 (46) 30,08.85. Бюл. 32 (72) Г.Г,Бондарович, В. Г.Кутас, Н.A,Ñîêîëîâà и В.Г.Цывинский (71) Киевский ордена Ленина политехнический институт им.50-летия Великой

Октябрьской социалистической революции (53) 621.317.7(088.8) (56) Авторское свидетельство СССР

Р 331321, кл. G 01 R 19/00, 1970.

Авторское свидетельство СССР

У 467280, кл. С 0.1 R 19/00, 1973.

„„Я0„„1176255 A (54) (57) СПОСОБ ИЗМЕРЕНИЯ ЭЛЕКТРИ .ЧЕСКИХ НАПРЯЖЕНИЙ, заключающийся в том, что формируют первое и второе образцовые напряжения, суммируют измеряемое напряжение с первым образцовым, отличающийся тем . что, с целью повышения точности, измеряют полученную сумму,, измеряют первое и второе образцовые напряжения, затем находят разности первого и второго, а также третьего и второго результатов измерений, делят первую из указанных разностей на вторую, умножают на разность второго и первого образцовых напряжений и по полученному результату судят о величине измеряемого напряжения.

1176255 где N„

К вЂ” результат измерения; — коэффициент передачи измерителя; 25 — мул ьтиплика тив ная по грешность измерения (нестабильность коэффициента передачи); — измеряемая величина; — первая образцовая мера; 30 аддитивная погрешность измерения (дрейфа нуля).

Измеряется первая образцовая

2) мера

=K (1+y)xp+, 35 где И вЂ” результат измерения.

3) Измеряется вторая образцовая мера

И5 = К (1 + )x„ + а, (3) 4О где N5 — результат измерения; х — вторая образцовая мера;

Для оценки измеряемой величины вычисляется соотношение

45 12. х =- — — — (х -х). (4) 3 N2

После подстановки выражений 1-3 в выражение (4) можно убедиться, что результат вычисления не зависит ни от аддитивной, ни от мультиплика« тивной погрешностей измерения.

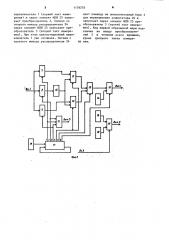

Устройство для реализации предлагаемого способа (фиг. 1) содержит переключатель 1, вход которого является входом устройства, а выход подключен к первому входу сумматора

Изобретение относится к электроизмерительной технике и может быть использовано для измерения постоянного напряжения.

Цель изобретения — повышение точности за счет устранения аддитивной составляющей погрешности измерения.

На фиг. 1 представлена блок-схема устройства для реализации предлагаемого способа; на фиг. 2 - пример 10 выполнения вычислительного блока; на фиг, 3 — пример выполнения блока управления.

Способ осуществляется следующим образом. 15

Последовательно производятся три измерения.

I) Измеряется измеряемая величина, просуммированная с первой образцовой мерой 2О

N = К(1+1) (х + xo) + d,,(1) 2, выход которого через преобразователь 3 напряжения в код подключен к первому. входу вычислительного блока 4, первый выход которого является выходом устройства, второй выход через преобразователь 5 кода в напряжение подключен ко второму входу сумматора 2, в третий выход— подключен ко входу блока 6 управления, первый выход которого подключен к управляющему входу переключателя 1, второй выход — ко входу запуска преобразователя 3, а третий выход — ко второму входу вычислительного блока 4.

Вйчислительный блок 4 (фиг. 2) содержит запоминающие регистры 7-9, входы которых подключены к первому входу блока 4, инверторы 10, входы которых подключены к выходам регистра 8, а выходы — к. первым входам сумматоров 11 и 12, вторые входы которых подключеньгсоответственно к выходам регистров 7 и .9,,а выходы— соответственно к первому и второму входам делителя 13, формирователь 14 постоянного коэффициента, выход которого подключен к первому входу умножителя 15, к первому входу которого подключен выход делителя

13, выход которого образует первый выход блока 4, генератор 16 импульсов, выход которого подключен ко входу распределителя 17 импульсов, первый выход которого подключен к управляющему входу регистра 7, второй выход — к управляющему входу регистра. 8, третий выход — к управляющему входу регистра 9, четвертый выход - .к управляющим входам сумматоров 11 и 12 пятый выход — к управляющему входу делителя 13, шестой выход — к управляющему входу умножителя 15, выходы формирователей 18 и 19 эталонных кодов поключены к входам коммутатора 20 кодов, управляющий вход которого является входом блока 4, а выход— вторым выходом блока 4, и элемент

ИЛИ 21, первый, второй и третий входы которого подключены соответственно к первому, второму и третьему выходам распределителя 17, а выход образует третий выход блока 4.

Блок б управления .(фиг. 3) содержит генератор 22 импульсов, выход которого подключен к одному входу з 117 элемента И 23, к другому входу которого подключен вход блока 6, а к выходу — вход распределителя 24 импульсов, первый выход которого образует первый выход блока 6 и подключен к первому входу элемента

ИЛИ 25, второй выход подключен ко второму входу элемента ИЛИ 25, а третий выход образует третий выход блока 6 и подключен к третьему входу элемента ИЛИ 25, выход которого образует второй выход блока 6.

Устройство работает следующим образом.

Я первом такте работы устройства блок 6 управления по команде вычислительного блока 4 замыкает контакт переключателя 1 и подает команду блоку 4 на формирование кода NpÄ . Код МО1, сформированный на втором выходе блока 4, .преобразуется в сигнал напряжения Upq посредством преобразователя 5. На выходе сумматора 2 формируется сигнал напряжения Uz + П „.

По команде блока 6 преобразователь 3 вырабатывает код N соответствующий сигналу U + U „ . По следующей команде блока 6 код М„ запоминается блоком 4.

Во втором такте блок 6 размыкает контакт переключателя 1. На выходе сумматора 2 формируется сигнал напряжения Uo, по командам блока 6 преобразуемый в код И2 и запоминаемый блоком 4.

В третьем такте блок 6 подает команду блоку 4 на формирование кода . N p . Код Np преобразуется в напряжение

U посредством преобразователя 5.

Напряжение U 1 через сумматор 2 поступает на вход преобразователя 2 и по команде блока 6 преобразуется

В четвертом такте работы устройства блок 4 по формуле (4) вычисляет код И, соответствующий значению измеряемого напряжения U» формирует N на выходе устройства и подает блоку 6 сигнал об окончании измерения. После этого описанный процесс повторяется.

Устройство устраняет аддитивную и мультииликативную составляющие пог- . решности преобразователя 3 напряжения в код с точностью, определяемой точностью преобразователя 5 кода в напряжение, 6255

55

4

Вычислительный блок 4 работает . следующим образом.

По импульсу с первого выхода распределителя 17 импульсов, который может быть реализован, например, в виде сдвигового регистра, результат первого измерения N с выхода преобразователя 3 запоминается в регистре 7. По импульсу со второго выхода распределителя 17 результат второго измерения N2 запоминается в регистре 8. По имйульсу с третьего выхода распределителя 17 результат третьего измерения N запоминается в регистре 9. Код N<, запомненный в регистре 8, инвертируется набором инверторов 10, количество которых определяется количеством разрядов преобразователя 3. По импульсу с четвертого выхода распределителя 17 сумматоры 11 и 12 определяют соответственно суммы N + (- Н ) и

N > + (- N ), отношение которых по импульсу с пятого выхода распределителя 17 определяет делитель 13 1х (††††). Результат деления умно3 2 жается на постоянный коэффициент (х1 — х ) умножителем 15 по сигналу с шестого выхода распределителя 17.

Формирователем 14 постоянного коэффициента может служить, например, набор переключателей. Сигналы с первого, второго, третьего выходов распределителя 17 через элемент ИЛИ 21 разрешают работу блока управления 6.

Формирователи эталонных кодов 18 и 19 могут быть реализованы, например, на наборах переключателей и формируют коды соответствующие первой и второй образцовым мерам

Xp Nâ clX

Х1 И1 4ХУ где дХ вЂ” шаг квантования преобразователя 5.

Коммутатор 20 кодов подключает коды ко входу преобразователя 5 по сигналу с блока 6 управления, Блок 6 управления работает следующим образом.

Сигнал с вычислительного блока 4 разрешает прохождение тактовых импульсов с генератора 22 через элемент И 23 на распределитель 24, Импульс с первого выхода распределителя 24 дает команду на замыкание

1176255 переключателя 1 (первый такт измерения) и через элемент ИЛИ 25 запускает преобразователь 3. Сигнал со второго выхода распределителя 24 через элемент ИЛИ 25 запускает преобразователь 3 (второй такт измерения). Лри этом однопозиционный переключатель 1 уже отключен, Сигнал с третьего выхода распределителя 24 дает команду на вычислительный блок 4 для переключения коммутатора 20 и запускает через элемент ИЛИ 25 преобразоватепь 3 (третий такт измерения). Код первой образцовой меры под, ключен ко входу преобразователей 5 в течение всего времени, кроме гретьего такта измере-!

О ния.

1176255

Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д . 4/5

Заказ 5355/45

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель С. Рыбин

Редактор С. Тимохина Техред И,Надь Корректор !Л. Бескид