Накапливающий сумматор

Иллюстрации

Показать всеРеферат

НАКАПЛИВАЮЩИЙ СУММАТОР, со держащий в каждом разряде первый и , второй Р5-триггеры, семь элементов И и два элемента ИЛИ, причем входы . первого элемента И соединены с шиной :управления сложением по модулю два и с выходом переноса предыдущего разряда сумматора соответственно, входы второго элемента И соединены с шиной управления приемом кода второго слагаемого и с соответствующим разрядом входной шины сумматора соответственно , выходы первого и второго элементов И подключены к соответствующим входам первого элемента ИЛИ, выход которого соединен с первыми входами третьего и четвертого элементов И, выходы третьего и четвертого элементов И соединены соответственно с (I- и S-входами пер-: вого ЯЗ триггера, инверсный выход которого соединен с первым входом пятого элемента И, а прямой выход с первым входом шестого элемента И, 8С Гогл тдл I БЕБЛйОТь}/, вторые входы пятого и шестого элементов И подключены к шине управления пересылкой кода сумматора, прямой и инверсный вьтходы второго RS-триггера соединены с вторыми входами третьего и четвертого элементов И соответственно, первый вход седьмого элемента И соединен с выходом предьдущего разряда сумматора, выход седьмого элемента И соединен с первым входом второго элемента ИЛИ, выход которого подключен к выходу переноса данного разряда сумматора, отличающийся тем, что, с целью упрощения конструкции, накапливающий сумW матор содержит в каждом разряде восьмой элемент И и третий элемент ИЛИ, первый вход восьмого элемента И соединен с выходом , второго элемента ИЛИ, а второй вход - с шиной стробирования переноса сумматора, а выход подключен к второму входу второ | го элеме| та ИЛИ, третий вход котороо го соединен с выходом третьего элемента И, первый вход третьего эле00 мента ИЛИ соединен с;прямым выходом го второго / 3-триггера, R- н 5-входы со которого подключены к выходам пятого и шестого элементов И соответственно , второй вход третьего элемента ИЛИ соединен с выходом шестого элемента И, а третий вход - с выходом второго элемента И, выход третьего элемента ИЛИ соединен с вторым вход6м седьмого элемента И.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН рц4 G 06 F 7/50

ВСЕ(а И1щ

13 ц!

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

ГО Д1.„ЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPGHOMY СВИДЕТЕЛЬСТВУ (21) 3719267/24-24 (22) 06.01.84 (46) 30.08.85. Бюл. Ф 32 (72) Б.M.Âëàñîâ, В.А.Фотин, Н.В.Краснова и Т.Б.Власова (53) 681.325.5 (088.8)

: (56) Папернов А.А. Логические основы ЦВТ. М.: Советское радио, 1972,. с. 158, рис. 13.

Авторское свидетельство СССР

У 1112363, кл. G 06 F 7/50, 1983. (54) (57) НАКАПЛИВАЮЩИЙ СУММАТОР, со-. держащий в каждом разряде первый и второй КЭ-триггеры, семь элементов И и два элемента ИЛИ, причем входы . первого элемента И соединены с шиной управления сложением по модулю два . и с выходом переноса предыдущего разряда сумматора соответственно, входы второго элемента И соединены с шиной управления приемом кода второго слагаемого и с соответствующим разрядом входной шины сумматора соответственно, выходы первого и второго элементов И подключены к соответствующим входам первого элемен: та ИЛИ, выход которого соединен с первыми входами третьего и четвертого элементов И, выходы третьего и четвертого элементов И соединены соответственно с R- u S-входами пер-. вого RS-триггера, инверсный выход которого соединен с первым входом пятого элемента И, а прямой выход— с первым входом шестого элемента И, „„SU„„1176323 A вторые входы пятого и шестого элементов И подключены к шине управления пересылкой кода сумматора, прямой и инверсный выходы второго 8-триггера соединены с вторыми входами третьего и четвертого элементов И соответственно, первый вход седьмого элемента И соединен с выходом переноса предыдуп1его разряда сумматора, выход седьмого элемента И соединен с первым входом второго элемента ИЛИ, выход которого подключен к выходу переноса данного разряда сумматора, о т л и ч а ю— шийся тем, что, с целью упро- Я щения конструкции, накапливающий сумматор содержит в каждом разряде восьмой элемент И и третий элемент ИЛИ, первый вход восьмого элемента И соединен с выходом второго элемен- Я та ИЛИ, а второй вход — с шиной стробирования переноса сумматора, а выход подключен к второму входу второ- Мш го элемента ИЛИ, третий вход которо- ФААД го соединен с выходом третьего эле- . ©ф мента И, первый вход третьего эле- фр мента ИЛИ соединен с,прямым выходом р р второго Ю>-триггера, R- и 5-входы фф которого подключены к выходам пятого и шестого элементов И соответственно, второй вход третьего элемента ИЛИ соединен с выходом шестого элемента И, а третий вход - с вы- фЬ ходом второго элемента И, выход третьего элемента ИЛИ соединен с вторым входом седьмого элемента И.

1176323

Изобретение относится к цифровой вычислительной технике и предназначается для использования в процессорах ЭВИ или в устройствах цифровой автоматики. 5

Цель изобретения — упрошение конструкции накапливающего сумматора.

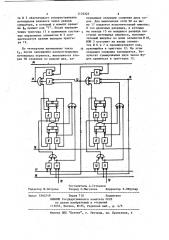

На чертеже представлена функциональная схема двух разрядов накапливающего сумматора. 10

Каждый разряд накапливающего сумматора содержит элементы ИЛИ 1-3, элементы И 4-11, RS-триггеры 12 и 13, шину 14 стробирования переноса, выход 15 переноса в следующий разряд, 15 шину 16 управления пересылкой кода, шину 17 управления сложением по модулю два, шину 18 управления приемом кода второго слагаемого и входную шину 19. PS -триггеры 12 и 13 и соответствующие элементы И 6 — 9 образуют триггер со счетным входом.

Рассмотрим работу сумматора при выполнении сложения двух чисел; представленных в двоичном коде. Напри- д5 мер, код первого слагаемого хранится в триггерах 12, а код второго слагаемого поступит в сумматор по шине 19.

По первому временному такту Ф„ выполняются подготовительные элементарные операции (ЭО ) пересылки кода из основных триггеров 12 во.вспомогательные триггеры 13 и стробирование схем переносов. Элементарная операция пересылки кода необходима для подго- З» товки триггеров 12 и 13 к работе в режиме счетного триггера. Для выполнения этой элементарной операции на шину 16 подается исполнительный импульс. Если триггер 12 хранит код 40

"1", то исполнительный импульс через элемент И 9 поступит на 5-вход триггера 13 и установит его в состояние "1". Если триггер 12 хранит код

"0", то исполнительный импульс через элемент И 8 поступит íà R-вход триггера 13 и установйт его в состояние "О". Таким образом, по первому временному такту триггеры 12 и 13 устанавливаются в одинаковые состоя- gp ния. Одновременно с пересылкой кода из триггеров !2 в триггеры 13 производится "гашение" переносов во всех двоичных разрядах сумматора. Эта ЭО выполняется для исключения возможных 5 потенциалов, хранящихся з цепи сквозI ного переноса от предыдущей операции сложения. Для "гашения" переносов во всех разрядах сумматора на шину 14 подается нулевой потенциал, за счет чего разрывается цепь обратной связи между элементами ИЛИ 1 иИ4.

По второму временному такту выполняется ЭО первого сложения по модулю два. Для ее выполнения на шину 18 подается исполнительный импульс. В это же время на шины 19 поступает код второго слагаемого.

Если в данном двоичном разряде на шину 19 поступил код ",1" то исУ полнительный импульс по цепи элементов И ll, ИЛИ 3 поступит на входы элементов И 6 и И 7 и проинвертирует код хранящийся в триггере 12.

Если до прихода счетного импульса в триггерах 12 и 13 хранился код

"1", то исполнительный импульс череэ элемент И 6 поступит на нулевой вход триггера 12 и через элемент ИЛИ 1 поступит в цепь сквозного переноса данного разряда и далее в следующий разряд сумматора. Сигнал переноса, выработанный в данном разряде сумматора, запоминается за счет элемента И 4, к первому входу которого подключен выход элемента ИЛИ 1.

Если в рассматриваемом разряде сумматора триггеры 12 и 13 до поступления второго исполнительного импульса находились в нулевом состоянии, то исполнительный импульс по цепи элементов И 11, ИЛИ 3, И 7 поступит на 5-вход триггера 12. Кроме того, исполнительный импульс по цепи элементов И ll, ИЛИ 2 поступит на первый вход элемента И 5, разрешая прохождение потенциала сквозного переноса из младшего разряда через элемент И 5, ИЛИ 1 в .следующий разряд.

По третьему временному такту выполняется ЭО второй пересылки кода из триггеров 12 в триггеры 13. Для выполнения этой элементарной операции на шину 16 подается исполнительный импульс. Если в триггере 12 хранится код "0" то исполнительный импульс через элемент И 8 поступит на

Я-вход триггера 13 и установит его в нулевое состояние. Если же в триггере 12 хранится код "1", то исполнительный импульс через элемент И 9 поступит на 5-вход триггера 13. Одновременно этот импульс поступит на второй вход элемента ИЛИ 2 и далее на вход И 5. Наличие исполнительного импульса ф на входе элеменСоставитель А.Степанов

Техред С.Мигунова Корректор А.Обручар

Редактор М.Петрова

Заказ 5362/48 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

3 1176323 .4 та И 5 обеспечивает распространение вершающая операцию сложения двух копотенциала пененоса через Разряд, дов. фея выполнения этой ЭО на шисумматора, в который в момент време ну 17 подается исполнительный импульс. йи ф принят, код "1". После переклю В тех двоичных разрядах, в которых чения триггера 13 в единичное состоя- g на выходе 15 из младшего разряда поние управление элементом И 5 осу- ступил потенциал переноса, исполниществляется прямым выходом тригге- тельный импульс по цепи элементов И 10, ра 13. ИЛИ 3 поступит на входы элементов И 6 и 7 и проинвертирует код, По четвертому временному такту lp хранящийся в триггере 12. На этом

, после завершения распространения операция сложения завершается. Репотенциала переноса, выполняется вто- зультат суммирования двух чисел бурая ЭО сложения по модулю два, за- дет храниться в триггерах 12.