Цифровая система с тестовым диагностированием

Иллюстрации

Показать всеРеферат

ЦИФРОВАЯ СИСТЕМА С ТЕСТОВЫМ ДИАГНОСТИРОВАНИЕМ, содержащая генера тор тестовых воздействий, блок хранения эталонных реакций, блок сравнения , основное и вспомогательное вычислительные устройства, каждое из которых состоит из блока буферной памяти, арифметико-логического блока и запоминающего блока, причем выход блока хранения эталонных реакций соединен с первым входом блока сравнения , первый информационный вход каждого арифметико-логического блока .соединен с выходом соответствуняцего блока буферной памяти, первый выход каждого арифметико-логического блока - с информационным входом соответствующего запоминающего блока, входы синхронизации блоков буферной памяти запоминающих блоков, генератора тестовых воздействий и блока хранения эталонных реакций соединены с синхровходом системы, отличающаяс я тем, что, с целью повышения точности диагностирования цифровых систем, введены счетный триггер, два элемента И и четыре коммутатора, причем первые информационные входы первого И второго коммутаторов соединены с информационным входом системы, «торые информационные входы первого t и второго коммутаторов соединены с выходом генератора тестовых воздействий , а выходы первого и второго коммутаторов - соответственно с информационными входами блоков буферной памяти основного и вспомогательного вычислительных устройств, первые информационные входы третьего и четвертого коммутаторов соединены со вторым выходом арифметико-логического блока основного вычислительного устройства, а вторые информационные входы - с цторьм выходом арифметикологического блока вспомогательного вычислительного устройства, выходы третьего и четвертого коммутаторов (Л соединены соответственно с информационным выходом системы и со вторым входом блока сравнения, управляющие входы первого и третьего коммутаторов соединены с прямым выходом счетного триггера, а управляющие входы второго и четвертого коммутаторов с инверсным выходом счетного триггеОд ра, вторые информационные входы со со ел арифметико-логических блоков основного и вспомогательного вычислительнь1х устройств соединены с выходами запоминающих блоков вспомогательного и основного вычислительных устройств соответственно, первые входы элементов И соединены с выходами блока . сравнения, вторые входы первого и второго злементов И соединены с прямым и инверсным выходами счетного триггера соответственно,а выходы первого и второго элементов И являются выходами ми сигналов ошибок вспомогательного и основного вычислительных устройств соот ветственно ,вход счетного триггера соединен с синхровходом системы.

СОЮЗ СООЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПИЬЛИН (51) 4 С 06 F 11/26

И, g ИИЯ01 :ö,ц

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3627736/24-24 (22) 27.07.83 (46) 30.08.85. Вюл. В 32 (72) Н.В. Колесов, В.П.Подкопаев, В.С.Толстяков и А.Е.Шумский (71) Ленинградский ордена Ленина электротехнический институт им. В.И.Ульянова (Ленина1 (53) 681.3(088.8) (54)(57) ЦИФРОВАЯ СИСТЕМА С ТЕСТОВЫМ

ДИАГНОСТИРОВАНИЕМ, содержащая генератор тестовых воздействий, блок хранения этапонных реакций, .блок сравнения, основное и вспомогательное вычислительные устройства, каждое из которых состоит иэ блока буферной памяти, арифметико-логического блока и запоминающего блока, причем выход блока хранения эталонных реакций соединен с первым входом блока сравнения, первый информационный вход каждого арифметико-логического блока ,соединен с выходом соответствующего блока буферной памяти, первый выход каждого арифметико-логического блока — с информационным входом соответствующего запоминающего блока, входы синхронизации блоков буферной памяти запоминающих блоков, генератора тестовых воздействий и блока хранения эталонных реакций соединены с синхровходом системы, о т л и ч а ю щ а яс я тем, что, с целью повышения точности диагностирования цифровых систем, введены счетный триггер, два элемечта И и четыре коммутатора, причем первые информационные входы первого и второго коммутаторов соединены с информационным входом системы. вторые информационные входы первого

„„SU„„ I 126335 А и второго коммутаторов соединены с выходом генератора тестовых воздействий, а выходы первого и второго коммутаторов — соответственно с информационньпчи входами блоков буферной памяти основного и вспомогательного вычислительных устройств, первые информационные входы третьего и четвертого коммутаторов соединены со вторым выходом арифметико-логического блока основного вычислительного устройства, а вторые информационные входы — с вторым выходом арифметикологического блока вспомогательного с вычислительного устройства, выходы третьего и четвертого коммутаторов соединены соответственно с информационным выходом системы и со вторым входом блока сравнения, управляющие входы первого и третьего коммутато- Я ров соединены с прямым выходом счет0asl ного триггера, а управляющие входы второго и четвертого коммутаторов с инверсным выходом счетного тригге- 4 ра, вторые информационные входы ©1 арифметико-логических блоков основ- фф ного и вспомогательного вычислитель- фф ных устройств соединены с выходами ф запоминающих блоков вспомогательного. и основного вычислительных устройств соответственно, первые входы элементов И соединены с выходами блока . сравнения, вторые входы первого и второго элементов И соединены с прямым и инверсным выходами счетного триггера соответственно,а выходы первого и второго элементов И являются выходами ми сигналов ошибок вспомогательного и основного вычислительных устройств соответственно,вход счетноготриггера соединен с синхровходом системы.

1 1176

Изобретение относится к вычислительной технике.

Целью изобретения является повышение точности диагностирования цифровых систем. S

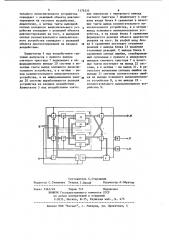

На чертеже представлена структура предлагаемой системы.

Система содержит генератор 1 тестовых воздействий, коммутаторы 2-5, блок 6 сравнения, счетный триггер 7, 10 основное и вспомогательное вычислительные устройства 8 и 9 соответственно, каждое из которых состоит иэ блоков буферной памяти 10 и 11 соответственно, арифметико-логического 15 блока 12 и 13 соответственно, запоминающего блока 14 и 15 соответственно, Кроме того, она содержит информационный вход 16, синхровход 17, первый и второй элементы И 18 и 19, информа- 20 ционный выход 20, выходы 21 и 22 сигнала ошибки основного и вспомогательного вычислительных устройств соответственно, блок 23 хранения эталонных реакций. 25

Система работает следующим образом i

Счетный триггер вырабатывает управляющий импульс.на своих прямом и инверсном выходах, передний (задний) ЗО фронт которого совпадает с нечетным (четным) и четным (нечетным) тактовым импульсом соответственно.

Тактовые импульсы поступают с синхровхода 17 системы и обеспечивают35 синхронность работы блоков буферной памяти 10 и 11 и запоминающих блоков

14 и 15 основного и вспомогательного вычислительных устройств 8 и 9, а также генератора 1 тестовых воздейст-40 вий и блока 23 хранения эталонных реакций, При наличии на управляющем входе каждого из коммутаторов управляюще;го импульса на выход коммутатора поступает сигнал с первого из его входов, а при отсутствии — со второго. В нечетных так,ах сигнал с информационного входа системы через коммутатор 2 поступает на вход ос- 50 новного вспомогательного устройства, а тестовый сигнал с выхода генератора 1 тестовых воздействий через ком" мутатор,3 — на вход вспомогательного вычислительного устройства 9 и фик- SS сируетс" в блоках памяти 10 и 11 соответств"нно. В результате сигналы на первом и втором выходах арифмети335 2 ческо-логического блока 12, в нечетном такте определяются сигналами на информационном входе 16 системы и выходе запоминающего блока 15, а сигналы на первом и втором выходах арифметико-логического блока 13— сигналами на выходе генератора I тес" товых воздействий и выходе запоминающего блока 14. В четном такте сигнал с информационного входа 16 системы через коммутатор 3 подключается ко входу вспомогательного вычислительного устройства 9, а тестовый сигнал с выхода генератора 1 через коммутатор 2 подключается ко входу основного вычислительного устройства

8 и фиксируются в блоках буферной памяти 11 и 10 соответственно. В результате сигналы на первом и втором выходах арифметико-логического блока .13 в четном такте определяются сигналами на информационном входе 16 системы и выходе запоминающего устройства 14, а сигналы йа первом и втором выходах арифметико-логического блока 12 — сигналом тестовых воздействий на выходе генератора 1 и сигналом на выходе запоминающего блока 15.

С приходом каждого тактового импульса синхровхода 17 системы осуществляется запись сигналов со вторых выходов арифметико-логических блоков 12 и 13 в запоминающие блоки 14 и 15 соответственно. Таким образом, в нечетном такте состояние запоминающих блоков 14 и 15 определяется состоянием основного и вспомогательного вычислительных устройств 8 и 9 в предыдущем (четном) такте, в которые укаэанные системы переходят под воздействием сигналов с выхода генератора 1 тестовых воздействий информационной системы и входа 16 системы соответственно. В четном такте состояние запоминающих блоков 14 и 15 определяется состоянием основного и вспомогательного вычислительных устройств в предыдущем (нечетном) такте, в которые укаэанные системы переходят под воздействием сигналов с информационного входа 16 системы и с выхода генератора 1 .тестовых воздействий. В результате в нечетные такты выходной сигнал основного вычислительного устройства совпадает с реакцией объекта диагностирования на входное воздействие, поступающее с информационного входа 16, а выходной сигнал вспомогаСоставитель С. Старчихин

Редактор С.Тимонина Техред З.Палий Корректор А.Обручар

Заказ 5363/49 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

3 ll тельного вычислительного устройства совпадает с реакцией объекта диагностирования на тестовое воздействие.

Аналогично, в четные такты выходной сигнал основного вычислительного устройства совпадает с реакцией объекта диагностирования на тест, а выходной еигнал вспомогательного вычислительного устройства совпадает с реакцией объекта диагностирования на входное воздействие.

Коммутатор 4 под воздействием тактовых. импульсов с прямого выхода счетного триггера 7 подключает к информационному выходу 20 системы в нечетные такты выход основного вычислительного устройства, а в четные — выход вспомогательного вычислительного устройства, и на информационном выходе 20 системы вырабатывается реакция устройства на входное воздействие.

Коммутатор 5 под воздействием такто76335 4 вых импульсов с инверсного выхода счетного триггера 7 подключает к пер.— вому входу блока 6 сравнения в нечетные такты выход вспомогательного вычислительного устройства, а в четныевыход основного вычислительного устройства, и на входе блока 6 сравнения формируется реакция объекта диагности. рования на тест. На второй вход блока 6 сравнения поступает эталонная реакция с выхода блока 23 хранения эталонных реакций, С выхода блока 6 сравнения сигнал ошибки, стробироваиный сигналами с прямого и инверсного выходов счетного триггера 7 в нечетные такты поступает на выход 2 системы, а в четные — на выход 21. В результате появлению сигнала ошибки на выходе 21 системы соответствует ошибка на выходе основного вычислительного устройства 8, а на выходе 22— вспомогательного вычислительного устройства 9.