Множительно-делительное устройство

Иллюстрации

Показать всеРеферат

МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее первый и второй элементы с управляемым сопротивлением , выполненные на согласованных полевых транзисторах,истоки которых подключены к инвертирующим входам первого и второго операционных усилителей соответственно, выход первого операционного усилителя -подW0ключен к затворам первого и второго полевых транзисторов, между инвертирующим входом и выходом второго операционного усилителя включен первый масштабный резистор, выход второго операционного усилителя является выходом устройства, неинвертирующий вход второго операционного усилителя подключен к шнне нулевого потенциала, второй масштабный резистор , первьй вывод которого является входом первого сигнала-сомножителя устройства, отличающее - с я тем, что, с целью упрощения, второй вывод BTOporQ масштабного ре зистора подключен к неинвертирующему входу первого операционного усилителя , сток первого полевого транзистора является входом сигнала-делиг теля устройства, вход бторого полевого транзистора является входом второго сигнала-сомножителя устройства. Од со и

СООЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1176347

А (51)4 С 06 С 7 16

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

1!

ВСРС Г .Я

1а (21) 3712241/24-24 (22) 11. 03. 84 (46) 30.08.85. Бюл. № 32 (72) А.Н. Гуляев, И.Г. Дорух, П.К. Ермоленко и В.В. Шеболков (53) 681.335-(088,8) (56) Патент США № 3675003, кл. 235-196, опублик. 1972.

Алексенко А.Г. и др, Применение прецизионных аналоговых ИС. M.:

Радио и связь, 1981, с. 93-94, рис. 3.15 б (54)(57) МНОИИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ

УСТРОЙСТВО, содержащее первый и второй элементы с управляемым сопротивлением, выполненные на согласованных полевых транзисторах, истоки которых подключены к инвертирующим входам первого и второго операционных усилителей соответственно, выход первого операционного усилителя -подключен к затворам первого и второго полевых транзисторов, между инвертирующим входом и выходом второго операционного усилителя включен пер" вый масштабный резистор, выход второго операционного усилителя является выходом устройства, неинвертирующий вход второго операционного усилителя подключен к шине нулевого потенциала, второй масштабный резистор, первый вывод которого является входом первого сигнала-сомножителя устройства, о т л и ч а ю щ е е— с я тем, что, с целью упрощения, второй вывод второгомасштабного резистора подключен к неинвертирующему входу первого операционного уси" лителя, сток первого полевого транзистора является входом сигнала-дели-. теля устройства, вход второго полевого транзистора является входом второго сигнала-сомножителя устройства.

1176347

YGÃ-Z G, (2) где Y -"сигнал«сомножитель с вхо1О да 9;

Z - сигнал-делитель с входа 10;

G1 — проводимость первого полевого транзистора 1;

С - проводимость второго масштаб

И ного резистора 7.

Gx Y ХY

U -Х вЂ” -" - — - -А..

Ьых С б Z :Е ° (3)

Для получения произведения двух сигналов со входов 8 и 9 следует подавать на вход )О сигнал фиксированного уровня.

Для получшния частного двух сиг) налов следует сигнал-делитель подать на вход 10, сигнал-делимое— на,вход 8 (или 9), а на вход 9 (или 8) подать сигнал фиксированного уровня.

По сравнению с устройством-прототипом предложенное множительно-делительное устройство характеризуется более простой функциональной схемой.

Gg

U алых С где Х вЂ” сигнал-сомножитель с входа 8;

G - проводимость второго полево2 го транзистора 2; - 35

G " проводимость первого масштаб6 ного резистора 6.

Выходной сигнал первого опера1 ционного усилителя 3 изменяет проводимость согласованных по параметрам. «1

Составитель О. Отраднов

Техред З,Палий Корректор М. Максимишинец

Редактор И. Ковальчук

Заказ 5363/49 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Изобретение относится к электрическим вычислительным устройствам и

° может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является упрощение функциональной схемы.

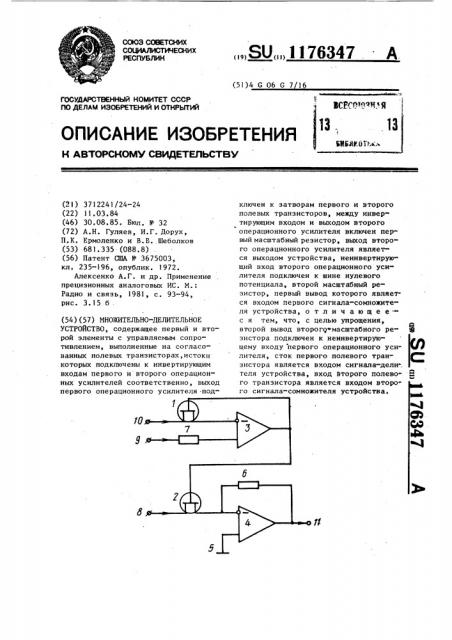

На чертеже изображена функциональ ная схема множительйо-делительного устройства.

Схема содержит первый и второй элементы с управляемым сопротивлением, выполненные на согласованных полевых транзисторах 1 и 2, первый и второй операционные усилители 3 и

4, шину 5 нулевого потенциала, пер вый и второй масштабные резисторы

6 и 7, вход 8 второго сигнала-сомножителя, вход 9 первого сигнала-сомножителя, вход 10 сигнала-делителя, выход 11.

Множительно-делительное устройство работает следующим образом.

Преобразуемые сигналы имеют одинаковую полярность. Второй операцион. ный усилитель 4 совместно с первым масштабным резистором 6 образуют масштабирующий узел. На выходе второго операционного усилителя 4 формируется напряжение первого и второго полевых,транзисторов 1 и 2 до тех пор, пока не уравняются токи через канал первого полевого транзистора 1 и второй масш. табный резистор 7, т.е. до выполнения условия

Учитывая, что первый и второй полевые транзисторы 1 и 2 согласованы по параметрам, т,е. их проводимости равны, то уравнение (1) с учетом уравнения (2) можно записать в виде