Устройство формирования эталонных цифровых сигналов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ФОРМИРОВАНИЯ ЭТАЛОННЫХ ЦИФРОВЫХ СИГНАЛОВ, содержащее последовательно соединенные первьй переключатель тока и первый формирователь уровня, содержащие соответственно первьш и второй источники напряжения, и последовательно соединенные и выполне шые на транзисторах противоположной нолярности второй переключатель тока и второй формирователь уровня, содержащие соответственно третий и четвертый источники напряжений,.первый и второй переключатели тока вьтолнены на первом, втором, третьем и четвертом транзисторах, первый и второй формирователи уровней выполнены на пятом и шестом транзисторах соответственно р-п-р-типа и 1-р-П-типа, эмиттеры пятого транзистора соответственно первого и второго формирователей уровня подсоединены через первый резистор соответственно к второму и четвертому источникам напряжения, третий и четвертьй транзисторы соответственно первого и второго переключателей токов выполнены по схеме с объединенньии эмиттерами и в цепи их коллекторов .включены второй и третий резисторы, база и эмиттер второго транзистора h-p-n- и р-п-р-типа соответственно первого и второго переключателей токов подключены к первым выводам соответственно четвертого и пятого резисторов , базы первых транзисторов первого и второго переключателей токов подключены к первым входным шинам устройства формирования эталонных цифровых сигналов, о т л ичающееся тем, что, с целью расЕйирения функциональных возможностей путем обеспечения работы от i источников сигнала противоположных полярностей, в него введены первый (Л и второй диодные мосты, последовательно соединенные шестой и седьмой резисторы первого и второго переключателей тока, подключенные между эмиттером первого транзистора и вторыми входньп 1и шинами устройства формирования эталонных цифровых сигналов, причем первый транзистор о первого переключателя тока вьтолнен 4 на транзисторе р-п-р-типа, а третийи четвертый транзисторы первого СО переключателя тока выполнены п-р-Птипа , формирователи уровня выполнены по схеме переключателей тока с объединенными эмиттерами, вторые выводы второго и третьего резисторов и соответственно четвертого и пятогорезисторов первого переключателя тока подк.гаочены соответственно к второму источнику напряжения и к первому источнику напряжения, вторые выводы второго и третьего резисторов и соответственно четвертого и пятого резисторов второго переключа

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧ ЕСНИХ

РЕСПУБЛИН (51) 4

ОПИСАНИЕ ИЗОБРЕТ

К ABTGPCHGMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3579839/24-21 (22) 15.04.83 (46) 30.08.85. Бюл. Р 32 (72) А.В. Яковлев и Л.Д. Носов (53) 621.374.38 (088.8) (56) Измерение параметров цифровых интегральных микросхем. Под ред. Д.Ю. Эйдукаса. N.: Радио и связь, 1982, с. 265-266, рис. 6.19.

2. Там же, с. 267-272, рис. 6.20 и рис. 6.21. (54)(57) УСТРОЙСТВО ФОРМИРОВАНИЯ

ЭТАЛОННЫХ ЦИФРОВЫХ СИ HAIIOB, содержащее последовательно соединенные первый переключатель тока и первый формирователь уровня, содержащие соответственно первь|й и второй источники напряжения, и последовательно соединенные и выполненные на транзисторах противоположной полярности второй переключатель тока и второй формирователь уровня, содержащие соответственно третий и четвертый источники напряжений,.первый и второй переключатели тока выполнены на первом, втором, третьеМ и четвертом транзисторах, первый и второй формирователи уровней выполчены на пятом и шестом транзисторах соответственно о -и-Р-типа и A-)-A-типа, эмиттеры пятого транзистора соответственно первого и второго формирователей уровня подсоединены через первый резистор соответственно к второму и четвертому источникам напряжения, третий и четвертый транзисторы соответственно первого и второго переключателей токов выполнены по схеме с объединенными эмиттерами и в цепи их коллекторов

„„Я0„„1176443 А.включены второй и третий резисторы, база и эмиттер второго транзистора й-р-и- и -в- -типа соответственно первого и второго переключателей токов подключены к первым выводам соответственно четвертого и пятого резисторов, базы первых транзисторов первого и второго переключателей токов подключены к первым входным шинам устройства формирования эталонных цифровых сигналов, о т л ич а ю щ е е с я тем, что, с целью расширения функциональных воэможностей путем обеспечения работы от источников сигнала противоположных полярностей, в него введены первый и второй диодные мосты, последовательно соединенные шестой и седьмой резисторы первого и второго переключателей тока, подключенные между эмиттером первого транзистора и вторыми входными шинами устройства формирования эталонных цифровых сигналов, причем первый транзистор первого переключателя тока выполнен на транзисторе р -г1-Р-типа, а третий и четвертый транзисторы первого переключателя тока выполнены и -Р-Итипа, формирователи уровня выполнены и схеме переключателей тока с объединенными эмиттерами, вторые выводы второго и третьего резисторов и соответственно четвертого и пятого. резисторов первого переключателя тока подключены соответственно к второму источнику напряжения и к первому источнику напряжения, вторые ьыводы второго и третьего резисторов и соответственно четвертого и пятого резисторов второго переключа-!

1176443 теля подключены соответственно к четвертому источнику напряжения и к третьему источнику напряжения, коллекторы пятого и шестого транзисторов первого формирователя уровней подключены к точкам соединения анодов первого и второго дисдного мостов, точки соединения катодов которых подключены соответственно к коллекторам пятого и шестого транзисторов второго форми1

Изобретение может быть использо— вано в радиоэлектронной аппаратуре различного назначения, в частности в многоканальной аппаратуре контроля и измерения параметров цифровьгх схем для формирования эталонных цифровых сигналов с заданными уровнями и длительностью фронтов сигналов.

Цель изобретения — расширение функциональных возможностей устройства путем обеспечения работы от источников сигнала противоположных полярностей.

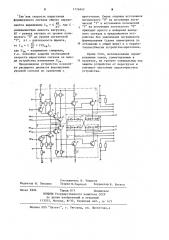

На чертеже нрецставлена принципиальная электрическая схема устройства формирования эталонных цифровых сигналов.

Устройство формирования эталонных цифровых сигналов содержит последовательно соединенные первый переключатель 1 тока и первый формирователь 2 уровня, содержащие соответственно первый и второй источники 3, 4 напряжения, и последовательно соединенные и выполненные на транзисторах противоположной полярности второй переключатель 5 тока и второй формирователь 6 уровня, содержащие соответственно третий и четвертый источники 7,8 напряжений, первый перекпючатель 1 тока выполнен на первом, втором, третьем и четвертом транзисторах

9-12, второй переключатель 5 тока выполнен на транзисторах 13-16, первый и второй формирователи 2, 6 уровней выполнены на пятом и шестом транзисторах 17,18 ссответствен> с <> -1>-Р-гила и соответственно рователя уровней, первые точки соединения анод-катод первого и второго диодного мостов подключены к уровню логического нуля и соответственно к урс>эню логической единицы, вторые точки соединения анодкатод первого и второго диодного мостов соединены между <обой и подключены к выходу vcòðoéñòíà формирования эталонных цифровых снгналов.

19, 20 п -I>-П -типа, эмиттеры пятого транзистора соответственно первого и второго формирователей 2, 6 уровня подсоединены через первый резистор 21 и соответственно резистор

22 к соответствующе< второму и четвертому источникам 4, 8 напряжения, третий и четвертый транзисторы 11, 12 и 15, 16 соответственна

10 первого и второго переключателей

1 и 5 токоь выполнены по схеме с объедине><ными эмиттерами и в цепи их коллекторов включены второй и третий резисторы соответственно 23, 24 и 25, 26, база и эмиттер вторсгс транзистора П вЂ” E>-0- и (> — И- р-типа соответственно первого и второго переключателей 1 и 5 токов под><л>очены к первым выводам соответст20 венно четвертого и пятого резисторов соответственно 27, 28,29, 30 базы первых транзисторов соответственно первого и второго переключателей

1, 5

25 гервым и вторым входами 31, 32, у-стройства формирования эталонных цифрсвых сигня 1св первь<и и Втор си диодные мосты 33 и 34, последовательно соединенные шестой и седьмой резисторы 35, 36 и 37, 38 соотьетственно первого и второго переключателей 1 и 5 тока, подключенные между эмиттером первого транзистора

9 и 13 и вторыми входными шинами

39 40 устройства формирования эталонных цифровых сигнапсв, причем первый транзистор первого перекл>очателя 1 тока выполнен на транзисторе Р— 0-I> †ти, à третий и четв< рпый транзисторы первого пе1>ек.гочаэ àl<8

11!644 3

35 ством которых формируется на выходе

55 тока выполнены П -, -n -тин», формпро— ватели 2 и 6 уровня выполнены по схеме переключателей тока с объединенными эмиттерами, вторые выводы второго и третьего резисторов 23,24 и соответственно четвертого и пятого резисторов 27,28 переключателя 1 тока подключены к второму источнику 4 положительного напряжения и соответственно к первому источнику

3 отрицательного напряжения, вторые выводы второго и третьего резисторов 25, 26 и соответственно четвертого и пятого резисторов 29, 30 второго переключателя 5 тока подключены к четвертому источнику 8 отрицательного напряжения и соответственно к третьему источнику 7 поло— жительпого напряжения, коллекторы пятого и шестого транзисторов 17, 18 первого формирователя 2 уровней

-подключены к точкам соединения анодов первого и второго диодного мостов 33, 34, точки соединения катодов которых подключены соответственно к коллекторам пятого и шестого транзисторов 19, 20 второго формирователя уровней, 6 первые точки соединения анод-катод первого и второго диодного мостов подключены к шине логического нуля 41 и соответственно к .шине логической единицы 42, вторые точки соединения анод-катод первого и второго диодного мостов соединены между собой и подключены к выходу 43 устройства формирования эталонных цифровых сигналов, входы 44, 45, 46, 47 являются дополнительными входами устройства.

Устройство работает следующим образом.

При поданном питании сигнал высокого уровня (логическая "1" ТТЛ уровня) на базе транзистора 9 отключает генераторы токов на транзистора с 9-10 и 13-19, так как переходы база-эмиттер транзисторов

9 и 13 находятся в обратносмещенном состоянии. Все транзиcòîðû устройства закрыты независимо от уровней логических сигналов на информационных входах (базах транзисторов 11, 12, 15, 16) устройства, при этом переходы диодов в мостах 33, 34 смещены в обратном направлении и устройство находится в третьем (отключенном от нагрузки) состоянии. На1О

30 личие сигнала низкого уровня (логический "0" ТТЛ уровня) на базе транзистора 9 включает генераторы токов на транзисторах 9, 10, 13, 14 и с коллекторов транзисторов 10, 14 задаются токи питания переключателей токов на транзисторах 11, 12 и 15,16, состояние устройства и полярность формируемого сигнала определяются в этом случае полярностью сигналов на базах транзисторов 1 1, l5, 12, 16.

При высоком уровне. управляющего сигнала на базах транзисторов 11, 16 и низком уровне управляющего сигнала на базах транзисторов 12, 15 транзисторы 11, 15 включены, в цепи баз транзисторов 17, 20 заданы управляющие токи, практически равные токам питания первых переключателей 1,5 токов. Транзисторы

17, 20 работают при этом как генераторы тока питания диодного моста 33.

Токи, снимаемые с коллекторов транзисторов 17, 20 смещают переходы диодов моста 33 в прямом направлении, подключая источник опорного напряжения логического "0" к нагрузке (выходу устройства).

При низком уровне управляющего сигнала на базах транзисторов 11, 16 и высоком уровне управляющего сигнала на базах транзисторов 10, 12 транзисторы 11, 15 выключены, а транзисторы 12, 16 включены и в цепи баэ транзисторов 17, 20 в диодный мост 33 подаются токи, посредустройства сигнал с заданным опорным уровнем логической "1" (аналогично формированию сигнала с уровнем логического 0").

Особенностью работы устройства является то, что формирование эталонного цифрового сигнала осуществляется номированным током (током заданного значения), отдаваемым в нагрузку. При этом в момент переключения сигналов в нагрузку с диодного моста снимается весь ток а при достижении заданного опорного уровня происходит перераспределение токов, протекающих через диоды моста, и уровень формируемого (U < ) сигнала определяется как сумма падений напряжений на диодах моста U - = U +U

Р

: у П Uon1176443

Составитель В. Чижиков

Редактор М. Бандура Техред М.Пароцай Корректор В. Бутяга

Заказ 6984

Тираж 871 Подписи ое

ВНИИПИ Государственного комитета СССР

IIG e M H3 PeI eHHH H OTKPblTHH

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная 4

n v

Так как скорость нарастания формируемого сигнала обычно опреде4П ляется выражением I С вЂ” где С * н эквивалентная емкость нагрузки, bU " размах сигнала от уровня логического "0" до уровня логической 1, h t — длительность фронта, то Тн = С вЂ” „= f(U<„,), 4П где П ц — напряжение смещения, т.е. возможно задание необходимой скорости нарастания сигнала на выходе устройства изменением U „,.

Предложенное устройство позволяет расширить диапазон формируемых уровней сигнала по сравнению с прототипом. Смена опорных источников логического "0" на источники логической "1" и источников логической

"1" на источники логического "0" приводит просто к инверсии выходного сигнала в предложенном устройстве без увеличения погрешности формирования (схема симметрична по отношению к общей шине) и к неработоспособности устройства-прототипа.

Кроме того, использование нормированных токов, коммутируемых в

15 нагрузку, не требует специальных мер защиты устройства от перегрузок и улучшает частотные характеристики устройства.