Устройство для контроля умножения чисел по модулю @

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ т, содержащее регистры контрольных разрядов множимого и множителя, четыре узла сложения по модулю m, два узла вычитания по модулю in, узел умножения по модулю tn три узла свертки по модулю In, блок сравнения, причем вход первого узла свертки по модулю mобъединен с первым входом первого узла сложения по модулю m и является входом порядка множимого устройства , вход второго узла свертки по модулю т объединен с первым входом второго узла сложения по модулю m и является входом порядка множителя устройства, вторые входы первого и второго узловсложения по модулю гп являются входами мантиссы множимого и мноясителя устройства соответственно , выходы первого и второго узлов сложения по модулю fn соединены соответственно с информационными входами регистра контрольных разрядов множимого и регистра контрольных разрядов множителя, выходы которых соединены с первыми входами первого и второго узлов вычитания по модулю ГП соответственно, выход первого уэла свертки по модулю mсоединен с первым входом третьего узла сложения по модулю m и вторым входом первого узла вычитания по модулю т, выход которого соединен с первым входом узла умножения по модулю Гп, второй вход которого соединен с выходом второго узла вычитания по модулю два, второй вход которого соединен с выходом второго узла свертки по модулю in и вторым входом третьего узла сложения по модулю w, выход т которого соединен с первым входом четвертого узла сложения по модулю с т, второй вход которого соединен с выходом узла умножения по модулю hi, § выход третьего узла свертки по модулю m соединен с первым входом блока сравнения, выход которого является выходом неиспргвности устройства, вход третьего узла свертки по модуч лю .т является входом результата уст ройства, отличающееся тем, что, с целью повышения точности контроля, в него введены сумматор по модулю два, группа сумматоров по модулю два, четвертый узел свертки по модулю fn и третий узел вычитания по модулю m, причем первый и второй входы сумматора по модулю два являются соответственно входами знака множимого и множителя соответственно, вход четвертого узла свертки по модулю пг является входом отбрасываемых разрядов результата устройства, выходы контрольных разрядов четвертого

СОО3 СОВЕТСНИХ

СОЦЮЛИСтИЧКСНИХ

РЕСГ1УБЛИК (19> SU (II) 1 1 (Я)4 G 06 F 11/08 (21) 3716973/24-24 (22) 27.03.84 (46) 07.09.85. Бюл. 11 33 (72) А.В.Дрозд, Е.Л.Полин, В.Л.Панченко, В. А. Минченко и Ю. Г. Клименко (53) 681.3(088.8) (56) Авторское свидетельство СССР

1Ô 411454, кл. G 06 F 11/10, 1970, Авторское свидетельство СССР

У 595737, кл, С 06 F ll/08, 1975. (54)(57) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ щ, содержащее регистры контрольных разрядов множимого и множителя, четыре узла сложения по модулю m, два узла вычитания по модулю tn узел умножения по модулю m три узла свертки по модулю 1н, блок сравнения, причем вход первого узла свертки по модулю

1побъединен с первым входом первого узла сложения по модулю rn и является входом порядка множимого устрой ства, вход второго узла свертки по модулю уп объединен с первым входом второго узла сложения по модулю П1 и является входом порядка множителя устройства, вторые входы первого и второго узлов. сложения по модулю щ являются входами мантиссы множимого и множителя устройства соответственно, выходы первого и второго узлов сложения по модулю Ф соединены соответственно с информационными входами регистра контрольных разрядов множимого и регистра контрольных разрядов множителя, выходы которых соединены с первыми входами первого и второго узлов вычитания по модулю

1П соответственно, выход первого узла свертки по модулю щ соединен с первым входом третьего узла сложения по модулю rnи вторым входом первого узла вычитания по модулю m выход которого соединен с первым входом узла умножения по модулю Ф, второй вход которого соединен с выходом второго узла вычитания по модулю два, второй вход которого соединен с выходом второго узла свертки по модулю 1т и вторым входом третьего узла сложения по модулю щ, выход которого соединен с первым входом четвертого узла сложения по модулю второй вход которого соединен с выходом узла умножения по модулю 1п, выход третьего узла свертки по модулю щ соединен с первым входом блока сравнения, выход которого является ! выходом неисправности устройства, вход третьего узла свертки по модулю .rn является входом результата устройства, отличающееся тем, что, с целью повышения точности контроля, в него введены сумматор по модулю два, группа сумматоров по модулю два, четвертый узел свертки по модулю 1п и третий узел вычитания по модулю 1п, причем первый и второй входы сумматора по модулю два являются соответственно входами знака множимого и множителя соответственно, вход четвертого узла свертки по модулю щ является входом отбрасываемых разрядов результата устройства, выходы контрольных разрядов четвертого

1177814 узла свертки по модулю щ соединены с первыми входами соответствующих сумматоров по модулю два группы, вторые входы которых объединены и соединены с выходом сумматора по модулю,.два,.**ввижды "четвертого узла сложен пс уаффгф ЙМ:оедйнены с первой Ф»- ... ., у Л .*. Ф

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах, Целью изобретения является повышение точности контроля.

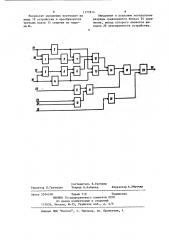

На чертеже приведена структурная схема устройства для контроля умножения по модулю rn.

Устройство содержит первый узел 1 сложения по модулю 1п, второй узел 2 сложения по модулю П1, первый узел

3 свертки по модулю )и, второй узел

4 свертки по модулю щ, регистры .5 и б контрольных разрядов множимого и множителя, первый узел 7 вычитания по модулю rn второй узел 8 вычитания по модулю п1, четвертый узел 9 свертки по модулю е сумматор 10 по модулю два, группу 11 сумматоров по модулю два, узел 12 умножения по модулю два, третий узел 13 сложения по модулю Ф, четвертый узел 14 сложения по модулю Ь, третий узел 15 свертки по модулю rn третий узел 16 вычитания по модулю .th, Bxog 1? nopspzca множимого устройства, вход 18 порядка множителя устройства, вход 19 результата устройства, входы 20 и

21 мантиссы множимого и множителя устройства, вход 22 отбрасываемых

1 зр разрядов результата устройства, входы 23 и 24 знака множимого и множителя, блок 25 сравнения, выход

26 неисправности устройства.

Устройство для контроля умножения чисел по модулю 1п работает следующим образом.

В начальный момент на входы 20 и 21 мантисс множимого и множителя устройства поступают соответственно 4р обратные коды мантиссы множимого и множителя, а на входы 17 и 18 устгруппой входов третьего узла вычитания по модулю rn, вторая группа входов которого соединена с выходами сумматоров по модулю два группы, выход третьего узла вычитания по модулю rh соединен с вторым входом блока сравнения, ройства — обратные коды порядков множимого и множителя.

Первый узел 1 сложения по модулю ъ осуществляет суммирование по модулю кодов мантиссы и порядка множимого, результат записывается на регистр 5 контрольных разрядов множимого.

Второй узел 2 сложения по модулю 11осуществляет суммирование по модулю кодов мантиссы и порядка множителя,результат записываетсяна регистр

6 контрольныхразрядов множителя .

Первый и второй узлы 7 и 8 вычитания по модулю m формируют соответственно контрольные разряды мантисс множимого и множителя с помощью первого и второго узлов 3 и 4 свертки по модулю п.

Контрольные разряды мантисс множителя и множимого перемножаются узлом 12 умножения, формируя контрольные разряды мантиссы результата, Третий узел 13 сложения по модулю Ж формирует контрольные разряды порядка результата.

Сумматор 10 по модулю два формирует код знака результата по кодам знака множимого и множителя, поступающим на входы 23 и 24 устройства.

Четвертый узел 9 свертки по модулю 1 формирует контрольные разряды отбрасываемой части результата, которые поступают на входы сумматоров по модулю два группы 11, где складываются с сигналом с выхода сумматора 10 по модулю два.

Четвертый узел 14 сложения по модулю два и третий узел 16 вычитания по модулю п осуществляют формирование ожидаемых контрольных разрядов результата.

Составитель В.Гречнев

Техред А.Бабинец Корректор А Обручар

Редактор Л. Гратилло

Заказ 5554/48 Тираж 710 Подписное

ВНИИПИ ГосударсТвенного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r Ужгород, ул. Проектная, 4

3 117781

Результат умножения поступает на вход 19 устройства и преобразуется третьим узлом 15 свертки по модулю М.

4 4

Ожидаемые и реальные контрольные разряды сравниваются блоком 25 срав нения, выход которого является выходом 26 неисправности устройства.