Устройство для оценки дисперсии распределения сигнала

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ОЦЕНКИ ДИСПЕРСИИ РАСПРЕДЕЛЕНИЯ СИГНАЛА, содержащее генератор тактовых импульсов, последовательно соединенные блок .пороговых элементов, вход которого является входе устройства, блок логической обработки и блок элементов И, регулятор ширины зоны уровня сигнала , выход которого является выходом устройства, отличающееся тем, что, с целью повышения точности, в него введены последовательно соединенные решакщий блок и блок вычитания, объединенные входы которых соединены с входом блока пороговых элементов, коммутатор и блок усреднения, выполненный в виде последовательно соединенных квадратора ,вход которого соединенс выходом коммутатора, сумматора, второй вход которого соединен с выходом генератора тактовых импульсов, дополнительного блока вычитания, интегратора и блока памяти, второй вход и выход которого соединены соответственно с выходом генератора тактовых импульсов и вторым входом дополнительного блока вычитания, выход блока памяти подключен к входу регу (Л лятора ширины зоны уровня сигнала, выход генератора тактовых импульсовк управлякщему входу коммутатора, информационный вход которого соединен с выходом блока элементов И, второй вход которого соединен с выходом блока вычитания. ч со

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (!9) (! !) (5!)4 Н 04 В 1 10 (21) 3746246/24-09 (22) 28.04.84 (46) 07.09.85. Бюл. Ф 33 (72) А.М.Боград, Б.С.Данилов, Л.Г.Израильсон и А.В.Реймерс (53) 621.395.62 (088.8) (56) Патент США И 3633108, кл. Н 04 В l/10, 1972.

Авторское свидетельство СССР

Ф 543159, кл. Н 04 В 1/10, 1974. (54)(57) УСТРОЙСТВО ДЛЯ ОЦЕНКИ ДИСПЕРСИИ РАСПРЕДЕЛЕНИЯ СИГНАЛА, содержащее генератор тактовых импульсов, последовательно соединенные блок .пороговых элементов, вход которого является входом устройства, блок логической обработки и блок элементов

И, регулятор ширины зоны уровня сигнала, выход которого является выходом устройства, о т л и ч а ю щ е— е с я тем, что, с целью повышения точности, в него введены последова-, тельно соединенные решающий блок и блок вычитания, обьединениые входы которых соединены с входом блока пороговых элементов, коммутатор и блок усреднения, выполненный в виде последовательно соединенных квадратора, вход которого соединен с выходом коммутатора, сумматора, второй вход которого соединен с выходом генератора тактовых импульсов, дополнительного блока вычитания, интегратора и блока памяти, второй вход и выход которого соединены соответственно с выходом генератора тактовых импульсов и вторым входом дополнительного блока вычитания, выход блока памяти подключен к входу регулятора ширины зоны уровня сигнала, выход генератора тактовых импульсовк управлянш(ему входу коммутатора, информационный вход которого соединен с выходом блока элементов И, ВТо рой вход которого соединен с выходом блока вычитания.

1177913

Изобретение относится к технике электросвязи и может использоваться ° для оценки качества сигнала дис,кретной информации.

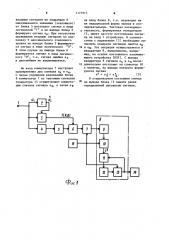

Цель изобретения — повьппение точности, На фиг.l представлена структурная электрическая схема предложенного устройства; на фиг.2 — вариант выполнения решающего блока; на фиг.3 — вариант выполнения блока пороговых элементов; на фиг.4 — вариант выполнения блока логической обработки; на фиг.5 — вариант выполнения блока элеметов И. 15

Устройство для оценки дисперсии распределения сигнала содержит вход

1, решающий блок 2, блок 3 вычитания, блок 4 пороговых элементов, блок 5 логической обработки, блок 6 элемен- 0 тов И, коммутатор 7, блок 8 усреднения, состоящий из квадратора 9, сумматора 10, дополнительного блока ll вьгчитания, интегратора 12 и блока 13 памяти, регулятор 14 ширинызЬньг уровня сигнала, генератор 15 тактовых им- . пульсов.

Решающий блок (фиг.2) содержит блок

16 выделения "1", блок 1? выделения

"3". и элемент ИЛИ 18. 30

Блок пороговых элементов (фиг.3) . содержит четыре пороговых элемента

19-22, Блок логической обработки (фиг.4) содержит два элемента НЕ 23 и 24.и два элемента ИЛИ 25 и 26.

Блок элементов И (фиг.5) содержит два элемента И 27 и 28.

Устройство работает следующим образом. 40

Предложенное устройство осуществляет оценку качества многопозиционного сигнала, принимаемого посредством двух демодуляторов, осуществляющих демодуляцию с помощью двух ортогональ- 45 ных когерентных колебаний 1В и Я).

В качестве критерия оценки 9 используется величина дисперсии ошибки Р (е):

В = D (е) = M(e ) — M (е), (1) где M — - математическое движение; 50 е — вектор ошибки;

D — - дисперсия.

° Поскольку М (е) = О, так как оценка является несмещенной, то выражение (1) преобразуется в

О= D (е) = М (е"), (2)

Учитывая, что каждая из проекций е1 и е вектора сигнала ошибки е на ко4 герентные колебания R и Q, являются независимыми случайными величинами, можно записать:

8 =М(е ")=М(е„)+М(е )=М(е еа). (3)

Величина @ может быть вычислена на основе рекуррентного алгоритма:

8„„=8.+ (e„- "„„), (4) где О1 — коэффициент интеграции;

1 еп.11= e Q 1-1 ад+,, а „,1 — величины принимаемо — .

ro и эталонного значений вектора сигнала.

Многоуровневый многопозиционный сигнал, оцениваемый по двум ортогональным подканалам Я и Я, поступает на объединенные входы решающего блока

2, блока 3 вычитания и блока 4 пороговых элементов, соединенные с входом 1 устройства. С помощью решающего блока 2 и блока 3 вычитания определяется величина отклонения сигнала от эталонных значений в каждом из подканалов — сигналы ошибки е и

g е . С целью повышения точности оценки в предложенном устройстве используются сигналы ошибки только в том случае, когда принимаемый сигнал ripeвышает максимальный эталонный уровень.

Для ограничения зоны использования ошибок в предложенном устройстве служат три блока: блок 4 пороговьгх элементов, блок 5 логической обработки и блок 6 элементов И (фиг.1), Блок 4 пороговых элементов фиксирует превьппение сигналом максимального по. абсолютной величине эталонного уровня (положительного или отрица" тельного)для каждого подканала. Сигналы, свидетельствующие о превьппении, с выхода блока 4 пороговых элементов поступают на вход блока 5 логической обработки. На выходе блока 5 формируются объединенные сигналы (для каждого подканала), которые затем поступают на входы блока 6 элементов И.

На другие два входа блока 6 элементов И поступают сигналы е и eq от блока 3 вычитания.

Если входной сигнал по модулю меньше максимального эталонного уровня, сигналы ошибок на выходе блока 6 элементов И отсутствуют, т.е. на вьгходе блока 6 формируются сигналы, соответствующие логическо-. му "0". Далее сигналы е и е поступают на коммутатор 7, который посредством тактовых серий, выраба-! з 11779 тываемых генератором 15, разделяет эти сигналы по времени. Для повышения тоАности оценки качества сигнала служит блок 8 усреднения, вычисляющий дисперсию ошибок в соответствии с выражениями (3) и (4). Реализация указанного алгоритма вычисления дисперсии распределения сигнала в блоке 8 осуществляется квадратором 9, сумматором 10, дополнитель- 10 ным блоком 11 вычитания, интегратором 12 и блоком 13 памяти. Сигнал с выхода блока 8 усреднения поступает на вход регулятора 14,. служащего для отображения визуального, 15 качества анализируемого сигнала.

Реализация решающего блока 2 (фиг.2) зависит от типа анализируемых сигналов. В задачу решающего блока 2 входит выделение- соответст- щ0 вия анализируемого сигнала а„ эталонному значению 4 . Под соответствием понимается близость.(в смысле расстояния) между а и . В данном случае a„ R u Q,,25 могут принимать значения + 1 и + 3..

Из соображений минимума расстояния до эталона можно составить следующие выражения соответствия

1а1 < 2 ь а; (= 1

2 < 1а„1 =Ф1а = 3, . (5) причем: sgn CL sgn at..

Выполнение логических условий согласно первому и второму уравнению выражения (5) осуществляется в блоке

16 выделения "1" и в блоке 17 выделения "3" соответственно, входящих в состав решающего блока 2 (фиг ° 2).

Традиционно значение символа а„ представляется двоичным числом моду- 40 ля со знаком. Тогда уравнения выражения (5) можно переписать следующим образом:

1а = 1+a<. a = 1 а"„= З=Ь а„+ а = 1. (6) 45

Таким образом, реализация блоков

16 и 17 может быть выполнена, используя выражения (5) или (6). Причем в выражении (6) приняты следующие обозначения: а> и а — первый (старший) 50

- и второй двоичный разряды числа а; а — инверсия двоичного числа а1..

Выделенное эталонное кодовое число а „ получается как объединение на элементе ИЛИ 18 всех возможных сигна-55 лов. Следует иметь в виду, что на . фиг.2 представлен пример реализации формирования сигнала а только по

1 1 4 одному подканалу. При формировании сигнала а по двум подканалам число блоков 16 и 17 и элемента ИЛИ 18 удваивается.

Блок 4 пороговых элементов состоит из четырех пороговых элементов: первого 19 и второго 20, анализирующих входной сигнал по подканалу R, и третьего 21 и четвертого 22, анализирующих входной сигнал по подканалу Q (фиг.3). Каждый из пороговых элементов фиксирует превышение входным сигналом максимального эталонного значения. При этом пороговые элементы 19 и 21 фиксируют превьппение положительным входным сигналом, а пороговые элементы 20 и 22 — отрицательным. Каждый из пороговых элементов

19-22 может быть реализован на основании выражения: a< + а ° а„° а = 1 (7)

Блок 5 логической обработки осуществляет. объединение сигналов (фиг ° 4), отображающих превышение входным сигналом положительного и отрицательного максимального эталонного значений в каждом из подканалов, элемент НЕ

23 и элемент HJIH 25 объединяют сигналы превьппения в подканале R, элемент

НЕ 24 и элемент ИЛИ 26 — в подканале

q (фиг.4). Таким образом, на выходе блока 5 раздельно, но одновременно, для каждого подканала формируется сигнал, например, в виде логической

"1" только в том случае, когда модуль величины входного сигнала превышает максимальный эталонный уровень.

Каждый из элементов И 27 и 28 блока 6 (фиг.5) при дискретной реализации устройства состоит из набора элементов И, число которых равно числу разрядов в кодовом числе еп или е@. При этом сигналы е и е, формируются в блоке 6 в соответствии с выражением и л еу, = a —.а

n"

eQ= а " — а (8)

Рассмотрим функционирование, на-. пример, элемента И 27 для подканала

R (функционирование элемента И 28 для подканала Я осуществляется ана-. логично). На вход каждого из элементов И поступает сигнал соответствующего разряда кодового числа е .

На объединенные вторые входы каждого элемента И поступает управляющий сигнал от блока 5, При превьппении

1177913 входным сигналом по подканалу R максимального значения (эталонного) от блока 5 поступает сигнал в виде логической "1" и на выходе блока 6 формирует сигнал е . При отсутствии превышения входным сигналом по подканалу R максимального эталонного уровня на выходе блока 5 формируется сигнал в виде логического "0".

В этом случае на выходе блока 6 формируется сигнал в виде логического "0", т.е. сигнал ошибки е в дальнейшем не анализируется.

На вход коммутатора 7 поступают одновременно два сигнала е и е .

С целью упрощения реализации блока

8 коммутатор 7 по тактовым сигналам генератора 15 осуществляет коммутацию сначала сигнала е, а затем eg на вход блока 8, т.е. переводит их из параллельной формы записи в последовательную. Тактовая последовательность, формируемая генератором

15, имеет частоту поступления сигнала на вход 1 устройства. В соответствии с выражением (3) необходимо вычислить квадраты сигналов ошибки е

1Î и е . Эта операция осуществляется в квадраторе 9, выполненном, например, на основе постоянного запоминающего устройства (ПЗУ). С выхода квадратора 9 сигналы е и е> после15 довательно поступают на сумматор 10 с памятью, на выходе которого формируется сигнал е = е"-+ е . (9)

В стационарном состоянии сигнал на выходе блока 13 памяти равен

:определяемой дисперсии сигнала.

1 177913

1177913

mumop 7

Фиг.5

Составитель E. Голуб

Техред М.Гергель Корректор М.Самборская

Редактор А.Шандор е

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 5562/53 Тираж 659 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5