Устройство для измерения коэффициента ошибок в цифровых системах передачи

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ОШИБОК В ЦИФРОВЫХ СИСТЕМАХ ПЕРЕДАЧИ, содержащее на передающей стороне генератор контрольно-испытательного сигнала, выход которого является входом цифрового линейного тракта, а на приемной стороне - последовательно соединенные выделитель тактовой частоты, блок управления и счетчик общего числа ошибок, последовательно соединенные регистр сдвига, линию задержки и распределитель, последовательно соединенные дешифратор, входы которого соединены с соответствующими выходами регистра сдвига и распределителя, и эталонный генератор, регулируемую линию задержки, второй выход выделителя тактовой частоты подключен к первому входу регистра сдвига и к второму входу распределителя, второй вход регистра сдвига и вход выделителя тактовой частоты объединены с выходом цифрового линейного тракта, отличающееся тем, что, с целью повышения точности, в него введены формирователь сигнала ошибки , три счетчика, три элемента запрета, три элемента задержки и два элемента совпадения , выход формирователя сигнала ошибки подключен к входу первого элемента задержки , выход которого подключен к первому входу первого элемента запрета, второй вход и выход которого соединены соответственно с выходом формирователя сигнала ошибки и первым входом первого счетчика , выход первого элемента запрета подключен к объединенным первому входу второго элемента запрета и входу второго элемента задержки, выход которого подключен к первому входу первого элемента совпадения , выход которого подключен к первым входам второго счетчика, третьего элемента запрета и входу третьего элемента задержки , выход которого подключен к первому входу второго элемента совпадения, выход и второй вход которого соединены соI ответственно с первым входом третьего счетчика и выходом третьего элемента запрета, сл второй вход которого соединен с вторым входом первого элемента совпадения и выходом второго элемента запрета, второй вход которого соединен с выходом формирователя сигнала ошибки, второй выход блока управления подключен к вторым входам первого , второго и третьего счетчиков, выход эталонного генератора подключен к входу регулируемой линии задержки, выход которой подключен к первому входу формирова ;о ьо теля сигнала ощибки, второй вход которого соединен с третьим выходом выделителя тактовой частоты, третий вход формирователя сигнала ощибки объединен с выходом цифрового линейного тракта, а выход формирователя сигнала ошибки подключен к второму входу счетчика общего числа ошибок .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ з,„„ 1

ОПИСАНИЕ ИЗОБРЕТЕНИ -...,.,::; 9

Н ABTOPGHOMY СВИДЕТЕЛЬСТВУ (21) 3715359/24-09 (22) 10.01.84 (46) 07.09.85. Бюл. № 33 (72) С. С. Литвак (53) 621.391. 154 (088.8) (56) Патент Франции № 2185901, кл. Е 04В1/00, 1977.

Авторское свидетельство СССР № 1020998, кл. Н 04 В 3/46, 1981.

Я

М 3

CO

Ю

С0 (54) (57) УСТРОИСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ОШИБОК В ЦИФPOBbIX СИСТЕМАХ ПЕРЕДАЧИ, содержащее на передающей стороне генератор контрольно-испытательного сигнала, выход которого является входом цифрового линейного тракта, а на приемной стороне — последовательно соединенные выделитель тактовой частоты, блок управления и счетчик общего числа ошибок, последовательно соединенные регистр сдвига, линию задержки и распределитель, последовательно соединенные дешифратор, входы которого соединены с соответствующими выходами регистра сдвига и распределителя, и эталонный генератор, регулируемую линию задержки, второй выход выделителя тактовой частоты подключен к первому входу регистра сдвига и к второму входу распределителя, второй вход регистра сдвига и вход выделителя тактовой частоты объединены с выходом цифрового линейного тракта, отличающееся тем, что, с целью повышения точности, в него введены формирователь сигнала ошибки, три счетчика, три элемента запрета, три элемента задержки и два элемента совпадения, выход формирователя сигнала ошибÄÄSUÄÄ 1177920 А ки подключен к входу первого элемента задержки, выход которого подключен к первому входу первого элемента запрета, второй вход и выход которого соединены соответственно с выходом формирователя сигнала ошибки и первым входом первого счетчика, выход первого элемента запрета подключен к объединенным первому входу второго элемента запрета и входу второго элемента задержки, выход которого подключен к первому входу первого элемента совпадения, выход которого подключен к первым входам второго счетчика, третьего элемента запрета и входу третьего элемента задержки, выход которого подключен к первому входу второго элемента совпадения, выход и второй вход которого соединены соответственно с первым входом третьего счетчика и выходом третьего элемента запрета, второй вход которого соединен с вторым входом первого элемента совпадения и выходом второго элемента запрета, второй вход которого соединен с выходом формирователя сигнала ошибки, второй выход блока управления подключен к вторым входам первого, второго и третьего счетчиков, выход эталонного генератора подключен к входу регулируемой линии задержки, выход которой подключен к первому входу формирователя сигнала ошибки, второй вход которого соединен с третьим выходом выделителя тактовой частоты, третий вход формирователя сигнала ошибки объединен с выходом цифрового линейного тракта, а выход формирователя сигнала ошибки подключен к второму входу счетчика общего числа ошибок.

1177920

Изобретение относится к радиотехнике и может использоваться в системах многоканального уплотнения с импульсно-кодовой модуляцией.

Цель изобретения — повышение точности.

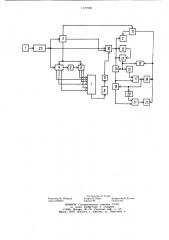

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство для измерения коэффициента ошибок в цифровых системах передачи содержит на передающей стороне генератор 1 контрольно-испытательного сигнала, на приемной стороне — счетчик 2 общего числа ошибок, выделитель 3 тактовой частоты, регистр 4 сдвига, линию 5 задержки, распределитель 6, дешифратор 7, эталонный генератор 8, регулируемую линию 9 задержки, формирователь 10 сигналов ошибки, блок 11 управления, первый элемент 12 задержки, первый 13 и второй 14 элементы запрета, второй элемент 15 задержки, первый счетчик 16, первый элемент 17 совпадения, второй счетчик 18, третий элемент 19 запрета, третий элемент 20 задержки, второй элемент 21 совпадения, третий счетчик 22, причем передающая и приемная стороны соединены цифровым линейным трактом 23.

Устройство работает следующим образом.

Испытательный цифровой сигнал с выхода генератора 1 подается на вход цифрового линейного тракта 23, с выхода которого поступает на третий вход формирователя 10 сигналов ошибки. На второй вход формирователя 10 сигналов ошибки подается периодическая последовательность импульсов, совпадающих по времени с символами отдельных разрядов кодовых комбинаций контрольно-цифрового сигнала.

На выходе формирователя 10 сигналов ошибки формируются сигналы ошибок, которые подсчитываются счетчиком 2 общего числа ошибок и поступают на выход устройства. Импульсы ошибок поступают на вход первого элемента 13 запрета, на второй вход которого сигнал поступает через первый элемент 12 задержки, осуществляющий задержку на один такт. На вход первого счетчика 16 поступают одиночные ошибки и первые импульсы смежных ошибок. На запрещающий вход второго элемента 14 запрета поступают импульсы с выхода формирователя 10 сигналов ошибки и выхода первого элемента 13 запрета. Поэтому на выход устройства не пропускаются одиночные ошибки, длина смежных ошибок уменьшается на один тактовый интервал. С выхода первого элемента 13 запрета импульсы ошибок подаются на вход второго элемента 15 задержки и первый элемент 17 совпадения, к второму входу которого подводятся импульсы одиночных ошибок и первые импульсы смежных ошибок, задержанные на один тактовый интервал во втором элементе 15 задержки. Поэтому на вход второго счетчика 18 пропускаются только сдвоенные смежные ошибки, когда они существуют. Аналогично работают третий элемент 19 запрета и третий элемент 20 задержки. Третий счетчик 22 служит для регистрации третьих импульсов смежных ошибок, и т.д. Результаты, 10 зафиксированные в третьем счетчике 22, представляют собой статистический ряд накопленных частот распределения длины смежных ошибок.

Формирование эталонных периодических импульсных последовательностей, синхронных и синфазных с контрольным цифровым сигналом на втором входе формирователя 10 сигналов ошибки производится непосредственно из контрольного цифрового сигнала, который представляет собой периодическую

20 последовательность к-разрядных кодовых комбинаций, следующих с частотой fò/2», (1 — значения тактовой частоты контрольного цифрового сигнала). Для этого сигнала с выхода цифрового линейного тракта 23 поступает на прямой вход регистра 4 сдвига. который через линию 5 задержки сдвигает контрольный цифровой сигнал на интервал времени пТ (на длительность п-разрядной кодовой комбинации, Т вЂ” длительность тактового интервала сигнала с тактовой часто30 тон 4)

В результате кодовые символы на соответствующих разрядных выходах регистра 4 сдвига и распределителя 6 должны совпадать (в случае отсутствия ошибок). В случае совпадения соответствующих символов, M на выходе дешифратора 7 формируется периодическая импульсная последовательность с частотой f /2 „Ïoñëåäóþùåå формирование периодической импульсной последовательности с частотой 1 /П производится с

4О помощью синхрозируемого по фазе эталонного генератора 8. Эти последовательности по временному положению соответствуют символам первого разряда и-разрядных кодовых комбинаций.

С помощью регулируемой линии 9 за4 держки сигнал поступает на второй вход формирователя 10 сигналов ошибки. Применение синхронизируемого по фазе эталонного генератора 8 позволяет производить формирование синхронной и синфазной эталонной последовательности импульсов с час о тотой f /н даже при возникновении ошибок символов в соседних кодовых комбинациях контрольного цифрового сигнала. Выделитель 3 тактовой частоты осуществляет выделение из входного сигнала тактовой частоты и управляет работой соответствующих элементов.

1177920 Составитель Е. Голуб

Редактор Ar. Шандор Техред И. Верес Корректор В. Бутяга

Заказ 5563/54 Тираж 659 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4