Устройство для выбора и переадресации каналов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫБОРА И ПЕРЕАДРЕСАЦИИ КАНАЛОВ, содержащее блок приема информации и блок оперативной паГШти, первый выход которого соединен с входами блока вьщеления управлякнцих сигналов и блока вьщеления разрядов поля маски, выход которого .подключен к вкоду последовательно соединенньк счетчика количества единиц и сумматора, второй вход которого соединен с вторым выходом блока оперативной памяти, о т л ичающееся , тем, что, с целью упрощения устройства путем сокращения объема оперативной памяти,в него введены пер вый;, второй и третий коммутаторы , первые информационные входы которых соединены соответственно с выходом сумматора, первым и вторым выходами блока приема информации , третий выход которого под- , ключен к второму информационному входу второго коммутатора, выход которого.соединен с вторыми входами блока выделения разрядов поля маски и блока вьщеления управляющих-сигналов , выход которого соединен с управляющими входами первого, второго и третьего коммутаторов, выход которого соединен с адресным входом блока оперативной памяти, а второй информационный вход третьего комму татора подключен к первому выходу пёр:вого коммутатора, второй-выххэд которого является выходом устройства.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51)4 Н 04. 9 14

Ь

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /

И ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР пО делАм изОБРетений и ОтнРытий (21) 3706514/24-09 (22) 01.03.84 ,(46) 07.09.85. Бюл. ¹ 33 (72) Г.Г.Григоренко, Е.В.Артемова и Ю.А.Захаров (53) 621.382.23(088.8) (56) Авторское свидетельство СССР № .836820, кл. Н 04 Q 9/ !4, 1977.

Авторское свидетельство СССР № 562952, кл. Н 04 О 9/14, 1975. (54) (57) УСТРОЙСТВО ДЛЯ ВЫБОРА И

ПЕРЕАДРЕСАЦИИ КАНАЛОВ, содержащее блок приема информации и блок оперативной памяти, первый выход которого соединен с входами блока выделения управляющих сигналов и блока выделения разрядов поля маски, выход которого .подключен к входу последовательно соединенньи счетчика количества единиц и сумматора, второй вход которого соединен с вторым выходом блока оперативной памяти, о т л и„„SU„„1 3 7795 A чающееся,тем, что, сцелью упрощения устройства путем сокращения объема оперативной памяти,в него введены первый, второй и третий коммутаторы, первые информационные входы которых соединены соответственно с выходом сумматора, первым и вторым выходами блока приема информации, третий выход которого под-, ключен к второму информационному входу второго коммутатора, выход которого соединен с вторыми входами блока выделения разрядов поля маски и блока выделения управляющих:сигналов, выход. которого соединен с управляющими входами первого, второго и третьего кою утаторов, выход которого соединен с адресным входом блока оперативной памяти, а второй информационный вход третьего коммутатора подключен к первому выходу пер:вого коммутатора, второй. выход которого является выходом устройства.

1 11779

Изобретение относится к области обработки измерительной информации и может быть использовано для ввода измерительной .информации в системы обработки данных и системы регистрации измерительной информации.

Целью изобретения является упрощение устройства путем сокращения обьема onеративной памяти.

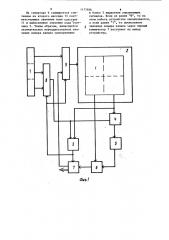

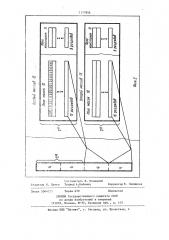

На фиг. 1 приведена функциональ- 10 ная схема устройства для выбора и переадресации каналов; на фиг. 2— схема распределения информации блока оперативной памяти.

Устройство содержит (фиг. 1) !5 блок 1 приема информации, блок 2 оперативной памяти, блок 3 вьщеления управляющих сигналов, блок 4 выделения разрядов поля маски, счетчик 5 количества единиц, сумматор б,первый 2О коммутатор I7, второй коммутатор S u третий коммутатор 9.

Блок 2 оперативной памяти (фиг. 2) включает в себя поле масок 10, поле констант 11, первый массив 12 и вто- 25 рой массив 13. Устройство для выбора и переадресации каналов работает следующим образом.

Перед началом работыв блок2 опе— ративной памяти заносятся исходные данные поля маски 10 и поля констант 11, Каждый разряд поля маски 10 первого массива 12 соответствует группе номеров каналов с одинаковыми старшими разрядами и заполняется "1", если хотя бы один из каналов данной группы подлежит выбору. Каждый раз40 ряд поля маски 10 второго массива 13 соответствует определенному исходному номеру (адресу) канала. Наличие "1" в соответствующем разряде означает, что канал с данным номером подлежит

45 выбору и переадресации. В поле констант 11 заносится константа количества "1", содержащихся в поле маски 10 всех слов, адреса которых меньше адреса данного слова.

Вычисление нового адреса канала производится за два такта.

В первом такте при поступлении на вход устройства кода номера канала осушествляется запоминание этого адре- 5 са в блоке 1 приема информации. Одновременно импульс сопровождения информации инициирует обращение к первому

5б 2 массиву 12 блока 2 оперативной памяти.

В результате обращения из первого массива 12 считывается соответствующее данному адресу слово поля маски

10 и поля констант 11.

Информация поля маски 10 поступает в блок 4 выделения разрядов поля маски, в этот же блок из блока 1 приема информации через второй коммутатор 8 поступает группа разрядов входной информации, определяющая номер разряда поля маски 10.. Блок 4 вьщеляет часть слова слева от выбираемого разряда.

Счетчик 5 количества единиц формирует двоичный код, соответствующий . количеству единиц в выделенной части считанного слова. Данный двоичный код поступает на вход сумматора б, на второй вход которого из блока 2 оперативной памяти поступает значение поля константы 11 считанного слова.

Полученная сумма будет представлять собой адрес во втором массиве 13 блока 2 оперативной памяти. Одновременно в блоке 3 анализируется значение вьделенного разряда. Если выделенный разряд равен "0", то группа канапов с.таким номером не подлежит выбору и все блоки устройства приводятся в исходное состояние.

Если выделенный разряд равен "1", то вырабатывается управляющий сигнал для первого 7, второго 8 и третьего 9 коммутаторов, и устройство переходит ко второму такту работы.

Во втором такте вычисленное сумматором б значение кода через первый коммутатор 7 поступает на второй вход третьего коммутатора 9, который формирует адрес во втором массиве 13 блока 2 оперативной памяти.

Разряды поля маски 10, считанного из второго массива 13 поступают в блок 4, на в-.îðîé вход которого поступзет с блока приема информации через второй коммутатор 8 вторая группа разрядов, определяющая номер разряда поля маски 10 во втором массиве 13 блок 2 оперативной памяти.

В блоке 4 производится выделение части слова слева от вьщеленного раз ряда. Счетчик 5 количества единиц суммирует количество единиц в вьщеленной части слова. з 1

На сумматоре 6 суммируется считанное из второго массива 13 соответствующее значение поля констант

11 и вычисленное значение, кода счетчика 5. Таким образом, вычисляется окончательное переадресованное значение номера канала одновременно

177956 4 в блоке 3 выделения управляющих сигналов. Если он равен "0", то на этом работа устройства заканчивается, а если равен "1", го вычисленное значение номера канала через первый коммутатор 7 поступает на выход устройства.

1177956

Заказ 5564/55

Подписное

Тираж 659

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель В. Паницкий

Редактор В. Данко Техред A.Áàáèíåö Корректор В. Синицкая