Устройство для сопряжения аналого-цифрового преобразователя с цифровой вычислительной машиной

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 G 06 F 3 00

ОГ1ИСАНИЕ ИЗОБРЕТЕНИЯ

v фя1

К ABTOPCHOlVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3659435/24-24 (22) 05.11.83 (46) 15.09.85. Бюл. N 34 (72) Ф. Н. Березин, В. А. Кисурин и I . Г. Офенгенден (53) 681.3 (088.8) (56) Авторское свидетельство. СССР

Р 377759, кл. G 06 F 3/00, 1970.

Авторское свидетельство СССР N 1094038, кл. G 06 F 3/00, 17.01.83. (54(57) 1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

АНАЛОГΠ— ЦИФРОВОГО ПРЕОБРАЗОВАТЕЛЯ

С ЦИФРОВОЙ ВЬ1ЧИСЛИТЕЛЬНОЙ МАШИНОЙ, содержащее промежуточный регистр, вход которого является информационным входом устройства, блок ввода внешних параметров, информационный вход которого является входом задания внешних параметров устройства, буферную память, регистр слова состояния и вспомогательную память, входы-выходы которых образуют вход-выход устройства, сумматор, память микрокоманд, первый и второй адресные регистры и тактовый генератор, вход пуска которого является входом сигнала Готовность" устройства, а выход соединен с синхровходом памяти микрокоманд, адресный вход которой соединен с выходом первого адресного регистра, первый, второй, третий и четвертый выходы памяти микрокоманд соединены соответственно с управляющим входом первого адресного регистра, входом модификации страницы второго адресного регистра, управляющими входами буферной памяти и регистра слова состояния, первый, второй, третий, четвертый и пятый разрядные выходы которого соединены соответственно с входом управления чтением буферной памяти, базовым входом первого адресного регистра, управляющим входом второго адресного регистра, входами разрешения тактового генератора и первого адресного регистра, соединенных с выходом сигнала "Разрешение" устройства и с управляюшим входом блока ввода внешних параметров, выход которого подключен к вхо- ду модификации второго адресного регистра, адресный вход вспомогательной памяти соединен с выходом второго адресного регистра, выход сумматора соединен с информационным входом буферной памяти, управляющий выход которой соединен с информационным входом регистра слова состояния, о т л и ч а ю ш е е с я тем, что, с целью расширения класса решаемых задач . устройства за счет обеспечения .возможности отбора событий, удовлетворяюших одному. из многих условий, эа один такт работы, в него введен блок фиксации совпадений, причем вход-выход блока фиксации совпадений является входом-выходом корреляции устрой ства, а информационный вход соединен с выходом вспомогательной памяти, информационный выход — с первым входом сумматора, второй вход которого соединен с информационным входом второго адресного регистра и. с выходом промежуточного регистра, управляющий вход блока фиксации совпа. дений соединен с дополнительным разрядным выходом регистра слова состояния, а управляющий выход соединен с входом модификации первого адресного регистра.

2. Устройство по п. 1, о т л и ч а юш е е с я тем, что, блок фиксации совпадений содержит в каждом разряде элемент

ИЛИ, переключатель и согласующий резистор, причем выход элемента ИЛИ является управляюшим выходом блока и соединен через переключатель с входом-выходом блока, а через согласуюший резистор — с шиной источника питания, положительной полярности, (ll79308 динен с информационным входом и информационным выходом блока.

Изобретение относится к области вычислительной техники, в частности к средствам ввода измерительной информации в цифровые вычислительные машины (ЦВМ) и может бгчть использовано в системах автоматизации ядерно-физических и иных экспериментальньrx научных исследований, а также промышленных испытаний.

Цель изобретения — расширение класса решаемых задач за счет обеспечения возмож- 10. ности отбора событий, удовлетворяюших одному иэ многих условий, за один такт работы.

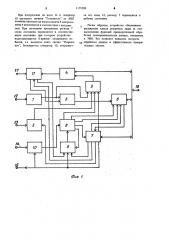

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — формат команд обработ- 15 ки событий, размещение программ отбора . информации и размещение микрокоманд в ячейках -памяти микрокоманд, на фиг. 3 пример реализации одного разряда блока сравнения; на фиг. 4 — блок-схема алгорит- 2р ма работы устройства под управлением ЦВМ; на фиг. 5 — временная диаграмма цикла работы устройства по приему, обработке и записи входящих событий в буферную память.

Устройство (фиг. 1) содержит промежу- 25

I точный регистр 1, блок 2 ввода внешних парамстров, сумматор 3,. вспомогательную память 4, первый адресный регистр 5, буферную память 6, регистр 7 слова состояния, память 8 микрокоманд, второй адресный ре- 30 гистр 9, тактовый генератор 10, . блок 11 совпадений, информационный вход 12 устройства, вход 13 задания внешних параметров. устройства, вход 14 сигнала Готовность" устройства, выход 15 сигнала "Разрешение" устройства, входы-выходы 16 устройства, 35 связывающие устройство с ЦВМ; вход-выход

17 корреляции устройства, связывающий его с другими такими же у.тройствами для совместной работы.

Блок l l совпадения содержит (фиг. 2) в каждом разряде переключатель 17, элемент

ИЛИ 18, соединенный через согласуюший резистор 19 с шиной 20 источника питания положительной полярности.

Устройство работает следуюшим образом.

Иэ АЦП (не показан) код события записывается в промежуточный регистр 1. и далее первый вход элемента ИЛИ является управляющим входом блока, а второй вход соев буферную память 6, где накапливается массив измеренных данных. На втором этапе осуществляется отбор событий, "представляющих интерес". Для этого предусмотрена вспомога- тельная память 4, емкость которой соответствует числу возможных значений кодов событий. Код события используется в качестве основной части адреса вспомогательной памяти 4, а в ячейках, соответствуюших каждому адресу, предварительно с помощью ЦВМ записываются признаки "полезности" события, например "1" в ячейке фиксируют, что событие "представляет интерес", а "О" — "не представляет".

Для регистрации многомерных событий с помощью нескольких АЦП, каждый из которых связан со своим устройством, предусмотрен блок 11, который осуществляет сравнение признаков полезности, вырабатываемых вспомогательной памятью 4 каждого устройства и, если они совпадают, вырабатывает. общий сигнал для всех блоков, В качестве памяти 8 микрокоманд используется постоянная память, так как для конкретной экспериментальной системы набор программ обработки обычно неизменен, в качестве вспомогательной памяти оперативная память, поскольку в ходе каждого эксперимента может многократно возникать потребность в смене операндов, На фиг. 2 для примера показана память

8, состоящая из 32 ячеек с адресами от

00000 до 11111. Она используется для размешения четырех очень коротких программ (так как обработка в устройстве выполняется в масштабе времени, определяемом интенсивностью входящего потока событий). Память делится на 8 участков по 4 ячейки так, что 1-й и 5-й участки. используются для первой программы, 2-й и 6-й для второй и т.д.

Первая программа определяет безусловную запись данных из промежуточного регистра 1 в буферную. память 6. Она, как видно на фиг. 2, состоит из одной команды, помещенной в ячейку с адресом 00000. Вторая программа управляет записью "полезных" событий в "канал" в буферную память 6.

Она состоит из трех команд, размещенных

1 793ОЯ

3 в 5 й, 6-" и 22-й ячейках. Первым тактом обработки проверяется "полезность" события.

Если оно не представляет интерес, то запись в буферную память 6 не производится, а программа заканчивается (по команде из

6-й ячейки), если представляет, то запись . выполняется и программа этим заканчивается. Третья программа отличается от второй тем, что запись в память 6 осуществляется в инкрементном режиме. Эта программа . p может быть использована, если память 6 допускает такой режим. Четвертая программа рассчитана на поиск признака представля юшего интерес события за счет двукратного обрашения к памяти 4.

Адрес очередной команды определяется . состоянием регистра 5, которое формируется совокупностью сигналов, поступающих с регистра 7 на базовый вход (в разряды 3 и

4), с блока 11 на входы модификации и с памяти 8 в счетном режиме на управляющий вход (в разряды 1 и 2) .

Адрес операнда в вспомогательной памяти

4 определяется состоянием регистра 9, которое формируется совокупностью сигналов на соответствующих входах, поступающих с регистра 1 (определяет ячейку в выбранной странице памяти), блока 2 и памяти 8 микрокоманд (определяют страницу) .

Блок-схема работы устройства под управлением UBM приведена на фиг. 4.

Для подготовки устройства к накоплению информации сначала устанавливается в исходное состояние регистр 7, в результате чего сбрасывается и переводится в счетный режим регистр 9, а его входы модификации блоки- 35 руются. Этим память 4 подготавливается к приему данных из UBM. После заполнения памяти 4 списком событии, "представляющих интерес", очередной командой UBM регистр

7 переводится в следующее состояние, обес- 4О нсчиваюшее разблокирование входов модификации регистра 9, перевод его в рабочий режим, установление режима работы блоков

2 и 11, а также выбор программы обработ- ки регистрирующих событий установлением базы (началыюго адреса) . Следующей командой LIBM регистр 7 выцает на выход 15 сигнал "Разрешение" для AIIII, открывает тактовьш генератор 10 для сигнала "Готовность" из AUII выдает на регистр 5 разрешение для выполнения программы обработки событий, поступающих на входы 12 и 13 устройства.

Па временной диаграмме (фиг. 5) показан цикл работы устройства по приему, обработке и записи входящих событий в буферную память 6 (на примере второй про ммы), 1!ри поступлешш из А! !1! кода лзбытий на вход 12 н одновременно (либо заранее) одного нли нескольких сигналов внешних параметров на вход 13 информация с регистра 1 проходит на сумматор 3 и одновременно на регистр 9, а информация с бл ка 2 — на регистр 9.

Блок 2 осуществляет прием и ишфрацию сигналов, поступающих на вход 13. Возможны два варианта работы в зависимости от управляющего сигнала, вырабатываемого регистром 7 слова состояния. Первый — прием одного из взаимоисключающих сигналов.

Второй — прием нескольких неисключаюших сигдалов. В качестве блока 2 может быть использована, например, постоянная память, в которой закодированы допустимые состояния внешних сигналов.

При поступлении информации на регистр

9 из памяти 4 считывается код признака регистрируемого события, который говорит о том, что дашгое событие "представляет интерес" либо нет (нулевой код). Этот л<од подается на блок 11, который представляет собой (фиг. 3) набор элементов ИЛИ, реализующих "проводное И". Вход-выход этого блока служит для соединения с идентичными блоками в других устройствах сопряжения, обслуживающих AIIII, для измерения других параметров данного события (при многомерном анализе) . При одномерном анализе связь с магистралью при помощи переключателей !7 разрывается, а информация проходит на сумматор 3, минуя блок

11. Маскирующий сигнал па управляющем входе, поступающий с регистра 7, всегда пропускает код признаков на управляющий выход блока 2 для модификации регистра

5. При многомерном анализе (совместная работа нескольких устройств) возможны два варианта работа. В первом случае определяется совпадение одинаковых кодов признаков для всех устройств. Этот режим отличается от автономной работы только тем, что через переключатели 17 соединены между собой-входы-выходы всех устройств сопряжения. Во втором — информация, регистрируемая данным устройством, подлежит записи в память 6, если ее "полезность" фиксируется всеми остальными устройствами совпадения. Для этого сигналом на управляющем входе блока 2 маскируется прохождение кода признаков на управляющий выход. Код признака, вырабатываемый памятью

4 данного устройства, может быть использован для модификащш данных с АЦП, например для изменения страницы в буферной памяти 6.

1179308

При поступлении на вход 14 и генератор

10 тактового сигнала "Готовность" от АЦП команда проходит на выход памяти 8 микрокомапд и исполняется в соответствии с программой. При окончании программы регистр 7 слова состояния переводится в соответствующее состояние, при .котором устройство подготавливается к приему следующего со-, бытия, т.е. выдается опять сигнал "Разрешение", блокируется генератор 10, открывается его вход 14, регистр 5 переводится в рабочее состояние.

Гаким образом, устройство обеспечивает расширение класса решаемых задач за счет выполнения функций предварительной обработки экспериментальных данных, вводимых в ЭВМ. Это позволит повысить скорость

10 обработки данных и эффективность измерительных систем.

I!79308

117 71

Г) Рюмеиуеииг юроерамм

Юлтмя пи 8 беаусло3иая дпписэ оппоо

nm Na7 юи паж +

Люись если, оР не 47с модификациРй аа мятика

Зались 3 инкрем. режиме, если лаа не 4

Юнее отсечь су

Люись если лоди ф

Иначе Омсюии а)Формат коман3 абраЬотя3 .2

ll79308 гФаее г сегюра ние наивнее ре олгаю омюе no r me. лризнщоо соЪытиц

„предсяюблающик интерес» о1полиро па к о меРиЕзипации.рг9 стан ьмре и о ра ото

Аюне .,1 тан на ноеорепоео кроерамме екаеора гооегюир б Рг б ане сиенола разяВшепип

pukmai дстродегчда сутремсения Сюбмеет о с ALlll

Окидание запроса vari от Рг 7 устройстВа фием запроса vmrwue тение имформаиии накопленной бпаипти6

arm оиеи сеапца напапленир онец раааа

9неи

4Ье 4 дк, 14 бк. 1 бк. 1Ю дик.lTN1 чаи. Рг. К

Фнпр;вю. и б

Жр!вп и. б

Ае. 1б

ВНИИПИ Зжаз 5675/49 Тираж 710 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4