Конвейерное устройство для деления интерационного типа

Иллюстрации

Показать всеРеферат

КОНВЕЙЕРНОЕ УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ИТЕРАЦИОННОГО ТИПА, включающее регистры делимого, делителя и результата, три блока формирования дополнительного кода, пять блоков умножения, причем первый вход первого блока умножения соединен с входом первого блока формирования дополнительного кода, выход которого соединен с первым входом второго блока умножения и вторым входом первого блока умножения, выход которого соединен с первым входом третьего блока умножения и входом второго блока формирования дополнительного кода, выход которого соединен с первым входом четвертого блока умножения и вторым входом третьего блока умножения , выход которого соединен с входом третьего блока формирования дополнительного кода, выход которого соединен с первым входом пятого блока умножения, выход и второй вход которого соединены соответственно с входом регистра результата и выходом четвертого блока умножения, второй вход которого соединен с выходом второго блока-умножения, отличающееся тем, что, с целью сокращения оборудования, оно содержит шифратор и два блока формирования и суммирования кратных, каждый из которых содержит сумматор с сохранением переносов, сумматор с распространением переносов и четыре коммутатора кратного, причем выход старших разрядов регистра делителя соединен с входом шифратора, выходы которого соединены с управляющими входами соответствующих коммутатоi ров кратных первого и второго блоков формирования и суммирования кратных, (Л информационные входы которых соединены соответственно с выходами регистров делителя и делимого, выходы сумматоров с распространением переносов первого и второго блоков формирования и суммирования кратных соединены соответственно с первым входом первого блока умножения и ч вторым входом второго блока умноже (@ ния, а также в каждом из блоков фор&д мирования и суммирования кратных выьэ ходы коммутаторов кратного соединены с соответствующими входами слагаемых сумматора с сохранением переносов, выходы сумм и переносов которого соединены соответственно с входом перво го и второго слагаемых сумматора с распространением переносов, входы переноса сумматора с сохранением переносов соединены соответственно с управляющими входами коммутаторов кратного с первого по третий.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН у1)4 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТ

Н АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВ,Ф

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3694522/24-24 (22) 24.01.84 (46) 15.09.85. Бюл. Р 34 (72) П.В.Борисов и Ю.С.Варакин (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

N - 602944, кл. G 06 F 7/52, 1975-.

2. Гаврилов Ю.В., Пучко А.И. Арифметические устройства быстродействующих ЭЦВМ. М., "Сов.Радио", 1970, с. 221-224 (прототип). (54)(57) КОНВЕЙЕРНОЕ УСТРОЙСТВО ДЛЯ

ДЕЛЕНИЯ ИТЕРАЦИОННОГО ТИПА, включающее регистры делимого, делителя и результата, три блока формирования дополнительного кода, пять блоков умножения, причем первый вход первого блока умножения соединен с входом первого блока формирования дополчительного кода, выход которого соединен с первым входом второго блока умножения и вторым входом первого блока умножения, выход которого соединен с первым входом третьего блока умножения и входом второго блока формирования дополнительного кода, выход которого соединен с первым входом четвертого блока умножения и вторым входом третьего блока умножения, выход которого соединен с входом третьего блока формирования дополнительного кода, выход которого соединен с первым входом пятого блока умножения, выход и второй вход которого соединены соответственно с входом регистра результата и выходом четвертого блока умножения, второй

„„SU„„3 379323 А вход которого соединен с выходом второго блока умножения, о т л и— ч а ю щ е е с я тем, что, с целью сокращения оборудования, оно содержит шифратор и два блока формирования и суммирования кратных, каждый из которых содержит сумматор с сохранением переносов, сумматор с распространением переносов и четыре коммутатора кратного, причем выход старших разрядов регистра делителя соединен с входом шифратора, выходы которого соединены с управляющими входами соответствующих коммутаторов кратных первого и второго блоков формирования и суммирования кратных, информационные входы которых соединены соответственно с выходами регистров делителя и делимого, выходы сумматоров с расгространением переносов первого и второго блоков формирования и суммирования кратных соединены соответственно с первым входом первого блока умножения и вторым входом второго блока умножения, а также в каждом из блоков формирования и суммирования кратных выходы коммутаторов кратного соединены с соответствующими входами слагаемых сумматора с сохранением переносов, выходы сумм и переносов которого соединены соответственно с входом первого и второго слагаемых сумматора с распространением переносов, входы переноса сумматора с сохранением переносов соединены соответственно с управляющими входами коммутаторов кратного с первого по третий.

1 11793

Изобретение относится к автомати= ке и вычислительной технике.и предназначено для использования в цифровых арифметических устройствах.

Известно устройство для деления, использующее итерационные методы, содержащее два регистра операндов, регистр результата, блок памяти, дешифратор, формирователь кратных, пирамидальный конвейерный умножитель, 10 преобразователь в дополнительный код Г1) .

Данное устройство использует метод приведения делителя к единице.

Недостатком его является низкое быст- 15 родействие.

Наиболее близким к изобретению по технической сущности является устройство для деления, содержащее регистры делимого, делителя и результата, семь блоков умножения, три преобразователя в дополнительный код, блок памяти, причем выходы старших разрядов делителя соединены с адресным входом блока памяти, выход которого соединен с первыми входами первого и второго блоков умножения, вторые входы которых соединены соответственно с выходами регистра делимого и делителя, выход второго блока умножения соединен с входом первого преобразователя в дополнительный код, выход которого соединен с первыми входами третьего и четв ртого блока умножения, вторые входы которых соединены соответственно с выходами первого и второго блоков умножения, выход четвертого блока умножения соединен с входом второго преобразователя в дополнительный код, выход которого сое40 динен с первыми входами пятого и шес. того блоков умножения, вторые входы которых соединены соответственно с выходами третьего и четвертого блоков умножения, выход шестого блока

4S умножения соединен со входом третье.го преобразователя в дополнительный код, выход которого соединен с первым входом седьмого блока умножения, второй вход и выход которого соединены соответственно с выходами пятого

50 блока умножения и входом регистра результата f2) .

Недостатком данного устройства является то, что определение начального приближения к обратной величине аргумента (делителя) с использова нием таблицы данных требует дополнительного оборудования на хранение

21 г табличных данных, на перезапоминание значения делителя и делимого для последующего их умножения на значение, полученное из таблицы начального приближения к обратной величине делителя.

Целью изобретения является сокращение оборудования.

Поставленная цель достигается тем, что конвейерное устройство для деления итерационного типа, содержащее регистры делимого, делителя и результата,. три блока формирования дополнительного кода, пять блоков умножения, причем первый вход первого блока умножения соединен с входом первого блока формирования дополнительного кода, выход которого соединен с первым входом второго блока умножения и вторым входом первого блока умножения, выход которого соединен с первым входом третьего блока умножения и входом второго блока формирования дополнительного кода,выход которого соединен с первым вхо— дом четвертого блока умножения и вторым входом третьего .блока умножения, выход которого соединен с входом третьего блока формирования дополнительного кода, выход которого соединен с первым входом пятого блока умножения, выход и второй вход которого соединены соответственно с входом регистра результата и выходом четвертого блока умножения, второй вход которого соединен с выходом второго блока умножения, содержит также шифратор и два блока формирования и суммирования кратных, каждый из которых содержит сумматор с сохранением переносов, сумматор с распространением переносов и четыре коммутатора кратного, причем выход старших разрядов регистра делителя соединен со входом шифратора, выходы которого соединены с управляющими входами соответствующих коммутаторов кратных первого и второго блоков формирования и суммирования кратных, информационные входы которых соединены соответственно с выходами регистров делителя и делимого, выходы сумматоров с распространением переносов первого и второго олоков формирования и суммирования кратных соединены соответственно с первым входом первого блока умножения и вторым входом второго бло21

+АВе :Д

+ А В СД

ПН2 = А В

+АВСД

+ ВСДЕ

11793 ка умножения, а также в каждом из блоков формирования и суммирования кратных выходы коммутаторов кратного соединены с соответствующими входами слагаемых сумматора с сохранением переносов, выходы сумм и переносов которого соединены соответственно с входом первого и второго слагаемых сумматора с распространением переносов, входы переноса сумма- 10 тора с сохранением переносов соединены соответственно с управляющими входами коммутаторов кратного с первого по третий.

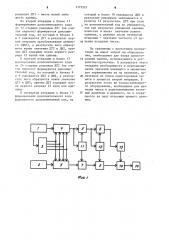

На фиг.1 представлена схема кон- 15 вейерного устройства для деления итерационного типа, на фиг.2 — схема блока формирования и суммирования кратных.

Конвейерное устройство для деления 20 итерационного типа содержит регистр

1 делителя, регистр 2 делимого, шифратор 3, блоки 4 и 5 формирования и суммирования кратных, блоки 6-10 умножения, блоки 11-13 формирования 25 дополнительного кода, регистр 14 результата.

Блок формирования и суммирования кратных содержит коммутаторы 15-18 кратных, сумматор 19 с сохранением щ ,переносов, сумматор 20 с распростра.— нением переносов, информационный вход 21, управляющие входы 22, выход 23.

Шифратор 3 реализуется согласно следующим уравнениям, в которых А, В, С, D, Е, P — шесть старших разрядов делителя, НСД вЂ” "нет сдвига", СД вЂ” "сдвиг", ПП-"прямая передача".

Первый Выход. шифратора 3 40

СД1=(А+В+С+Д+Е) (А+В+Д+ Р+Д Р) (А Е + В Д + В Е + А Д Е) (А + В С +

+ С Д + С Д) (В + Е + Р) (С + Р +

+АД)

НСД1= A В С Д + E С Д E + 4>

+АВ СЕ+ СДР+АВ.СP+АВДР+

+ АВ СДР+ В С Е P+АбЕ Р+.

+АВ СЕ Р+АВДЕ

ПП1= (С + А Р + Е Р + А Р Е) (В Д Е +

+ CE + B E + В Е Р) (А В С) (E E) (АЕР1(АВДЕ) (АВСE) (А С Д Р) (А В С Р) Второй выход шифратора 3:

СД2 = (А В + А С + С Д Е + С Д)

/ (А Д P + В С Е + А Д Е + А В С)

НСД2 = А В С Е Р + В С Д Е Р +

+ А С Д Е Р + А В С Р + А В С Д Е +

4 .

Е+АВСЕ+АСДЕ+

+ В С Д Е + А В Д+ В С Д

Е+ АВС+АВ С+АВД+

+ВСДР+ВСДР+

Третий выход шифратора 3:

СДЗ = А В С + А В Д + А В Е

НСДЗ = А В + В С + В Е Д + В Д Р +

+ А С Д Е + А С Д Е

ППЗ = А + ВС + ВДЕ

Четвертый выход шифратора 3:

СД4 = А В + А С Ц + А С Е

НСД4 = СД4

Конвейерное устройство для деления итерационного типа работает следующим образом.

На регистры 1 и 2 заносятся со- ответственно делитель и делимое.

Шесть старших разрядов делителя поступают на шифратор 3, где в соответствии с приведенными уравнениями формируются сигналы, управляющие формированием кратных.

При помощи управляющих сигналов

СД, НСД, ПП в коммутаторах t5-17 бло. ка 4 формируются соответственно первое, второе и третье кратное делителю числа, а в коммутаторах 15-17 бло ка 5 формируются соответственно первое, второе и третье кратное делимому числа. При помощи управляющих сигналов СД4 и НСД4 в коммутаторах

18 блоков 4 и 5 формируются четвертое кратное делителю и делимому числа. Коммутаторы 15-18 кратного выполняют при сигналах ПП, ПП, НСД, СД на управляющих входах передачу информации с информационного зхода на выход соответственно прямо, инверсно, без сдвига и со сдвигом на один разряд.

Сформированные четыре кратные делителю числа суммируются в дополнитель. ном коде на сумматоре 19 с сохранением переносов блока 4, при этом сигналы ПП для первых трех кратных выполняют роль единицы дополнительного кода, поступающей на вход переноса сумматора. Аналогично суммируются четыре кратные делимому числа в блоке 5. После сложения результатов с сумматоров 19 с сохранением переносов на сумматорах 20 с распространением переносов образуются результаты первой итерации деления (ДТ1). В результате первой итерации в старших

1179321 разрядах ДТ1 — шесть нулей либо шесть единиц.

Во второй итерации в блоке 11 формирования дополнительного кода от 12 старших разрядов ДХ1 (не считая первого) формируется дополнительный код, на который в блоках 6 и 7 умножаются ДТ1 и результат первой итерации преобразования делимого (ДМ1), в результате чего образуются новые значения ДТ2 и ДМ2, причем ДТ2 содержит после первого разряда 12 нулей или единиц.

В третьей итерации в блоке 12 формирования дополнительного кода от 24 старших разрядов ДТ2 (не считая первого) формируется дополнительный код, на который в блоках 8 и 9 умножаются ДТ2 и ДМ2, в результате чего образуются новые значения

ДТЗ и ДМЗ, причем ДТЗ содержит после первого разряда 24 нуля или единищл.

В четвертой итерации в блоке 13 формирования дополнительного кода формируется дополнительный код, на который в блоке 10 умножается ДМЗ и результат умножения записывается в регистр 14 результата. ДТЗ при этом

> на дополнительный код не умножается, так как результат умножения заранее известен и имеет значение равное единице., -а делимое после четвертой итерации — значение частного от де1п ления исходных чисел.

По сравнению с прототипом изобретение не имеет затрат на оборудование, необходимое для блока одностоtS ронней памяти, используемого в устройстве-прототипе. В результате этого отпадает необходимость в перезапоминании значений множимого и множителя для перемножения их на значение, по20 лученное из блока односторонней памяти в процессе второй итерации. В результате этого не только уменьшается оборудование, необходимое для хранения чисел и перезапоминания значений делителя и делимого, но и сокращается на одну итерацию процесс деления.

11?9321

Составитель А.Клюев

Редактор С.Тимохина Техред Т.Фанта Корректор О.Луговая

Заказ 5676/50 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óæãoðoä, ул.Проектная, 4