Конвейерное устройство для вычисления функции @

Иллюстрации

Показать всеРеферат

КОНВЕЙЕРНОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ lj 5ini-X содержащее входной регистр, два блока памяти, четыре промежуточных регистра, два сумматора, выходной регистр, информационный вход которого соединен с выходом первого сумматора , выход старших разрядов входного регистра соединен с адресным входом первого блока памяти и информационным входом первого промежуточного регистра, выход которого соединен с адресным входом второго блока памяти, выход второго сумматора соединен с информационным входом третьего промежуточного регистра , отличающееся тем, что, с целью упрощения устройства , оно содержит к-вадратор, блок : синхронизации и сдвигатель причем выход 1 -го разряда входного регистра i 1,2,... Иj где п - разрядность аргумента, соединен с первым входом (i+4)-ro разряда второго сумматора, второй вход (i+4)-ro разряда которого соединен с вькодом первого блока памяти, а выход (i+4)-ro разряда второго сумматора соединен с входом соответствующего разряда третьего промежуточного регистра , выход которого через квадратор соединен с информационным входом четвертого промежуточного регистра, выход которого соединен с информационным входом сдвигателя, выходы двух старших разрядов второго промежуточного регистра соединены § с управляющими входами сдвигателя, инверсный выход которого соединен С/} с первым входом первого сумматора, второй вход которого соединен с выходом второго блока памяти, причем блок синхронизации содержит элемент И,триггер, генератор импульссов и регистр сдвига, информационньй и управляюшд й входы которого соединеtaoA J ны соответственно с прямым выходом триггера и инверсным выходом генератора импульсов, прямой выход кото00 Ьд рого соединен с входом синхронизации триггера, информационный вход кото@д рого соединен с выходом элемента И, первьм и второй входы которого соединены с инверсным выходом триггера и входом пуска устройства соответственно , вход сброса которого соединен с установочными входами триггера и регистра сдвига, выход третьего разряда которого соединен с входом синхронизации входного регистра, вход синхронизации первого и третьего промежуточных регистров соединены с выходом пятого разряда регистра сдвига, выход седьмого разряда

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧ ЕСНИХ

РЕСПУБЛИН (s>)g G 06 F 7/548

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, ";

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3718319/24 — 24 (22) 06. 01 . 84 (46) 15.09.85. Бюл. 11У 34 (72) Н.В. Черкасский, В.М. Крищишин и Г.Ф . Криворучко (7i) Львовский ордена Ленина политехнический институт им. Ленинского комсомола и Институт прикладных проблем механики и математики

АН УССР (53) 681.325(088.8) (56) Авторское свидетельство СССР

9 907546, кл. G 06 F 7/548, 1980.

Авторское свидетельство СССР

МВ- 922734, кл. G 06 F 7/548, 1980. (54) (57) КОНВЕЙЕРНОЕ УСТРОЙСТВО

ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЛИН В=В ч — Х), содержащее входной регистр, два блока памяти, четыре промежуточных регистра, два сумматора, выходной регистр, информационный вход которого соединен с выходом первого сумматора, выход старших разрядов входного регистра соединен с адресным входом первого блока памяти и информациочным входом первого промежуточного регистра, выход которого соединен с адресным входом второго блока памяти, выход второго сумматора соединен с информационным входом третьего промежуточного регистра, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит квадратор, блок : синхронизации и сдвигатель причем выход 1 -ro разряда входного регистра j = 1,2,... и где п — разрядность аргумента, соединен с первым

„„SU„„ I 3 т9ззе A входом (В+4)-ro разряда второго сумматора, второй вход (i+4)-го разряда которого соединен с выходом первого блока памяти, а выход (i+4) — го разряда второго сумматора соединен с входом соответствующего разряда третьего промежуточного регистра, выход которого через квадратор соединен с информационным входом четвертого промежуточного регистра, выход которого соединен с информационным входом сдвигателя, выходы двух старших разрядов второго промежуточного регистра соединены с управляющими входами сдвигателя, инверсный выход которого соединен с первым входом первого сумматора, второй вход которого соединен с выходом второго блока памяти, причем блок синхронизации содержит элемент

И„ триггер, генератор импульссов и регистр сдвига, информационный и управляющий входы которого соединены соответственно с прямым выходом триггера и инверсным выходом генератора импульсов, прямой выход которого соединен с входом синхронизации триггера, информационный вход которого соединен с выходом элемента И, первый и второй входы которого соединены с инверсным выходом триггера и входом пуска устройства соответственно, вход сброса которого соединен с установочными входами триггера и регистра сдвига, выход третьего разряда которого соединен с входом синхронизации входного регистра, вход синхронизации первого и третьего промежуточных регистров соединены с выходом пятого разряда регистра сдвига, выход седьмого разряда которого соединен с входами синхронизации второго и четвертого промежуточных регистров, выход девятого

1179326 разряда регистра сдвига соединены с входом синхронизации выходного регистра.

Изобретение относится к области вычислительной техники и предназначено для использования в универсаль-, ных и специализированных вычислительных устройствах при обработке боль шах массивов данных.

Целью изобретения является упрощение устройства.

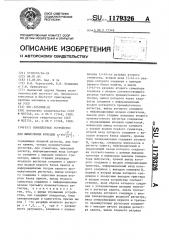

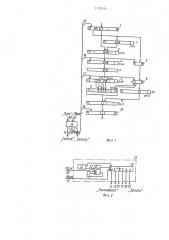

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 — блока синхрониза-. ции; на фиг. 3 — временная диаграмма работы устройства.

Устройство (фиг. 1) содержит входной регистр 1, блок памяти 2, сумматор 3, громежуточные регистры

4 и 5, квадратор 6, промежуточные регистры 7 и 8, сдвигатель 9, блок памяти 10, сумматор 11, выходной регистр 12, блок синхронизации 13 с выходами 14-19 и входами 20 .и 21.

Блок синхронизации 13 (фиг; 2) содержит генератор 22 тактовых импульсов, элемент И 23, триггер 24 и сдвиговый регистр 25.

Квадратор 6 может быть выполнен различным образом, но должен обладать достаточным быстродействием.

В частности, в качестве квадратора может быть использован быстродействующий перемножитель.

Промежуточные регистры 4, 5 и 7, 8 предназначены для. кратковременногс запоминания результатов промежуточных вычислений и для обеспечения конвейерного способа обработки. При этом регистр 4 имеет разрядность

n+4 (при разрядности регистров 1 и 12, равной И ), регистр 7 имеет разрядность Ь +6, а регистры 5 и 8 разрядность К

Вычисление функции н из П(" от аргумента Х (О Х 1) производится на основе метода сегментной аппроксимации выражением вида

=А + W (Х+Ь), где константы A

45 функции, ч ° slh(— hj > вирриениеи .ви/Я да у = А — 003125 9+8) диапазоне (1/4, 1/2) - ) = А - 0,0625 (х+Ь) в диапазоне 1/2, 3/4 — - "А

0,125 (х +3), в диапазоне (Э/4, 1) =А - 0,25 (x+8) .

Устройство работает следующим образом.

Перед обработкой массива чисел на вход 21 "Сброс" блока 13 синхро8,YI выбираются из условия минимизации абсолютной, погрешности. При этом коэффициент У/ выбирается равным степени числа два. Для функции

ij= & п — x 1 коэффициент Д являет° lФ Ь ! ся положительным, а коэффициент 8 отрицательным, независимо от числа разбиений интервала изменения ар— гумента на сегменты. Коэффициент Щ принимает в зависимости от двух старших разрядов аргумента, четыре значения: — 0,03125, — 0,0625, 0,125, — 0,25.

Диапазон изменения аргумента (°

0,1) разбивается на интервалы, количество которых определяется тре.буемой точностью, причем границы интервалов выражаются К старшими двоичными разрядами аргумента.

На разных интервалах константы

А. и В имеют различные значения.

Константы о хранятся в блоке памяти 2, а константы A — в блоке памяти 10. Адресация к каждому блоку памяти осуществляется по старшим разрядам аргумента, которые определяют, в каком интервале находится аргумент. Разрядность блоков памяти 2 и 10 определяется требуемой точностью вычисления функции.

Для интервалов, соответствующих

° диапазону изменения аргумента (0,1/4) коэффициенты A и 8 соответствуют наилучшему равномерному приближению

1179326

l0

20

45 низации подается сигнал "Сброс" (фиг. 3 q ), который приводит триггер

24 и сдвиговый регистр 25 в исходное состояние. После прихода сигнала 20 "Пуск" (фиг. 3 8 ) элемент

И 23 разрешает прохождение информации с инверсного выхода триггера

24 на его информационный вход. Триго

rep 24 осуществляет, деление частоты генератора 22 тактовых импульсов на два (фиг. 3 b ). По переднему фронту импульсов с инверсного выхода генератора 22 информация с выхода триггера 24 заносится в сдвиговьпf регистр 25 и с каждым новым импульсом сдвигается вправо. Выход первого разряда регистра сдвига 25. управляет считыванием чисел иэ внешних блоков памяти (фиг. 3)), выход третьего разряда управляет заносом числа во входной регистр 1 по выходу 15 (фиг. 3 е) . Выход пятого разряда регистра 25 управляет заносом чисел в регистры 4 и 5 (фиг. 3 L;) по выходу 16. Выход седьмого разряда регистра 25 управляет заносом чисел в регистры 7 и 8 (фиг. 3, л ) по выходу 17 блока синхронизации 13. Выход девятого разряда регистра 25 управляет заносом чисел в выходной регистр 12 (фиг. 3 н ) по выходу 18 блока 13. Выход одиннадцатого разряда регистра 25 управляет записью выходного числа во внешние блоки памяти по выходу 19 блока 13. Выходы четных разрядов сдвигового регистра 25 не используются. Структура блока синхронизации 13 учитывает инерционность конвейера и после снятия сигнала "Пуск" корректно завершает разработку чисел, ранее принятых для обработки.

В первом такте работы устройства в регистр 1 поступает аргумент Х<

С выхода регистра 1 значение аргумента поступает на сумматор 3 со сдвигом на 4 разряда вправо. Одновре4 менно из блока памяти 2 по адресу, укаэанному K старшими разрядами аргумента Х<, выбирается константа 8, и также поступает на сумматор 3. В сумматоре 3 происходит выработка суммы У,+ B, Во втором такте значение х, + В, записывается в регистр 4 и возводится в квадрат в блоке 6. В том же такте значение К старших разрядов аргумента х, записывается в регистр 5, а в регистр 1 поступает следующее значение аргумента Х, В третьем такте значение(х, + В,) записывается в регистр 7 и через сдвигатель 9 поступает на вход сумматора 11 беэ сдвига или со сдвигом на один, два или три разряда вправо.

Одновременно в регистр 8 переписывается иэ регистра 5 значение К старших разрядов аргумента Х,, являющееся адресом константы А<, хранимой в блоке 10. Значение двух старших разрядов регистра 8 поступают, кроме того, на управляющие входы сдвигателя 9 и управляют сдвигом величины (х1+ B,) Константа 4, 2 поступает иэ блока памяти 10 на второй вход сумматора 11, где и производится выработка суммы А - Ф,(Х,+ В,)

Так как значение Щ всегда отрицательно, то сумматор 11 фактически работает на вычитание. В этом же такте в регистр 4 записывается значение X > B, а в регистр 5 — значение k старших разрядов аргумента Х . В регистр 1 записывается следующее число Х, В четвертом такте в регистр 12 записывается значение ) = я w и, (к + В, ), являющееся искомым приближением фтеккии .- ек о ех),е точке х =x,; в регистры 4, 5 и 7, 8 записываются результыты промежуточных вычислений над аргументами х и Х, а в регистр 1 записывается новое число Х4 .

117932б

1179326

1

1

1

t

t Очаг. 3

Составитель А.Зорин

Редактор С.Тимохина Техред Т.Фанта Корректор А.Тяско

Заказ 5676/50 Тираж 710 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4