Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок постоянной памяти микрокоманд, регистр адреса и регистр микрокоманд, мультиплексор , первый коммутатор адреса, триггер пуска, генератор тактовых импульсов, причем вход пуска устройства соединен с единичным входом триггера пуска, выход которого соединен с входом генератора тактовых импульсов, выход регистра адреса соединен с адресным входом блока постояниой памяти микрокоманд, первый информационный выход которого соединен с первым информационным входом регистра микрокоманд , выход микроопераций регистра микрокоманд соединен с выходом микроопераций устройства, а выход микрооперации «Конец работы соединен с нулевым входом триггера пуска, выход логических условий регистра микрокоманд соединен с управляющим входом мультиплексора, информационный вход которого соединен с входом логических условий устройства, выход первого коммутатора адреса соединен с информационным входом регистра адреса, отличающееся тем, что, с целью уменьшения объема оборудования, в устройство введены второй коммутатор адреса, буферный регистр, блок элементов И, первый, второй и третий элементы И, элемент ИЛИ, причем вход кода операции устройства соединен с первым информационным входом первого коммутатора адреса, первый выход генератора тактовых импульсов соединен с входом синхронизации регистра адреса, второй выход генератора тактовых импульсов соединен с входом синхронизации регистра микрокоманд и первым входом первого элемента И, выход которого соединен с входом синхронизации буферного регистра, первый и второй выходы буферного регистра соединены с первыми группами входов соответственно первого и второго информационных входов второго коммутатора адреса, выход которого соединен с первой группой входов второго информационного входа первого коммутатора адреса, i второй информационный выход блока постоянной памяти микрокоманд соединен с ин (Л формационным входом буферного регистра, прямым входом блока элементов И и входами элемента ИЛИ, выход блока элементов И соединен с вторым информационным входом регистра микрокоманд, выход элемента ИЛИ соединен с инверсным входом второго элемента И и прямым входом третьего элемента И, выходы которых соединены соответственно с выходом ошибки устройства и первым управляющим входом второго ;о со коммутатора адреса, выход логических условий блока постоянной памяти микрокоманд соединен с инверсными входами блока эле00 00 ментов И, с прямыми входами первого и второго элемента И и с инверсным входом третьего элемента И, выход мультиплексора соединен с вторым управляющим входом второго коммутатора адреса, выходы немодифицируемой и модифицируемой частей адреса регистра микрокоманд соединены соответственно с второй группой входов второго информационного входа первого коммутатора адреса и третьим информационным входом второго коммутатора адреса, выход микрооперации «Конец команды регистра микрокоманд соединен с прямым и инверсным управляющими входами первого комму

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1179338 (s»4 G 06 F 9 22, 11/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

/ 3Cprg

ОПИСАНИЕ ИЗОБРЕТЕНИ ц " ...

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ .:„,, Ц г (21) 3708650/24-24 (22) 11.03.84 (46) 15,09.85. Бюл. № 34 (72) B. П. Супрун, Г. Н. Тимонькин, В. С. Харченко, В. А. Малахов, С. Н. Ткаченко и К. Ю. Воробьев (53) .681.3 (088.8) (56) Авторское свидетельство СССР № 928356, кл. G 06 F 9/22, 1980.

Хассон С. Микроп рограм мное уп равление, М.: Мир, ч. 1, 1974, с. 37 — 42, рис. 21, 22.

Майоров С. А. и Новиков Г. И. Структура ЭВМ. «Машиностроение», 1979, с. 312—

314, рис. 10.4. (54) (57) МИКРОПРОГРАММНОЕ УСТPOACTBO УПРАВЛЕНИЯ, содержащее блок постоянной памяти микрокоманд, регистр адреса и регистр микрокоманд, мультиплексор, первый коммутатор адреса, триггер пуска, генератор тактовых импульсов, причем вход пуска устройства соединен с единичным входом триггера пуска, выход которого соединен с входом генератора тактовых импульсов, выход регистра адреса соединен с адресным входом блока постоянной памяти микрокоманд, первый информационный выход которого соединен с первым информационным входом регистра микрокоманд, выход микроопераций регистра микрокоманд соединен с выходом микроопераций устройства, а выход микрооперации «Конец работы> соединен с нулевым входом триггера пуска, выход логических условий регистра микрокоманд соединен с управляющим входом мультиплексора, информационный вход которого соединен с входом логических условий устройства, выход первого коммутатора адреса соединен с информационным входом регистра адреса, отличающееся тем, что, с целью уменьшения объема оборудования, в устройство введены второй коммутатор адреса, буферный регистр, блок

:элементов И, первый, второй и третий элементы И, элемент ИЛИ, причем вход кода операции устройства соединен с первым информационным входом первого коммутатора адреса, первый выход генератора тактовых импульсов соединен с входом синхронизации регистра адреса, второй выход генератора тактовых импульсов соединен с входом синхронизации регистра микрокоманд и первым входом первого элемента И, выход которого соединен с входом синхронизации буферного регистра, первый и второй выходы буферного регистра соединены с первыми группами входов соответственно первого и второго и нформационных входов второго коммутатора адреса, выход которого соединен с первой группой входов второго информационного входа первого коммутатора адреса, второй информационный выход блока посто- И янной памяти микрокоманд соединен с информационным входом буферного регистра, Ц ф прямым входом блока элементов И и входа- уют ми элемента ИЛИ, выход блока элементов

И соединен с вторым информационным входом регистра микрокоманд, выход элемента 9

ИЛИ соединен с инверсным входом второго элемента И и прямым входом третьего элемента И, выходы которых соединены соответственно с выходом ошиб ки устройства и первым управляющим входом второго коммутатора адреса, выход логических усло- Я ) вий блока постоянной памяти микрокоманд соединен с инверсными входами блока элементов И, с прямыми входами первого и второго элемента И и с инверсным входом третьего элемента И, выход мультиплексора соединен с вторым управляющим входом второго коммутатора адреса, выходы немодифицируемой и модифицируемой частей адреса регистра микрокоманд соединены соответственно с второй группой входов второго информационного входа первого коммутатора адреса и третьим информационным входом второго коммутатора адреса, выход микрооперации «Конец команды» регистра микрокоманд соединен с прямым и инверсным управляющими входами первого комму1 179338 татора адреса, первая и вторая группы выходов модифицируемой части адреса регистра микрокоманд соединены с вторыми группа1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении центральных и периферийных устройств управления ЭВМ и вычислительных систем.

Целью изобретения является уменьшение объема используемого оборудования.

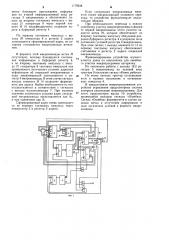

На фиг. 1 приведена функциональная схема микропрограммного устройства управления; на фиг. 2 — фрагмент реализуемой микропрограммы; на фиг. 3 — размещение информации в полях микрокоманд, предшествующих ветвлению (Ф I ) и микрокоманд ветвления (Ф2) .

Микроп рограммное устройство управления (фиг. 1) с конролем содержит блок 1 постоянной памяти микрокоманд, регистр 2 адреса и регистр 3 микрокоманд, буферный регистр 4, первый 5 и второй 6 коммутаторы адреса, мультиплексор 7, генератор 8 тактовых импульсов, триггер 9 пуска, первый элемент И 10, элемент ИЛИ 11, блок 12 элементов И, второй 13 и третий 14 элементы И, входы кода операции 15, логических условий 16 и пуска 17 устройства, выходы микроопераций 18 (в том числе выходы микроопераций «Конец команды» 18.1 и «Конец работы» 18.2) и ошибки 19 устройства, первый 20 и второй 21 выходы генератора 8, первый 22 и второй 23 информационные выходы и выход 24 логических условий блока 1 постоянной памяти микрокоманд, выходы немодифицируемой 25 и модифицируемой 26 частей адреса регистра 3, первый 27 и второй 28 выходы регистра 4.

На фиг. 2 и 3 использованы следующие обозначения:

R; — микрокоманда i; х; — логическое условие j;

Ф I — формат микрокоманды, предшествующей микрокоманде ветвления;

Ф2 — формат микрокоманды ветвления.

Назначение основных элементов микропрограммного устройства управления (фиг. 1) состоит в следующем.

Блок 1 постоянной памяти микрокоманд предназначен для хранения адресных и операционных частей микрокоманд, кодов логических условий и метки М, предназначенной для уп равления работой устройства.

Регистр 2 адреса предназначен для хранения адреса очередной микрокоманды. Запись следующего адреса в регистр 2 адми входов соответственно первого и второго информационных входов второго коммутатора адреса.

2 реса осуществляется по заднему фронту первого тактового импульса, формируемого генератором 8 тактовых импульсов.

Регистр 3 микрокоманд предназначен для приема, хранения и выдачи микрокоманд, каждая из которых содержит поле немодифицируемых адресных разрядов, поле модифицируемых разрядов адреса, поле микрооперации, поле метки и кодов логических условий. Запись очередной микроко1о манды в регистр 9 микрокоманд осуществляется по заднему фронту второго импульса.

Буферный регистр 4 предназначен для приема, хранения и выдачи модифицируемых разрядов адреса микрокоманды ветвлений, считанных из поля кодов логических условий блока 1 по заднему фронту второго тактового импульса при разрешающем сигнале метки.

Первый коммутатор 5 адреса предназначен для коммутации адреса очередной микрокоманды. При отсутствии сигнала микроопераций «Конец команды» на выходе 18.1 регистра 3 микрокоманд на информационный вход регистра 2 адреса поступает адрес, сформированный из модифицируемой и немодифицируемой частей — составной адрес.

25 В противном случае в регистр 2 адрес передается код выполняемой операции со входа 15 устройства, который определяет адрес первой микрокоманды соответствующей микропрограммы.

Второй коммутатор 6 адреса предназначен для формирования модифицируемой части адреса очередной микрокоманды из модифицируемых разрядов адреса, поступающих на его информационные входы с выходов 26 регистра 3 микрокоманд и выходов 27 и

28 буферного регистра 4 в соответствии с управляющими сигналами, поступающими с выхода мультиплексора 7 и третьего элемента И 14. При отсутствии сигнала с выхода третьего элемента И 14 все немодифицируемые разряды адреса выхода 25

4О непосредственно, а с выхода 26 регистра 3 микрокоманд через коммутатор 6, поступают на второй информационный вход первого коммутатора 5 адреса. При этом информация на выходе буферного регистра 4 отсутствует.

После появления сигнала на выходе эле4 мента И 14 адрес очередной микрокоманды формируется с учетом значения проверяемого логического условия на мультиплек1 179338 соре 7. При единичном значении сигнала с выхода мультиплексора 7 на вход первого коммутатора 5 поступает часть адреса, сформированная из модифицируемых разрядов адреса, поступивших на вход коммутатора 6 с выхода 26 регистра 3 микрокоманд и 27 буферного регистра 4, соответствующих единичному значению проверяемого логического условия. При нулевом значении сигнала с выхода мультиплексора 7 на вход первого коммутатора 5 адреса поступает адрес, сформированный из модифицируемых разрядов адреса, поступающих на вход коммутатора 6 адреса с выхода 26 регистра 3 микрокоманд и выхода 28 буферного регистра 4 и соответствующих нулевому значению проверяемого логического условия.

Мультиплексор 7 предназначен для выделения значения проверяемого логического условия. С этой целью на его информационные входы подаются сигналы логических условий, поступающие на вход 16 устройства, а на управляющие входы — коды проверяемых логических условий с выхода регистра 3 микрокоманд.

Генератор 8 тактовых им пульсов предназначен для синхронизации работы устройства.

На его выходах 20 и 21 формируются первый и второй тактовые импульсы соответственно.

Триггер 9 пуска предназначен для управления запуском генератора 8 тактовых импульсов. Его включение происходит по сигналу «Пуск», поступающему на вход 17 устройства, а выключение — по сигналу «Конец работы» с выхода 18.2 регистра 3 микрокоманд. Первый элемент И 10 управляет передачей тактового импульса с выхода 21 генератора 8 тактовых импульсов в соответствии со значением управляющей метки на синхронизирующий вход буферного регистра 4.

Элемент ИЛИ 11 предназначен для выдачи сигнала о наличии информации в поле логических условий микрокоманды.

Блок 12 элементов И управляет поступлением значений разрядов поля логических условий на второй информационный вход

D2 регистра 3 микрокоманд в соответствии со значением управляющей метки.

Второй элемент И 13 формирует на выходе устройства 19 сигнал «Ошибка». Сигнал формируется при условии появления метки при отсутствии информации в поле логических условий микрокоманды.

Третий элемент И 14 предназначен для формирования сигнала, управляющего коммутатором 6 адреса.

Рассмотрим функционирование микропрограммногоо устройства управления.

В исходном состоянии все элементы памяти устройства (фиг. 1) находятся в нулевом состоянии за исключением единичного состояния разряда регистра 3 микро5 о

55 команд, соответствующего выходу 18.1 регистра 3 микрокоманд. Цепи приведения в исходное состояние на схеме условно не показаны. Последний разрешает передачу через коммутатор 5 кода операции со входа 15 устройства для его последующей записи в регистр 2 адреса.

По сигналу «Пуск» со входа 17 устройства триггер 9 устанавливается в единичное состояние и выключает генератор 8 тактовых импульсов. По первому тактовому импульсу с выхода 20 генератора 8 в регистр

2 адреса со входа 15 кода операции устройства через первый коммутатор 5 адреса записывается код реализуемой операции, который определяет адрес первой микрокоманды, соответствующей микропрограммы.

Рассмотрим реализацию линейного участка микропрограммы.

В этом случае информация в поле логических условий микрокоманд отсутствует и значение метки равно нулю.

По второму тактовому импульсу с выхода 21 генератора 8 адрес следующей микрокоманды и код микрокоманды записываются в регистр 3 микрокоманд. Код микрокоманды выдается с выходов регистра 3 микрокоманд на выход 18 микроопераций устройства. Немодифицируемые разряды адреса поступают с выхода 25 регистра 3 микрокоманд на вторые информационные входы коммутатора 5 адреса; а модифицируемые разряды адреса с выхода 26 регистра 3 микрокоманд через второй коммутатор 6 адреса по разрешающему сигналу с выхода 18.2 регистра 3 поступают на второй информационный вход коммутатора 5. Таким образом, адрес микрокоманды является суммой немодифицируемых старших разрядов адреса (фиг. 3), модифицируемых разрядов адреса, соответствующих нулевому значению проверяемых логических условий, модифицируемых разрядов адреса, соответствующих единичному значению проверяемых логических услови й.

По очередному тактовому импульсу с выхода 20 генератора 8 тактовых импульсов в регистр 2 адреса со второго и .третьего информационных входов второго коммутатора 6 адреса считывается сформированный адрес микрокоманды и работа устройства осуществляется в соответствии с описанным.

При необходимости реализации условного перехода устройство функционирует следующим образом.

В формате поля логических условий (фиг. 3) микрокоманды, предшествующей микрокоманде ветвления, задаются модифицируемые части адреса: модифицируемые разряды адреса, соответствующие нулевому значению проверяемого логического условия и модифицируем ые разряды адреса, соответствующие единичному значению проверяемого логического условия и управляющая метка М. В результате этого

1179338 метка блокирует прохождение информации на второй информационный вход регистра 3 микрокоманд и обеспечивает зались по второму тактовому импульсу с выхода 21 генератора 8 через первый элемент И 10 модифицируемых разрядов адреса в буферный регистр 4.

По первому тактовому импульсу с выхода 20 генератора 8 в регистр 2 адреса записывается сформированный адрес, по которому считывается микрокоманда ветвления.

В формате этой микрокоманды метка М отсутствует, поэтому блокируется считывание информации в буферный регистр 4, и по второму тактовому импульсу с выхода 21 генератора 8 тактовых импульсов код проверяемого логического условия, адресная информация об очередной микрокоманде и коды микроопераций записываются в регистр 3 микрокоманды. В этом случае сигнал с выхода элемента И 14 позволяет формировать два адреса. Выбор необходимого из них осуществляется в соответствии с сигналом с выхода мультиплексора 7. При нулевом значении логического условия адрес следующей микрокоманды представляется как Ао, а при единичном как Ai.

Сформированный адрес вновь записывается по первому тактовому импульсу через коммутатор 5 в регистр 2 адреса.

Если следующая микрокоманда является также микрокомандой условного перехода, то устройство функционирует аналогичным образом.

При необходимости перехода к новому линейному участку микропрограммы в формате первой микрокоманды этого участка задается метка М, которая обеспечивает по второму тактовому импульсу обнуления разрядов буферного регистра 4 и разрядов поля

1 логических условий регистра 3 микрокоманд.

При этом сигнал с выхода элемента И 14 по первому тактовому импульсу обеспечивает считывание в регистр 2 адреса очередной микрокоманды.

Функционирование устройства осущест15 вляется далее по описанному для линеиного участка микроп рогра м мы алгоритму.

По окончании работы с выхода 18.2 регистра 3 микрокоманд на нулевой вход триггера 9 поступает сигнал «Конец работы».

По этому сигналу триггер устанавливается в нулевое положение и останавливает генератор 8.

В предлагаемом микропрограммном устройстве управления предусмотрена система контроля реализации микропрограммы. Для этого предусмотрен выход 19 устройства, являющийся выходом сигнала «Ошибка».

Сигнал «Ошибка» формируется в случае наличия метки и отсутствия информации в поле логических условий в формате микрокоманды.

1179338

Редактор С. Тимохина

Заказ 5677/5!

Составитель И. Снгалов

Техред И. Верес Корректор М. Самборская

Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )K — 35, Раушская наб., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4