Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микропрограмм, первый и второй счетчики, три блока элементов И, блок элементов ИЛИ, триггер, первый, второй и третий элементы И, блок объединения признаков условного перехода, содержащий два элемента ИЛИ и элемент И, и блок выделения групп признаков, содержащий дещифратор, п групп элементов И (где п - количество одновременно анализируемых логических условий) и п элементов ИЛИ, причем информационные выходы первого и второго счетчиков соединены соответственно с первыми входами первого и второго блоков элементов И, выходы которых соединены со входами блока элементов ИЛИ, выход которого соединен с адресным входом блока памяти .микропрограмм , выход первого элемента ИЛИ блока объединения признаков условного перехода соединен с первым входом элемента И блока объединения признаков условного перехода , выход которого соединен с первым входом второго элемента ИЛИ блока объединения признаков условного перехода, выход которого соединен с первым входом третьего элемента И, единичный и нулевой выходы триггера соединены соответственно с первыми входами первого и второго элементов И, группа входов признаков устройства подключена к первым входам элементов И групп блока выделения группы признаков, вторые входы которых соединены с соответствующими выходами дешифратора, выходы элементов И г-й группы (,л) блока выделения группы признаков соединены со входами г-го элемента ИЛИ группы блока выделения группы признаков , группа выходов элементов ИЛИ группы блока выделения группы признаков соединена с первой группой входов третьего блока элементов И, отличающееся тем, что, с целью сокращения оборудования за счет снижения объема блока па .мяти микропрограмм, оно содержит сумматор , коммутатор, элемент НЕ и блок формирования кодов, содержащий постоянную память и п мультиплексоров, причем инфорI мационные входы первого и второго регистров соединены с выходом сумматора, пер (Л вая и вторая группы входов которого подключены соответственно к группе выходов коммутатора и к выходам п мультиплексоров , управляющие входы которых соединены с соответствующими выходами постоянной памяти, группа адресных входов которой подключена к группе выходов третьего блока элементов И и к группе вхо дов первого элемента ИЛИ блока объеди оо 00 нения признаков условного перехода, информационные входы п мультиплексоров подключены ко второй группе входов третьего блока элементов И и к группе входов ;о маски устройства, вход чтения постоянной памяти соединен с выходом признака запрета работы блока формирования кодов блока памяти микропрограмм, выход кода проверки анализируемого вектора условий которого соединен со входом дешифратора, первый информационный в.ход коммутатора соединен с выходом поля адреса блока памяти микрокоманд, выход признака модификации адреса которого соединен с управляющим входом коммутатора, второй информационный вход которого соединен с выходо .м блока элементов ИЛИ, выходы призна

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51)4 G 06 F 9 22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3724820/24-24 (22) 19.01.84 (46) 15.09.85. Бюл. № 34 (72) В. О. Бялый, В. Б. Виноградов, И. А. Коммисарова и М. С. Куприянов (71) Ленинградский институт авиационного приборостроения (53) 681.325 (088.8) (56) Кравцов Л. Я., Черницкий Г. И. Проектирование микропрограммных устройств управления. Л.: Энергия, 1976, с. 47.

Авторское свидетельство СССР № 760099, кл. G 06 F 9/22, 1978. (54) (57) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержа щее блок памяти микропрограмм, первый и второй счетчики, три блока элементов И, блок элементов ИЛИ, триггер, первый, второй и третий элементы И, блок объединения признаков условного перехода, содержащий два элемента ИЛИ и элемент И, и блок выделения групп признаков, содержащий дешифратор, и групп элементов И (где и — количество одновременно анализируемых логических условий) и и элементов ИЛИ, причем информационные выходы первого и второго счетчиков соединены соответственно с первыми входами первого и второго блоков элементов И, выходы которых соединены со входами блока элементов ИЛИ, выход которого соединен с адресным входом блока памяти микроп рограмм, выход первого элемента ИЛИ блока объединения признаков условного перехода соединен с первым входом элемента И блока объединения признаков условного перехода, выход которого соединен с первым входом второго элемента ИЛИ блока объединения признаков условного перехода, выход которого соединен с первым входом третьего элемента И, единичный и нулевой выходы триггера соединены соответственно с первыми входами первого и второго элементов И, группа входов признаков устройства подключена к первым вхо„„SU„„1179339 А дам элементов И групп блока выделения группы признаков, вторые входы которых соединены с соответствующими выходами дешифратора, выходы элементов И i-й группы (i=1, n) блока выделения группы признаков соединены со входами -ro элемента

ИЛИ группы блока выделения группы признаков, группа выходов элементов ИЛИ группы блока выделения группы признаков соединена с первой группой входов третьего блока элементов И, отличающееся тем, что, с целью сокрашения оборудования за счет снижения объема блока памяти микропрограмм, оно содержит сумматор, коммутатор, элемент НЕ и блок формирования кодов, содержащий постоянную память и и мультиплексоров, причем информационные входы первого и второго регистров соединены с выходом сумматора, первая и вторая группы входов которого подключены соответственно к группе выходов коммутатора и к выходам и мультиплексоров, управляющие входы которых соединены с соответствующими выходами постоянной памяти, группа адресных входов которой подключена к группе выходов третьего блока элементов И и к группе входов первого элемента ИЛИ блока объединения признаков условного перехода, информационные входы п мультиплексоров подключены ко второй группе входов третьего блока элементов И и к группе входов маски устройства, вход чтения постоянной памяти соединен с выходом признака запрета работы блока формирования кодов блока памяти микропрограмм, выход кода проверки анализируемого вектора условий которого соединен со входом дешифратора, первый информационный вход коммутатора соединен с выходом поля адреса блока памяти микрокоманд, выход признака модификации адреса которого соединен с управляюгцим входом коммутатора, второй информационный вход которого соединен с выходом блока элементов ИЛИ, выходы призна1179339 ка микрокоманды и признака безусловного перехода блока памяти микрокоманд соединены соответственно со вторыми входами элемента И блока выделения группы признаков и второго элемента ИЛИ блока выделения груп пы признаков, синхровход устройства подключен ко второму входу третьего элемента И, ко входу элемента

НЕ и к счетным входам первого и второго счетчиков, входы записи которых соединены соответственно с выходами первого и второго элементов И, вторые входы которых

Изобретение относится к вычислительной технике и может найти применение в цифровых вычислительных машинах.

Целью изобретения является сокращение оборудования за счет снижения объема блока памяти микропрограмм.

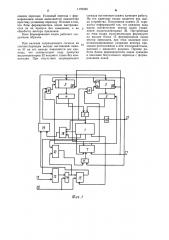

На фиг. 1 представлена функциональная схема микропрограммного устройства управления; на фиг. 2 — схема реализации первого и второго блоков элементов

И; на фиг. 3 — схема реализации блока !

0 элементов ИЛИ; на фиг. 4 — структурная схема блока объединения признаков; на фиг. 5 — сруктурная схема блока выделения группы признаков; на фиг. 6— схема реализации третьего блока элементов

И; на фиг. 7 — структурная схема блока формирования кодов; на фиг. 8 — схема реализации коммутатора.

Микропрограммное устройство управления (фиг. 1) содержит блок 1 памяти 20 микропрограмм, первый 2 и второй 3 счетчики, первый 4 и второй 5 блоки элементов И, блок 6 элементов ИЛИ, триггер 7 первый 8 и второй 9 элементы И, блок 10 объединения признаков условного перехода, третий элемент И 11, блок 12 выделения группы признаков, группу 13 входов признаков, третий блок элементов И 14, блок 15 формирования кодов, элемент НЕ 16, вход

l7 начальной установки, коммутатор 18, сумматор !9. группу 20 входов маски и синхровход 21.

Блок 4(5) элементов И (фиг. 2) содержит п элементов И 22, Блок 6 элементов ИЛИ (фиг. 3) содержит п элементов ИЛИ 23.

Блок 10 объединения признаков содержит (фиг. 4) первый элемент ИЛИ 24, элемент

И 25 и второй элемент ИЛИ 26.

Блок 12 выделения группы признаков (фиг. 5) содержит дешифратор 27, три группы элементов И 28 и группу элементов

ИЛИ 29. 40 соединены с выходом элемента НЕ, выход третьего элемента И соединен со входом синхронизации триггера, информационный вход которого соединен со вторым входом первого блока элементов И и с нулевым выходом триггера, единичный выход которого соединен со вторым входом второго блока элементов И, вход установки в «О» триггера соединен со входами установки в «О» первого и второго счетчиков и является входом начальной установки устройства.

Третий блок 14 элементов И (фиг. 6) содержит группу элементов И 30. Блок 15 формирования кодов (фиг. 7) содержит постоянную память 31 и группу мультиплексоров 32. Коммутатор 18 (фиг. 8) содержит элемент НЕ 33 и группу элементов

2И-ИЛИ 34.

Работа устройства рассматривается на примере выполнения им одной операции.

Перед началом работы программное устройство управления приводят в исходное состояние. Подготовка заключается в подаче в схему сигнала на вход 17 начальной установки. По этому сигналу триггер 7 и счетчики 2 и 3 обнуляются.

Работа устройства начинается с подачи на вход 21 тактовой частоты. По положительному полупериоду первого синхроимпульса происходит увеличение на единицу состояния счетчиков 2 и 3 и опрос блока 10 объединения признаков условного перехода на наличие какого-либо незамаскированного признака. Если признаки отсутствуют, то триггер 7 остается в нуле, т. е. не меняет свого состояния. По нулевому полупериоду синхроимпульса в счетчик 3 разрешается запись, а адрес из счетчика 2 через блок 4 элементов И и блок элементов ИЛИ подается на вход блока 1 памяти микропрограмм, на выходе которого появляется считываемая микрокоманда. Далее, п ри последовательном изменении адресов микрокоманды цикл работы программного устройства управления повторяется.

При необходимости осуществления безусловного перехода работа устройства изменяется следующим образом.

В поле считанной из блока 1 памяти микропрограмм микрокоманды присутствуют уменьшенный на единицу адрес безусловного перехода, признак безусловного перехода и признак управления коммутатором 18. Признак управления коммутатором подается на коммутатор 18 и настраивает его на пропуск уменьшенного на еди1179339 ницу адреса безусловного перехода с выхода блока 1 памяти микропрограмм на вход сумматора 19. На втором входе сумматора 19 при отсутствии признаков перехода или наличии в микрокоманде кода запрета передачи признаков через блок выделения группы признаков находится нулевая информация. Поэтому уменьшенный на единицу адрес безусловного перехода без изменения проходит через сумматор и записывается в счетчик. При нулевом полупериоде тактовой частоты и нулевом состоянии триггера

7 счетчик 3 находится в режиме записи входной информации.

На вход блока 10 объединения признаков условного перехода из поля микрокоманды подан сигнал признака безусловного перехода, который проходит блок 10, и, стробируясь на третьем элементе И 11, передним фронтом положительного полупериода тактовой частоты изменяет состояние триггера 7 на противоположное (в описываемой последовательности действий — единичное состояние) . По переднему фронту положительного полупериода тактовой частоты записанный в счетчик 3 уменьшенный на единицу адрес безусловного перехода увеличивается на единицу и через открытый вследствие единичного состояния триггера 7 второй блок 5 элементов И и блок 6 элементов ИЛИ подается на вход блока памяти микропрограмм. С выхода блока памяти микропрограмм считывается микрокоманда, соответствующая адресу безусловного перехода.

Модифицированный безусловный переход, т. е. переход, когда необходимо осуществить вписывание группы признаков в младшие разряды адреса безусловного перехода, осуществляется следующим образом.

Считанная из блока памяти микропрограммы микрокоманда настраивает блок 15 формирования кодов по входу 3 на пропуск без изменений отмаски рован ного вектора признаков. Отмаскированный вектор признаков складывается на сумматоре 19 с адресом безусловного перехода, который из поля считанной микрокоманды подается через коммутатор 18 на другой вход сумматора 19, Если разряды кода адреса безусловного перехода, соответствующие разрядам вектора признаков, равны нулю, то происходит вписывание вектора признаков в код адуеса безусловного перехода.

В противном случае на выходе сумматора

19 происходит формирование нового адреса безусловного перехода относительно считанного адреса. Дальнейшая работа устройства аналогична описанной при простом безусловном переходе.

Безусловный переход с формированием кодов, т. е. переход, когда в блоке формирователе кодов 15 происходит модификация отмаскированного вектора признаков, осуществляется следующим образом.

Блок формирования кодов получает отмаскированный вектор признаков и вектор маски. При отсутствии запрещающего работу сигнала из блока памяти микропрограмм и при поступлении на соответствующий вход постоянной памяти блока формирования кодов и вектора маски на его выходе появляются коды управления мультиплексорами 32. Настроенные по этим кодам мультиплексоры пропускают вектор признаков так, что все незамаскированные признаки группируются последовательно друг за другом, начиная с младших разрядов, а остальные разряды вектора становятся равными нулю. Например, если вектор маски равен 10101010 («О» соответствует формированию разряда), а разряды вектора признаков обозначены Р7, Рб, Р5, Р4, РЗ, Р2, Pl, PO, то выход блока 15 формирования кодов имеет вектор О, О, О, О, Р7, Р5, РЗ, Pl.

Сформированный таким образом вектор признаков участвует в дальнейшем формировании адреса перехода аналогично описанной работе при модифицированном безусловном переходе. Описанные безусловные переходы можно осуществлять не только относительно адреса, считанного из блока памяти микропрограмм, но и относительно текущего адреса. Для этого необходимо, чтобы микрокоманда настраивала коммутатор 18 на пропуск информации, соответствующей по входу.

Условный переход в устройстве выполняется следующим образом. Считанная из блока памяти микропрограмм микрокоманда настраивает блок 12 выделения группы признаков на пропуск какой-либо группы признаков на вход третьего блока 14 элементов И для маскирования. Отмаскированная группа признаков проходит без изменения настроенный микрокомандой блок

15 формирования кодов и поступает на вход сумматора 19. Отмаскированная группа признаков также поступает блок 10 объе40 динения признаков условного перехода и, если существует хотя бы один незамаскированный признак, на первом входе третьего элемента И 11 появляется сигнал требования осуществления перехода.

На первый вход сумматора 19 с выхода коммутатора 18 в зависимости от его настройки подается либо текущий адрес, либо адрес условного перехода из блока памяти микропрограмм. На выходе сумматора 19 формируется адрес перехода. Он записывается в тот счетчик, в который, в соответствии с состоянием триггера 7, разрешена запись. Дальнейшая работа устройства аналогична работе при безусловном переходе.

Модифицированный условный переход выполняется при равенстве нулю разрядов адреса перехода, в который будет вписываться вектор признаков. В остальном работа устройтсва аналогична работе при ус

1179339 ловном переходе. Условный переход с формированием кодов выполняется аналогично простому условному переходу. Отличие в том, что блок формирователь кодов настраивается не на пропуск без изменения, а на обработку вектора признаков.

Блок формирования кодов работает следующим образом.

При наличии запрещающего сигнала на соответствующем выходе постоянной памяти 31 на его выходе появляются все единицы, что соответствует коду пропуска мультиплексоров 32 входного слова без коммутации. При отсутствии запрещающего сигнала постоянная память начинает работу.

На его адресные входы подается код маски устройства. Постоянная память 31 «прошита» информацией так, что каждому коду маски соответствует вектор кодов управления мультиплексорами 32. Настроенные по этим кодам мультиплексоры формируют на выходе блока 15 формирования . кодов вектор признаков, при этом значения всех незамаскированных разрядов вектора признаков расположены в нем последовательно, начиная с младшего разряда. Пример работы блока формирователя кодов приведен в описании безусловного перехода с формированием кодов.!! 79339

1179339

° ° фиг. 8 авиа. 7

Редактор С. Тимохина

Заказ 5677/51

Составитель Ю. Ланцов

Техред И. Верес Корректор М. Максимишинец

Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий ! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5 филиал ППП «Патент», r. Ужгород, ул. Проектная, 4