Устройство для контроля логических блоков

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее блок памяти, блок записи, два регистра теста, два элемента задержки, формирователь входного сигнала, формирователь стробирующего импульса, и п ячеек (где п - число входоввыходов контролируемого логического блока ) , каждая из которых содержит элемент И, переключатель, элемент сравнения, входной формирователь сигнала, выходной формирователь сигнала и сумматор по модулю два, причем выходы блока памяти соединены с информационными входами блока записи, управляющий вход которого соединен с входом первого элемента задержки и управляющим входом устройства, выход формирователя входного сигнала соединен с первыми входами элементов И ячеек, выход второго элемента задержки соединен с входом формирователя стробирующего импульса, выход которого соединен с управляющими входами элементов сравнения ячеек, первые информационные входы которых соединены с входами соответствующих входных формирователей сигналов, вторые информационные входы элементов сравнения соединены с выходами соответствующих выходных формирователей сигнала, входы которых соединены с соответствующими входами-выходами контролируемого логического блока и первыми контактами соответствующих переключателей ячеек, вторые контакты которых соединены с выходами соответствующих выходных формирователей сигнала, выходы тестов блока записи соединены с информационными входами первого и второго регистров теста, информационные входы сумматоров по модулю два ячеек соединены с соответствующими информационными выходами первого регистра теста, вторые входы элементов И ячеек соединены с соответст . вующими информационными выходами второго регистра тестов, выходы элементов И ячеек соединены с управляющими входами соответствующих сумматоров по модулю два, выходы которых соединены с информационными входами соответствующих входных формирователей сигнала ячеек, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения динамического контроля, оно содержит регистр импульсных воздействий, схему сравнения, генератор тактовых импульсов, i формирователь периода и формирователь пачек импульсов, причем выход генератора СЛ тактовых импульсов соединен с информационным входом формирователя периода, управляющий вход которого соединен с первым информационным выходом регистра импульсных воздействий, информационный выход формирователя периода соединен с информационным входом формирователя пачки импульсов, вход запуска которого соединен с выходом первого элемента задержки и первым входом схемы сравнения, второй вход которой соединен с выходом ;о со Од «Конец записи регистра импульсных воздействий , вход разрещения формирователя пачки импульсов соединен с вторым информационным входом регистра импульсных воздействий , третий информационный выход которого соединен с управляющим входом формирователя входного сигнала, информационный выход которого соединен с информационным выходом формирователя пачки импульсов , выход конца формирования которого соединен с входом сброса регистра импульсных воздействий и информационным входом второго элемента задержки, управляющий вход которого соединен с выходом схемы сравнения, информационные входы регистра импульсных воздействий соединены с выходами микрокоманд блока записи.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 G 06 F 11 16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ;:

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 371 3417/24-24 (22) 10.02.84 (46) 15.09.85. Бюл. № 34 (72) Ю. В. Созин, В. П. Туробов и В. А. Нерубацкий (53) 681.3 (088.8) (56) Авторское свидетельство СССР № 390526, кл. G 06 F 11/26, 1971.

Авторское свидетельство СССР № 888127, кл. G 06 F 11/16, 1980. (54) (57) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

ЛОГИЧЕСКИХ БЛОКОВ, содержащее блок памяти, блок записи, два регистра теста, два элемента задержки, формирователь входного сигнала, формирователь стробирующего импульса, и п ячеек (где и — число входов— выходов контролируемого логического блока), каждая из которых содержит элемент И, переключатель, элемент сравнения, входной формирователь сигнала, выходной формирователь сигнала и сумматор по модулю два, причем выходы блока памяти соединены с информационными входами блока записи, управляющий вход которого соединен с входом первого элемента задержки и управляющим входом устройства, выход формирователя входного сигнала соединен с первыми входами элементов И ячеек, выход второго элемента задержки соединен с входом формирователя стробирующего импульса, выход которого соединен с управляющими входами элементов сравнения ячеек, первые информационные входы которых соединены с входами соответствуюш их входных формирователей сигналов, вторые информационные входы элементов сравнения соединены с выходами соответствующих выходных формирователей сигнала, входы которых соединены с соответствующими входами — выходами контролируемого логического блока и первыми контактами соответствующих переключателей ячеек, вторые контакты которых соединены с выходами соответствующих выходных формирователей сигнала, выходы тестов блока записи соединены с информационными входами первого и второго регист„„Я0„„1179346 A ров теста, информационные входы сумматоров по модулю два ячеек соединены с соответствующими информационными выходами первого регистра теста, вторые входы элементов И ячеек соединены с соответствующими информационными выходами второго регистра тестов, выходы элементов И ячеек соединены с управляюшими входами соответствующих сумматоров по модулю два, выходы которых соединены с информационными входами соответствующих входных формирователей сигнала ячеек, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения динамического контроля, оно содержит регистр импульсных воздействий, схему сравнения, генератор тактовых импульсов, формирователь периода и формирователь I пачек импульсов, причем выход генератора тактовых импульсов соединен с информади- Щ онным входом формирователя периода, управляющий вход которого соединен с пер- l вым информационным выходом регистра импульсных воздействий, информационный выход формирователя периода соединен с информационным входом формирователя пачки импульсов, вход запуска которого >„ф, соединен с выходом первого элемента задержки и первым входом схемы сравнения, второй вход которой соединен с выходом

«Конец записи» регистра импульсных воздей- (© ствий, вход разрешения формирователя пач- фф ки импульсов соединен с вторым инфор-,ф мационным входом регистра импульсных воздействий, третий информационный выход которого соединен с управляющим входом формирователя входного сигнала, информационный выход которого соединен с информа- а ционным выходом формирователя пачки им- Ф пульсов, выход конца формирования которого соединен с входом сброса регистра импульсных воздействий и информационным входом второго элемента задержки, управляющий вход которого соединен с выходом схемы сравнения, информационные входы регистра импульсных воздействий соединены с выходами микрокоманд блока записи.

1179346

Изобретение относится к автоматике и вычислительной технике.

Цель изобретения — расширение функциональных возможностей путем обеспечения динамического контроля.

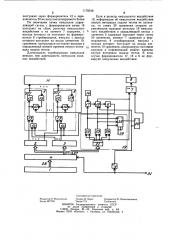

На чертеже показана функциональная схема устройства для контроля логических блоков.

Устройство для контроля логических блоков содержит блок 1 памяти, регистры 2 и 3 теста, блок 4 записи, элемент 5 задержки, формирователь 6 входного сигнала, элемент 7 задержки, формирователь 8 стробирования, ячейки 9, элемент 10 сравнения, контролируемый логический блок 11, формирователь 12 входного воздействия, формирователь 13 выходного воздействия, элемент

И 14, элемент 15 сложения по модулю два, генератор 16 тактовых импульсов, формирователь 17 периода, формирователь 18 пачки импульсов, регистр 19 импульсных воздействий, схему 20 сравнения, дешифратор 21, триггеры 22 — 24, элемент 25 сравнения, выходы 26 тестов блока записи, выходы 27 микрокоманд блока записи, выходы 28 блока памяти, шину 29 эталона, переключатель 30 и вход 31 пуска устройства.

Устройство работает следующим образом.

Контролируемый блок 11 имеет и контактов, каждый из которых может быть входным или выходным, что фиксируется соответственно замкнутым или разомкнутым положением переключателя 30. На каждый контакт может быть подана информация потенциальная или импульсная.

По сигналу управления с входа 31 устройства тестовая информация из блока 1 памяти через блок 4 записи поступает в регистр 3 теста и регистр 19 импульсного воздействия.

Регистр 3 теста определяет какой сигнал будет подан на вход контролируемого блока в данном тесте: «1» соответствует импульсному сигналу, «О» — потенциальному.

Логический нуль должен присутствовать на всех управляющих разрядах теста, соответствующих выходам логического устройства и незадействованным контактам.

Информационные разряды с регистра 2 теста задают логический уровень, подаваемый на вход контролируемого блока, если данный контакт этого блока потенциальный, импульсное воздействие — если контакт импульсный и эталонную информацию— если контакт выходной.

Если на выходе информационного разряда регистра 2 присутствует «О» то полярность импульса на выходе элемента 15 сложения по модулю два совпадает с полярностью входного импульса, если на выходе разряда имеется «1», то полярность импульса на выходе элемента сложения по модулю два инверсна входному импульсу.

10 l5

Информация с блока 4 записи поступает на информационные входы регистра 19 импульсных воздействий и через дешифратор

21 импульсных воздействий записывается в соответствующие триггеры периода 22, пачки

23, длительности 24. Информация с выходов триггеров 22 — 24 поступает на соответствующие формирователи 17, 18 и 6 и на эле2S мент 25 сравнения, который служит для регистрации наличия или отсутствия информации об импульсных воздействиях в триггерах 22 — 24. При наличии такой информации элемент 25 сравнения закрывает схему 20 сравнения, а при отсутствии информации открывает ее. Управляющий вход регистра импульсных воздействий 19 является установочным входом триггеров 22 — 24.

Ю

Логические сигналы с регистра 2 теста через элемент 15 сложения по модулю два поступают на входы формирователя 12 и элемента 10 сравнения. Если переключатель

30 разомкнут, то на второй вход элемента 10 сравнения поступает логический уровень с выхода контролируемого блока. Если переключатель 30 замкнут, то через формирователь 12 сформированный логический уровень поступает на вход контролируемого блока и через формирователь 13 на второй вход элемента 10 сравнения.

Регистр 19 импульсного воздействия имеет три разряда, первый из которых является управляющим для формирователя длительности периода, второй — для формирователя пачек импульсов, а третий — для формирователя входного воздействия.

Формирователь периода 1? по сигналу с регистра импульсного воздействия 19 формирует из импульсов с задающего генератора 16 импульсы с необходимым периодом следования, которые поступают на формирователь 18 пачек импульсов. Схема

20 сравнения закрыта управляющим выходом регистра 19 импульсного воздействия.

Через промежуток времени, определяемый элементом 5 задержки, на управляющий вход формирователя 18 пачек импульсов поступает сигнал, который разрешает формирование пачки импульсов с периодом следования, определяемым формирователем 17 периода. Величина пачки определяется управляющим сигналом с регистра 19 импульсного воздействия. Пачка импульсов поступает на формирователь 6 входных сигналов, где происходит формирование длительности импульсов с длительностью, заданной с регистра импульсного воздействия. Импульсное воздействие подается на входы элементов И 14 и проходит лишь через те элементы И 14, на управляющих входах которых присутствует «1». Далее импульс поступает на вход элемента 15 сложения по модулю два, затем импульсы необходимой полярности с выхода элемента 15

11 з поступают через формирователь !2 и переключатель 30 на вход контролируемого блока.

По окончании пачки импульсов управляющий сигнал с формирователя пачек 18 поступает на сброс регистра импульсного воздействия и на элемент 7 задержки, с выхода которого он поступает на формирователь 8 стробирования, импульс с выхода которого поступает на входы элементов 10, сравнения, контролируя состояние выходов в определенный момент времени внутри интервала подачи тестов.

Длительность стробирующих импульсов меньше, чем длительность импульсов входных воздействий.

79346

Если в регистр импульсного воздействия

19, информация об импульсном воздействии внутри интервала подачи тестов не записана, то схема 20 сравнения открыта управляющим выходом регистра 19 импульсного воздействия и управляющий сигнал с элемента 5 задержки проходит через схему

20 сравнения, элемент 7 задержки и формирователь 8 стробирования, импульс с выхода которого поступает на входы элементов 10 сравнения, контролируя состояние выходов в оп ределенный момент времени внутри интервала подачи тестов. В этом случае формирователи 17, 18 и 6 не формируют импульсные воздействия.

Редактор Л. Пчелннская

Заказ 5677/51

Составитель Сиротская

Техред И. Верес Корректор М. Макснмишинец

Тираж 710 Подлисное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <Патент>, г. Ужгород, ул. Проектная, 4