Устройство для ввода-вывода информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ИНФОРМАЦИИ, содержащее первый, второй и третий регистры, формирователь импульсов, триггер, терминалы, первьй, второй и третий элементы И, дешифратор, первый элемент ИЛИ, первую группу элементов И, первые входы которых соединены с выходом формирователя импульсов, первым входом второго элемента И и вторым входом первого элемента И, первый вход которого соединен с первым выходом триггера, второй выход которого является первым выходом устройства, первый вход второго регистра соединен с вторым входом триггера и является первым входом устройства, выходы группы второго регистра являются выходами группы устройства, входы первого регистра являются входами первой группы устройства, второй вход второго элемента И соединен с вторым выходом дешифратора, первый выход которого является вторым выходомустройства, выходы элементов И первой группы соединены с первыми входами соответствующих терминалов , выходы которых соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с вторым входом второго регистра , о т л и ч а ю щ е е с я тем, что, с целью упрощения и повышения быстродействия устройства, оно содержит второй элемент ИЛИ, вторую группу элементов И и элемент НЕ, выход которого соединен с вторым входом третьего элемента И, первый и третий входы которого соответственно соединены с первым и вторым входами второго элемента И, третий г вход которого соединен с входом элемента НЕ и является вторым входом устройства, выход второго элемента И соединен с первым входом второго элемента ИЛИ и входом третьего регистра, входы группы которого являются входами второй группы устройства , выход третьего элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен с третьим входом второго регистра, четвертый вход и выход которого соединены (Соответственно с первым и вторым входами дешифратора, выходы треть его регистра соединены с вторыми входами соответствующих элементов И первой группы, вторые входы терминалов соединены соответственно с выходами элементов И второй группы, первые вхо ды которых соединены с соответствующими выходами первого регистра, вторые входы элементов И второй группы соединены с выходом, первого элемента И и первым входом триггера.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (l 9) (11) (51) 4 G 06 F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3718533/24-24 (22) 27.03.84 (46) 15.09.85. Бюл. N 34 (72) А.M. Заяц, О.M. Губин и С.А. Матвеев (53) 681.327.21(088.8) (56) Авторское свидетельство СССР № 693362, кл. С 06 F 3/04,1979.

Авторское свидетельство СССР № 972494, кл. G 06 F 3/04, 1982. (54)(57) УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ИНФОРМАЦИИ, содержащее первый, второй и третий регистры, формирователь импульсов, триггер, терминалы, первый, второй и третий элементы И, .дешифратор, первый элемент ИЛИ, ервую группу элементов И, первые вхо" ды которых соединены с выходом формирователя импульсов, первым входом второго элемента И и вторым входом первого элемента И, первый вход которого соединен с первым выходом триггера, второй выход которого является первым выходом устройства, первый вход второго регистра соединен с вторым входом триггера и является первым входом устройства, выходы группы второго регистра являются.выходами группы устройства, входы первого регистра являются входами первой группы устройства, второй вход второго элемента И соединен с вторым выходом дешифратора, первый выход которого является вторым выходом устройства, выходы элементов И первой группы соединены с первыми входами соответствующих терминалов, выходы которых соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с вторым входом второго регистра,. о т л и ч а ю щ е е с я тем, что, с целью упрощения и повышения быстродействия устройства, оно содержит второй элемент ИЛИ, вторую группу элементов И и элемент НЕ, выход которого соединен с вторым входом третьего элемента И, первый и третий входы которого соответственно соединены с первым и вторым входами второго элемента И, третий Ck вход которого соединен с входом элемента НЕ и является вторым входом устройства, выход второго элемента И соединен с первым входом второго элемента ИЛИ и входом третьего регистра, входы группы которого являются входами второй группы устройства, выход третьего элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен с третьим входом второго регистра четвертый вход и выход которого соеди нены <соответственноэ с первым и вторым входами дешифратора, выходы треть его регистра соединены с вторяк входами соответствующих элементов И первой группы, вторые входы терминалов соединены соответственно с выходами элементов И второй группы, первые входы которых соединены с соответствующими выходами первого регистра, вторые входы элементов И второй группы соединены с выходом первого элемента И и первым входом триггера.

1179356

Изобретение относится к автоматике и вычислительной технике и может быть использовано для организации обмена информацией в системах коллективного пользования вычислительными ресурсами и в информационно-поисковых системах.

Режим чтения информации с терминалов может быть организован двумя 5 способами: последовательное чтение информации со всех терминалов 5 и приоритетное чтение информации с одЦель изобретения — упрощение устройства и повышение его быстродействия °

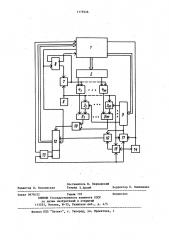

На чертеже представлена структурная схема устройства.

Устройство содержит процессор 1, первый регистр 2, элементы И. 3 первой

3 и второй 4 групп, терминалы 5, фор-15 мирователь 6 импульсов, первый элемент И 7, триггер 8, третий регистр 9, первый элемент ИЛИ 10, второй элемент

И 1 1, второй регистр 12, дешифратор

13, элемент НЕ 14, третий элемент

И 15 и второй элемент ИЛИ 16.

Предлагаемое устройство работает следующим образом.

Перед началом работы в.регистрах

2, 9 и 12 и триггере 8 записан нулевой код. Процессор 1 согласно программе устанавливает либо режим чтения, либо режим записи информации.

В режиме записи информации в терминалы 5 процессор 1 передает первую 30 информационную посылку в регистр 2, в котором i-я ячейка закреплена за

i-ым терминалом 5. Затем процессор 1 посылает сигнал, переводящий триггер 8 в состояние, разрешающее прохождение тактовых импульсов с формирователя 6 через элемент И 7 на входы элементов И группы 4. В результате чего информация с регистра 2 через соответствующие элементы И группы 4 40 поступает в соответствующие терминалы 5, В то же время импульс с выхода элемента И 7 поступает на вход триггера 8 и устанавливает его в нулевое состояние, запрещая прохождение тактовых импульсов через элемент

И 7, а с другого выхода триггера 8 формируется сигнал прерывания по записи, по которому процессор 1 выставляет в регистр 2 новую посылку ннфор-у) мации. Операции продолжаются до момента снятия режима записи информации. ного терминала 5, т.е. чтение информации полностью с одного терминала 5, В первом случае с выходной шины процессора 1 в регистр 9 заносится распределенный код 0000 ... 01, т.е, во все разряды регистра, кроме

n-ro.,çàíoñÿòñÿ нули, а в и-ый разJ ряд — единица.

Регистр 12 устройства устанавливается в исходное состояние, при котором все его кроме первого, разряды, включая и маркерный, устанавливаются в нулевое состояние, а в первый разряд регистра 12 записывается маркер, значение которого равно единице. Так как в маркерном разряде регистра 12 записан ноль, то с выхода дешифратора 13 снимается сигнал, разрешающий прохождение тактовых импульсов с формирователя 6 через элемент И 11 ° Так как режим чте" ния информации организуется последовательно со всех терминалов 5, то на вход элемента И 11 поступает единичный сигнал от процессора 1. Этот сигнал разрешает прохождение тактовых импульсов с формирователя 6 на вход регистра 9.

С приходом первого тактового импульса содержимое и-го разряда регистра 9 переписывается в его первый разряд, а код маркера переписывается из первого разряда регистра 12 во второй, так как с выхода элемента

И 11 тактовый импульс через элемент

ИЛИ 16 заводится на вход регистра 12, С выхода первого разряда регистра 9 единичный сигнал поступает на вход первого элемента И группы 3, на другой вход которого поступает импульс с формирователя 6. В результате управляющий импульс с выхода первого элемента И 3 группы поступает на вход соответствующего терминала 5.

Код символа с терминала 5 считывается и через элемент ИЛИ 10 записывается в первый разряд регистра 12.

На очередном шаге с приходом следующего тактового импульса с формирователя 6 происходит сдвиг кодов, записанных в регистрах 9 и 12 и код символа считывается с второго терминала и записывается .во второй разряд регистра 12 и т.д.

Операция считывания с каждого терминала 5 продолжается до момента появления в последующем (маркерном) (и+1)-м разряде регистра 12 кода марз 1179 кера, т.е, тогда, когда последовательно будет прочитана информация со всех и терминалов 5, начиная с первого терминала 5.

Так как код маркера Равен единице, то с инверсного выхода дешифратора 13 снимается сигнал, запрещающий прохождение тактовых импульсов через элемент И 11, а с выхода дешифратора

13 формируется сигнал прерывания, ко- 10 торый поступает в процессор 1. Содержимое регистра 12 поступает в процессор 1. Операция чтения продолжается после поступления кода установки в начальное состояние регистра 12 и 15 распределенного кода в регистр 9.

Если необходимо считать информацию полностью с одного терминала, напри-мер с i-го (второй случай), то в регистр 9 заносится код, где в i-м раз- 20 ряде единица, а в остальных ноль. Регистр 12 по первому входу устройства устанавливается в исходное состояние, как и в первом случае, На вход элемента И 11 поступает 25 нулевой сигнал, запрещающий прохождение тактовых импульсов с формирователя 6 на вход регистра 9,.

Так как сдвиг распределенного кода в регистре 9 не осуществляется, то разрешающий сигнал, равный единице, на время чтения информации с i-го терминала поступает на вход i-го элемента И 3 группы.

С приходом тактового импульса с формирователя 6 информация (коды символов) с i-ro терминала 5 последовательно записывается в регистр 12, при этом сдвиг информации в регистре .12 осуществляется сигналом, поступающим 4О

356 4 от формирователя 6 через элемент

И 15, с выхода элемента ИЛИ 16.

Как только в маркерном разряде регистра 12 появляется единица, то с выхода дешифратора 13 снимается сигнал, запрещающий прохождение тактовых импульсов через элемент И l5 а с другого выхода дешифратора формируется сигнал прерывания, который поступает в процессор 1, Содержимое регистра 12 поступает в процессор.

Если необходимо продолжить чтение информации с i-ro терминала, то регистр 12 переводится в исходное состояние и процесс повторяется, Операция чтения информации осуществляется до момента снятия режима чтения, В известном устройстве в режим записи информации в терминалы запись одной посылки информации для всех терминалов осуществляется последоьательно в каждый терминал, начиная с первого и до n-ro, что приводит к непроизводительным простоям I åðìèналов.

В предлагаемом устройстве запись одной посылки информации для всех терминалов производится одновременно, так как каждый терминал имеет свои независимые цепи и систему записи.

Таким образом, предлагаемое устройство не только обеспечивает увеличение быстродействия на 507 в режиме записи, но.и при любом количестве терминалов позволяет сокращать оборудование в 1,4 раза, что позволяет уменьшить количество функциональных связей, т.е. упростить устройство.

1179356

Составитесь В. Верховский

Техред З.Палий

Корректор Л. Пилипенко

Редактор Л. Пчелинская

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 5678/52 Тираж 710

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5