Аналоговое делительное устройство

Иллюстрации

Показать всеРеферат

АНАЛОГОВОЕ .ЦЕЛИТЕЛЬНОЕ УСТРОЙСТВО , содержащее компаратор, первый вход которого является входом сигнала-делимого устройства, соединенные последовательно ключевой элемент и блок памяти, выход которого является выходом устройства, выход компаратора подключен к управляющему входу ключевого элемента, о т л ичающееся тем, что, с целью повышения быстродействия, в него введены элемент с управляемым сопротивлением , выполненный на транзисторе , первый, второй и третий масштабные резисторы, причем ко второму входу компаратора подключены первый вывод первого масштабного резистора и эмиттер транзистора,коллектор которого соединен с первым выводом второго масштабного резистора и с выходом компаратора, общая шина которого подключена к шине нулевого потенциала , ко второму выводу первого штабного резистора и к первому выво (Л ду третьего масштабного резистора, второй вывод которого соединен со вторым выводом второго масштабного резистора и с входом ключевого элемента , база транзистора является входом сигнала-делителя устройстЬа. ;0 со

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (S l) 4

ОПИСАНИЕ ИЗОБРЕТ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 ОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3712245/24-24 (22) 07.03.84 (46) 15.09.85. Бюл. ¹ 34 (72) И.В.Кораблев, E.È.Глинкин, В.В.Тен, Б.И.Герасимов и Г.А.Гальцова (71) Московский ордена Трудового

Красного Знамени -институт химического машиностроения (53) 681.335(088.8) (56) Авторское свидетельство СССР

N- 547780, кл. G 06 G 7/16, 1975.

Авторское свидетельство СССР № 834712, кл. G 06 G 7/16, 1979. (54)(57) АНАЛОГОВОЕ ДЕЛИТЕЛЪНОЕ УСТРОЙСТВО, содержащее компаратор, первый вход которого является входом сигнала-делимого устройства, соединенные последовательно ключевой элемент и блок памяти, выход которого является выходом устройства, выход компаратора подключен к управляющему

„„SU„„1179379 А входу ключевого элемента, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены элемент с управляемым сопротивлением, выполненный на транзисторе, первый, второй и третий масштабные резисторы, причем ко второму входу компаратора подключены первый вывод первого масштабного резистора и эмиттер транзистора, коллектор которого соединен с первым выводом второго масштабного резистора и с выходом компаратора, общая шина которого подключена к шине нулевого потенциала, ко второму выводу первого масштабного резистора и к первому выводу третьего масштабного резистора, второй вывод которого соединен со вторым выводом второго масштабного резистора и с входом ключевого элемента, база транзистора является входом сигнала-делителя устройства.

20 где U напряжение в плече а в установившемся режиме, (3) Т= Т-К, 30 где Т = КС„ постоянная времени переходного процесса; сопротивление плеча моста; межэлектродная емкость плеча;

CN о

ЦВ = U, . а(), (1) 35

Pez. 1

BHHHHH Заказ 9679/ЗЗ Зиоаи 710 Поиписиоа и "ззаиз. -"., ".â"-.ы--Б,.=

1 1179

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

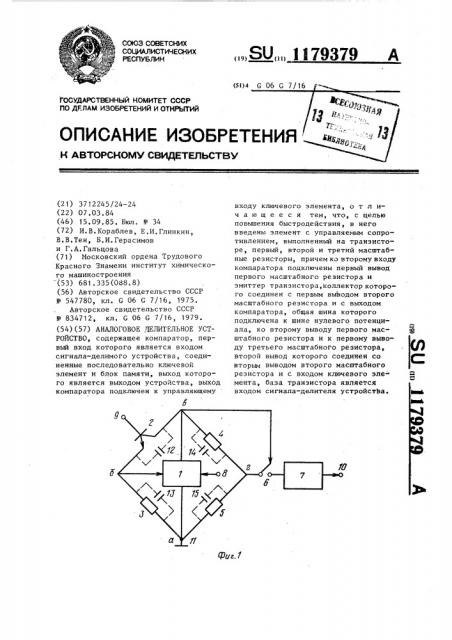

Цель изобретения — повышение 5 быстродействия устройства, На фиг. 1 показана функциональная схема предложенного аналогового делительного устройства; на фиг, 2— временные диаграммы сигналов. 10

Устройство содержит компаратор 1, элемент с управляемым сопротивлением, 1 выполненный на транзисторе 2, первый, второй и третий масштабные резисторы

3-5, ключевой элемент 6, блок 7 па- 15 мяти, вход 8 сигнала-делимого, вход

9 сигнала-делителя, выход 10, шину 11, нулевого потенциала, межэлектродные емкости 12-15.

Аналоговое делительное устройство работает следующим образом.

Первый, второй и третий масштабные резисторы 3-5 и управляемый транзистор 2 (может быть использован управляемый полевой транзистор) образуют мост.

При включении на выходе компаратора 1 появляется напряжение логической единицы (фиг. 2а), которое поступает в диагональ питания as коста. Напряжения в плечах мб (фиг, 2б) и аъ (фиг. 2в) возрастают за время Г„ (i — число переключений) соответственно до значений где U — напряжение сигнала-дели-6 теля; й(Y1" функция, описывающая переходной процесс и U за счет переходных процессов, f обусловленных яежэлектродными емкостями 12-15.

При достижении сигналом U значеВ ния сигнала-делимого U, компаратор 1 переключаетсяи на его выходе формируется напряжение логического нуля (фиг. 2б), При этом напряжение в плечах а и ota моста уменьшается до ,куля за тот же интервал времени.

Одновременно напряжение с плеча аъ моста поступает в блок 7 памяти через ключевой элемент 6, который управляется импульсом, сформированным на выходе компаратора 1 в момент переключения. При срабатывании ключевого элемента 6 на плече аъ моста появляется напряжение t

Ug g=U-ф, (2)

Описанный цикл работы повторяется.

Информация в блоке 7 памяти изменяется только после срабатывания ключевого элемента 6.

Время одного. цикла равно

К 1.

Поскольку межэлектродная емкость плеча не превосходит нескольких десятых долей пикофарады, то быстродействие является очень высоким.