Устройство для контроля аналоговых перемножителей

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5|)4 С 0 6 ф р р 4 FOP; j ст @

|З,"

ИЙ:,.;,„-„"

ОПИСАНИЕ ИЗОБРЕТЕ

К ASTOPCHOIVlY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3714700/24-24 (22) 13, 03, 84 (46) 15.09.85. Бюл. ¹ 34 (72) В.П.Волков (71) Ордена Ленина институт проблем управления (53) 681.335(088.8) (56) Бердяков Г.И. и др. Методы контроля аналоговых вычислительных машин.

М.: Машиностроение, 1978, с. 73, рис. 25.

Мироновский Л.А. Функциональное диагностирование динамических систем. — Автоматика и телемеханика, 1980, ¹ 8, с. 99 рис. 3. (547(57) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

АНАЛОГОВЫХ ПЕРЕМНОЖИТЕЛЕЙ, содержащее компаратор, первый вход которого подключен к выходу контролируемого аналогового перемножителя, являющемуся

„„Я0„„11793 0 выходом устройства, индикатор, о тл и ч а ю щ е е с я тем, что, с цулью упрощения, в него введены первый и второй нуль-органы, элемент ИЛИ, сумматор по модулю два и триггер, причем входы первого и.второго нульорганов .соединены с первым и вторым входами контролируемого аналогового перемножителя, выходы первого и вто рого нуль-органов подключены к первому и второму входам элемента ИЛИ соответственно, выход элемента ИЛИ соединен с первым входом сумматора по модулю два, второй вход которого соединен с выходом компаратора, выход сумматора по модулю два подключен к установочному входу триггера,, выход которого соединен с входом индикатора, вход сброса триггера подключен к входу установки в исходное состояние устройства.

179380

Компаратор

0 1 1

О 0

1 1

1 О

1 О

1 О

О 1

1 О

1 1

Выход сумматора по модулю два

0 1

0 О

Индикатор Отказк

"Нормально"

Составитель О. Отраднов

Редактор И. Ковальчук Техред М.Кузьма Корректор В. Бутяга

Подписное

Тираж 710

Заказ 56?9/53

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

1 1

Изобретение относится к устройст вам контроля перемножителей электрических сигналов и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения — упрощение устройства.

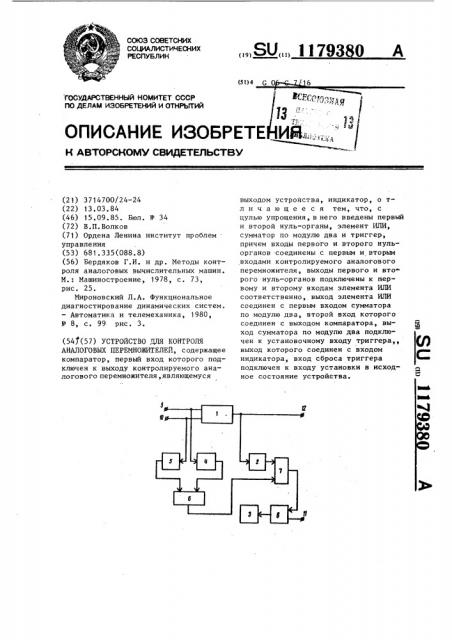

На чертеже показана функциональная схема устройства. Схема содержит контролируемый аналоговый перемножитель 1, компаратор 2, индикатор 3, первый и второй нуль-органы 4 и 5, элемент ИЛИ 6, сумматор 7 по модулю два, триггер 8, входы первого и второго сигналов- сомножителей 9 и 10, вход 11 установки в исходное состояние, выход 12.

Устройство работает следующим образом.

После подачи питания сигналом с входа 11 триггер 8 устанавливается в нормальное состояние, в состояние наблюдения за исправностью перемножителя 1, который выполняет обычные функции — перемножение входных сигналов. Режимы компаратора 2, первого

Первый нуль-орган О О 1

Второй нуль-.орган О 1 О

Выход элемента ИЛИ О 1 1 и второго нуль"органов 4 и 5 подобраны таким образом, что, если их входной сигнал равен нулю, то на выходе появляется сигнал логической единицы, если же входной сигнал отличен от нуля, то на выходе будет логический нуль. Контроль исправности перемножителя 1 происходит только в момент прохождения входными и выходными сигналами значения нуля. Момент прохождения нуля фиксируется компаратором 2, первым и вторым нуль-органами 4 и 5, обрабатывается элементом ИЛИ 6 и сумматором 7 по модулю два в соответствии с таблицей истинности, и в случае неисправности перемножителя 1 на входе триггера 8 вырабатывается сигнал, который переводит триггер 8 в состояние, при котором индикатор 3 сигнализирует об отказе. Минимальная длительность импульса запуска триггера 8 выбирается таким образом, чтобы предотвратить ложное срабатывание индикатора 3, которое может быть вызвано переходными процессами в цифровых элементах, а также шумами и помехами. !