Преобразователь частоты в код

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД, содержащий генератор тактовых импульсов, распределитель импульсов, четыре cинxpo изатора, два элемента ИЛИ, реверсивный счетчик , коммутатор, два элемента задержки и два элемента И, выход генератора тактовых импульсов соединен с входом распределителя импульсов , первый, второй, третий и четвертый выходы которого подключены к первьм входам первого, второго , третьего и четвертого синхронизаторов соответственно, выходы первого и второго синхронизаторов через первый элемент ИЛИ соединены с суммирующим входом реверсивного счетчика, выходы третьего и четвертого синхронизаторов через второй элемент ИЛИ соединены с вычитающим входом реверсивного счетчика , выходы которого через коммутатор подключены к выходной шине , пятый выход распределителя импульсов соединен с управляющим входом коммутатора, установочный вход реверсивного счетчика подключен к шине начальной установки, первая входная шина подключена к первому входу первого элемента И выход которого соединен с вторым ; входом первого синхронизатора и чег рез первый элемент задержки - с вторым входом третьего синхронизатора , вторая входная шина подключена к первому входу второго элемента И, выход которого соединен свторым входом второго элемента задержки , отличающийс я тем, что, с целью расширения функциональных возможностей, в неi го введены регистр, триггер, третий , четвертый, пятый и шестой эле (Л менты И и третий и четвертый элементы ИЛИ, первая управляющая шина соединена с первым входом регистра , первый выход которого подключен к второму входу первого элемента И, вторая управляющая шина соединена с вторым входом регистра второй выход которого подключен к со втopo ry входу второго элемента И, S выход которого соединен с первыми входами третьего и шестого элеменСП тов И, выход второго элемента задержки подключен к первым входам четвертого и пятого элементов И, третья управляющая шина соединена с установочным входом триггера, прямой выход которого подключен к вторым входам третьего и пятого элементов И, четвертая управляющая шина соединена с входом сброса триггера, инвертирующий выход которого подключен к вторым входам четвертого и шестого элементов И, вы

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5 )4 Н 03 M 5/10 (21) 3719966/24-24 (22) 04.04.84 (46) 15.09.85. Бюл. Р 34 (72) С.Л. Сироткин, В.В. Клименко, В.А. Гаманко и А.Н. Коньков (71) Таганрогский радиотехнический институт им. В.Д. Калмыкова (53) 681.325 (088.8) (56) Авторское свидетельство СССР

М 364095, кл. Н 03 К 13/20, 26.04.71.

Авторское свидетельство СССР

N - 1112551, кл. Н 03 К 13/20, 17.0б.83. (54)(57) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ

В КОД, содержащий генератор тактовых импульсов, распределитель импульсов, четыре синхронизатора, два элемента ИЛИ, реверсивный счетчик, коммутатор, два элемента задержки и два элемента И, выход генератора тактовых импульсов соединен с входом распределителя импульсов, первый, второй, третий и четвертый выходы которого подключены к первым входам первого, второго, третьего и четвертого синхронизаторов соответственно, выходы первого и второго синхронизаторов через первый элемент ИЛИ соединены с суммирующим входом реверсивного счетчика, выходы третьего и четвертого синхронизаторов через второй элемент ИЛИ соединены с вычитающим входом реверсивного счетчика, выходы которого через коммутатор подключены к выходной шине, пятый выход распределителя импульсов соединен с управляющим входом коммутатора, установочный вход реверсивного счетчика подклю„„SU„„1179545 А чен к шине начальной установки, первая входная шина подключена к первому входу первого элемента И выход которого соединен с вторым: входом первого синхронизатора и че рез первый элемент задержки — с вторым входом третьего синхронизатора, вторая входная шина подключена к первому входу второго элемента И, выход которого соединен с вто" рым входом второго элемента задержки, о т л и ч а ю щ и й— с я тем, что, с целью расширения функциональных возможностей, в него введены регистр, триггер, третий, четвертый, пятый и шестой элементы И и третий и четвертый элементы ИЛИ, первая управляющая шина соединена с первым входом регистра, первый выход которого подключен к второму входу первого элемента И, вторая управляющая шина соединена с вторым входом регистра второй выход которого подключен к второму входу второго элемента И, выход которого соединен с первымй входами третьего и шестого элементов И, выход второго элемента задержки подключен к первым входам четвертого и пятого элементов И, третья управляющая шина соединена с установочным входом триггера, прямой выход которого подключен к вторым входам третьего и пятого элементов И, четвертая управляющая шина соединена с входом сброса триггера, инвертирующий выход которого подключен к вторым входам четвертого и шестого элементов И, вы"

1179545 ходы третьего и четвертого элементов И через третий элемент ИЛИ соединены с вторым входом второго синхронизатора, выходы пятого и

Изобретение относится к измерительной технике и может быть использовано для связи вычислительньгх машин с объектами управления, для обработки сигналов от частотных датчиков (в том числе от струнных акселерометров) в системах стабилизации частоты.

Целью изобретения является расширение функциональных возможностей преобразователя путем обеспечения дополнительного режима преобразования суммы частот.

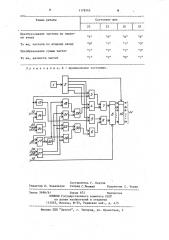

На чертеже изображена. структурная схема преобразователя.

Преобразователь содержит генератор 1 тактовых импульсов, раснределитель 2 импульсов, синхронизаторы 3 — 6, элемент ИЛИ 7, реверсивный счетчик 8, элемент ИЛИ 9, коммутатор 10, выходную шину 11, шину 12 начальной установки, первую входную шину 13, элемент И 14, элемент 15 задержки, вторую входную шину 16, элементы И 17-19, элемент 20 задержки, элементы И 21, 22, первую управляющую шину 23, регистр 24, вторую и третью управляющие шины 25 и 26, триггер 27, четвертую управляющую шину 28, элементы ИЛИ 29 и 30.

Устройство работает следующим образом.

При отсутствии сигналов на управляющих шинах 23, 25, 26 и 28 производится начальная установка реверсивного счетчика 8 по шине 12, причем длительность сигнала установки должна быть не меньше времени задержки в элементах 15 и 20 за-, держки для их полной очистки.. Затем комбинацией сигналов на шинах

23, 25, 26 и 28 устанавливается со" ответствующий режим работы преобра" зователя (см. таблицу). шестого элементов И через четвертый элемент ИЛИ подключены к второму входу четвертого синхронизатора.

При преобразовании частоты в код по первому входу входная частота подается на шину 13, сигнал с первой управляющей шины 23 подается на первый вход регистра 24, сигнал на второй управляющей шине 25 соответствует логическому "0" и, следовательно, логический "0" будет на втором выходе регистра 24.

Поэтому открыт элемент И 14, закрыт элемент И 17 и независимо от состояния триггера 27 импульсы входной частоты через синхронизатор 3 и элемент ИЛИ 7 поступают на суммирующий exop peaepcnaHoro счетчика 8 и они же через элемент

15 задержки, синхронизатор 5 и элемент ИЛИ 9 — на вычитающий вход реверсивного счетчика 8, на выходе ко" торого через время, равное времени распространения сигнала в элементе 15 задержки, установится код числа, равного целой части произведения входной частоты на время

25 распространения сигнала в элементе задержки. Знак кода определяется состоянием двух знаковых разрядов, выделенных для этой цели, т.е. выходной код является модифици30 рованным дополнительным кодом.

Преобразование частоты в код по второму входу отличается от преобразования по первому входу тем, что в этом случае входная частота подается на шину 16» сигнал, соответствующий логической "l" подается на шину 25 и на шину 26. При этом закрыт элемент И 14 и открыт элемент И 17 и, так как на пря40 мом выходе триггера 27 состояние логической "1", открыты элементы И 18 22. Импульсы входной частоты с элемента И 17 поступают через элемент И 18, элемент ИЛИ 29, синхронизатор 4 и элемент ИЛИ 7 на суммирующий вход реверсивного счетчика 8, и они же через элемент

20 задержки, элемент И 22, элемент ИЛИ 30, синхронизатор 6, элемент ИЛИ 9 — на вычитающий вход реверсивного счетчика 8, который непрерывно отслеживает значение частоты по второму входу, Преобразование суммы частот в код осуществляется при подаче преобразуемых частот одновременно на обе входные шины 13 и 16. При этом подается сигнал, соответствующий логической "1" на шину 26 и на шины 23 и 25. Так как в этом случае открыты оба элемента И 14 и 17, то импульсы входной частоты от шины 13 проходят через элемент И 14, синхронизатор 3 и элемент ИЛИ 7 на суммирующий вход реверсивного счетчика 8 и через элемент 15 задержки, синхронизатор 5 и элемент ИЛИ 9 — на вычитающий вход реверсивного счетчика 8, импульсы входной частоты от шины 16 проходят через элементы И 17 и 18, элементы ИЛИ 29 и 7 и синхронизатор 4 на суммирующий вход реверсивного счетчика 8 и через элемент 20 задержки, элемент И 22, элементы ИЛИ

30 и 9 и синхронизатор 6 — на вычитающий вход реверсивного счетчика-8. Таким образом, на суммирующий вход реверсивного счетчика 8 поступают импульсы двух Ьходных частот и через элементы 15 и 20 задержки эти частоты поступают на вычитающий вход реверсивиого счетчика 8, причем с помощью синхронизаторов 3-6 и распределителя 2 осуществляется разнесение во времени всех входных импульсов реверсивного счетчика 8. Следовательно на реверсивном счетчике 8 осуществляется сложение двух частот, т.е. осуществляется непрерывное слежение эа суммой двух частот, причем знак суммы всегда положительный.

1179545

B режиме преобразования разности частот в код логическая 1 одновременно подается на управляющие шины 23 и 25 и 28 ° Входные частоты подаются на шины 13 и 16. В этом случае открыты элементы И 14 17

19 и 21. В отличие от преобразования суммы частот в код первая входная частота от шины 13 поступает на суммирующий вход реверсивного счетчика 8 и через элемент 15 задержки — на вычитающий вход реверсивного счетчика 8, а вторая входная частота от шины 16 поступает на вычитающий вход реверсивного счетчика 8 и через элемент

;20 задержки — на суммирующий вход реверсивного счетчика 8. Таким образом, осуществляется непрерывное слежение за разностью частот, причем знак разности положительный, если первая частота больше второй, и отрицательный, если первая частота меньше второй.

20

Сигнал с пятого выхода распределителя 2 поступает на управляющий вход коммутатора 10 и осуществляет считывание кода с реверсивного счетчика 8 на выходную шину 11 в моменты времени, когда на вхо" де счетчика 8 нет входных импульсов.

Для того, чтобы синхронизаторы

3-6 не вносили существенных временных сдвигов и не влияли на точность преобразования, частота генератора 1 должна выбираться не; менее чем в 5 раз большей (по числу выходов распределителя 2) максимального значения преобРазуе мых частот.

Выходной код реверсивного счетчика 8 — модифицированный дополнительный, поэтому, кроме знака кода, возможно по состоянию знако30 вых разрядов обнаружить переполне" ния счетчика 8.

1179545

Режим работы

23 28

»1»

«0»

«Х"

11К«

1fp»

»1« ffp«

»1«

«1«

»1«

«p 1 1

То же, разности частот

»1»

111 «

«0»

«1»

П р и м е ч а н и е, Х вЂ” произвольное состояние.

Составитель Г. Козуля

Редактор И. Ковальчук Техред C.éoâæèé Корректор С. Черни

Заказ 5696/61 Тираж 8?2 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035) Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Преобразование частоты по первому входу

То же, частоты по второму входу

Преобразование суммы частот

Состояние шин

25 26