Устройство для умножения

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее регистры множимого, множителя и произведения, матрицу блоков умножения, двоичные сумматоры, Преобразователи двоичного кода в десятичный и десятичный сумматор, причем первые входы блоков умножения казвдой строки матрицы соединены с выходами тетрад регистра множимого, вторые входы блоков умножения каждого столбца матрицы соединены с выходами соотвегствующих тетрад регистра множителя, причем входы k -го двоичного сумматора (k 1,...,N+M-3; N - число десятичных разрядов множимого; М - число десятичных разрядов множителя) соединены с выходами младших тетрад i -х блоков умножения ;j-x строк матрицы ( 1,...,N; j 1,.... ,М; i «- j 1 «- 2) , выходы двоичных сумматоров с первого по (К--М-2)-й соединены с входами соответствующих npeoCip,T.ionaTo.iieit дпоич110ГО кода в дecяти тf ыll, Р -и ныход -го преобразователя длоичиого кода л десятичный соединен с пходом (p+g-2)-ro разряда л,е1 ятич|1ого сумматора (р 1,...,Р; Р - число выХОД013 данного преобразовлтеля двоичного кода п десятичн1)1Й; 6 1,..., М+М-2), отличающееся тем, что, с целью сокращения количества оборудования, блоки умножения выполнены десятичными, выходы младшей и старшей тетрад первого блока умножения первой строки матрицы соединены соответственно с входом о первой тетрады регистра произведения (Л и входом первого двоичного сумматора, первьм выход первого преобразователя с двоичного кода в десятичный соединен с входом второй тетрады регистра произведения , выходы младшей и старшей тетрад N-го блока умножения М-и строки матрицы соединены соответственно с входом (+М-2)-го двоичного 00 О сумматора и входом (Н+М-2)-й тетрады десятичного сумматора, выходы старс ших тетрад i -х блоков ум1южения 00 j-X строк матрицы соединены с входами (/C4l)-ro двоичного сумматора,вы1ХОДЫ разрядов с первого по )-й десятичного сумматора соединены с входами тетрад соответственно с третьей по (()-m регистра произведения .

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3586484/24-24 (22) 29.04.83 (46) 23.09.85. Бюл. № 35 (72) Л.Г. Лопато и А.А. 1 1остак (71) Иинский радиотехнический институт (53) 681.325.5(088,8) (56) Авторское свидетельство СССР

¹ 729587, кл. С 06 F 7/52, 1977.

Авторское свидетельство СССР

¹ 1035600, кл. С 06 F 7/52, 1981. (54) (57) YCTP0ACTBO gJM YMHOEF HHH, содержащее регистры множимого, множителя и произведения, матрицу блоков умножения, двоичные сумматоры, преобразователи двоичного кода в десятичный и десятичный сумматор, причем первые входы блоков умножения каждой строки матрицы соединены с выходами тетрад регистра множимого, вторые входы блоков умножения каждого столбца матрицы соединены с выходами соотвеx ñòBóþùèõ тетрад ре- гистра множителя, причем входы k -ro двоичного сумматора (= 1,...,И+М-3; и — число десятичных разрядов множимого; М вЂ” число десятичных разрядов множителя) соединены с выходами младших тетрад =х блоков умножения

1 -х строк матрицы (с = 1,...,М;

1,...,Щ; l. + = k+ 2), выходы двоичных сумматоров с первого по (N+M-2)-й соединены с входами соотн< тствующих преобр,ззонатс лей двоичного кода в десятичный, о — и выход

Д-го лреобра.зователя дноичного кода я десятичный соединен с входом (+ — 2) — го разряда десятичного сумматора (P = 1,...,(; <, — число выходов данного преобразователя двоичног<> кода п десятичный; = 1,..., N+ht-2), о т л и ч а к щ с е с я тем, что, с целью сокращения количества оборудования, блоки умножения выполнены десятичными, выходы младшей и старшей тетрад первого блока умножечия первой строки матрицы соединены соответственно с входом первой тетрады регистра произведения и входом первого двоичного сумматора, первый выход первого преобразователя двоичного кода в десятичный соединен с входом второй тетрады регистра произведения, выходы младшей и старшей тетрад И -го блока умножения М-й строки матрицы соединены соответственно с входом (К+М-2)-го двоичного су -.матора и входом (М+М-2)-й тетрады десятичного сумматора, выходы стар. ших тетрад 1 -х блоков умножения

1-х строк матрицы соединены с входами (1+1)-го двоичного сумматора,вы<ходы разрядов с первого по 94.И -2)-й десятичного сумматора соединены с входами тетрад соответственно с третьей по (ф+ф)-ю регистра произведения.

1180881

Изобретение относится к выч:;:слительной технике и может быть использовано для быстрого умножения десятичных чисеп, а также применено в качестве основы при разработке универсальных быстродействующих устройств умножения двоичных и десятичных чисел.

Цель изобретения — сокращение количества оборудования устройства за счет упрощения используемых в нем преобразователей двоичного кода в десятичный из-,за обеспечения меньшего диапазона преобразуемых в них чисел.

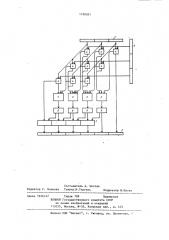

На чертеже приведена структурная схема предлагаемого устройства (для 15 случая, когда число десятичных разрядов у множимого и у множителя равно трем).

Устройство содержит регистры 1 — 3 множимого, множителя и произведения соответственно, матрицу блоков 4 умножения, двоичные сумматоры 5, преобразователи 6 двоичного кода в десятичный и десятичный сумматор 7, Первые входы блоков 4 умножения каждой стро- ки матрицы соединены с выходами соответствующих тетрад регистра 1 множимого, вторые входы блоков 4 умножения каждого столбца матрицы соединены с выходами соответствующих тетрад З0 регистра 2 множителя, входы k -ro двоичного сумматора 5 (k = 1,2,3,4) соединены с выходами младших тетрад -х блоков 4 умножения j --x строк матрицы (j = 1,2,3; = 1,2,3;

3S + j = (+2) выходы старших тетрад которых соединены с входами (1+1)-го двоичного сумматора 5, выходы двоичных сумматоров 5 с первого по четвертый соединены с входами соответст- 40 ,вующих преобразователей 6 двоичного кода в десятичный, -й выход g --ro преобразователя 6 двоичного кода в десятичный соединен с входом (+ -2)ro разряда десятичного сумматора 7 45 .(= 1,2; g = 1,2,3,4), выходы младшей и старшей тетрад первого блока

4 умножения первой строки матрицы соединены соответственно с входом первой тетрады регистра 3 произведе- 50 ния и входом первого двоичного сумматора 5, первый выход первого преобразователя 6 двоичного кода в десятичный соединен с входом второй тетрады регистра 3 произведения, выходы младшей и старшей тетрад третьего блока 4 умножения третьей строки матрицы соединены соответстванно с входом четвертого двоичного сумматора 5 и входом четвертой тетрады десятичного сумматора 7, выходы разрядов с первого по четвертый де>сятичного сумматора 7 соединены с входами тетрад соответственно с третьей по шестую регистра 3 произведения.

В устройстве блоки 4 умножения матрицы, двоичные сумматоры 5, преобразователи 6 двоичного кода в десятичный и десятичный сумматор 7 являются комбинационными схемами.

Блок 4 умножения матрицы предназначен для перемножения двух десятичных цифр (цифры множимого и цифры множителя). На его выходах формируется двухразрядное произведение в десятичном коде. Пусть, например, цифра множимого равна 9, цифра множителя равна 7, и для представления десятичных цифр используется код прямого замещения 8 — 4 — 2 — 1. Тогда на выходах старшей тетрады блока 4 умножения сформируется код 0110, а на выходах его младшей тетрады— код 0011, Блок 4 умножения может быть реализован по соответствующей таблице истинности на ПЗУ или в виде совокупности двоичного умножителя и преобразователя двоичного кода в десятичный, причем выходы умножителя подключены соответствующим образом к входам преобразователя двоичного кода в десятичный или же другими известными методами и средствами.

В каждом сумматоре 5 осуществляется двоичное суммирование младших цифр произведений, сформированных на выходах всех тех блоков

4 умножения, которые расположены в той же весовой десятичной позиции, что и данный сумматор 5, и старших цифр произведений, сформированных на выходах всех тех блоков 4 умножения, которые расположены в соседней младшей весовой позиции по отношению к весовой десятичной позиции данного сумматора 5.

С помощью преобразователей 6 осуществляется преобразование двоичных сумм, сформированных на выходах сумматоров 5, в десятичные суммы.

Десятичный сумматор 7 выполняет суммирование с распространением переноса результатов, образованных на выходах преобразователей 6 двоичного кода в десятичный.

i 180881 4 блока 4 умножения первой строки матрицы, а во второй разряд регистра 3 произведения подается результат, обра. зованный на первом выходе первого преобразователя 6 двоичного хода в десятичный, Устройство работает следующим образом.

Одновременно или последовательно во времени в регистры 1 и 2 соответственно множимого и множителя загружаются десятичные сомножители.

После загрузки операндов во входные регистры I и 2 устройства начинают работать блохи 4 умножения матрицы, с помощью которых формируются в де- 10 сятичном коде двухразрядные произведения десятичных цифр множимого и множителя. Сформированные на выходах

1блоков 4 умножения матрицы значения младших и старших тетрад двухразряд- 15 ных произведений поступают далее на .равновесовые входы сумматоров 5, где осуществляется их двоичное суммирование. Образованные на выходах сумматоров 5 двоичные суммы посред- gp ством преобразователей 6 преобразуются в десятичные суммы, которые поступают на равновесовые входы десятичного сумматора 7. Сформированная на выходах десятичного сумматор 7 сумма записывается в соответствующие разряды регистра 3 произведения, в первый разряд которого поступает значение младшей тетрады r выхода первого

Таким образом, предложенное устройство для умножения может быть принято за основу при разработке универсального быстродействующего устройства умножения двоичных и десятичных чисел. Для этого необходимо в его блоках 4 умножения матрицы предусмотреть формирование значений тетрадных произведений как в десятичном коде, так и в двоичном, а вместо десятичного сумматора 7 использовать универсальный сумматор для сложения двоичных и десятичных чисел. Это устройство при умножении десятичных чисел рабо1ает также, как и рассмотренное выше. Основное отличие при умножении на нем двоичных чисел состоит в том, что на входы сумматора 7 информация поступает не с выходов преобразователей 6 двоичного кода в десятичный, а непосредственно с выходов двоичных сумматоров 5.

1180881

Составитель А. Uîñòàê

Редактор Г. Волкова . Техред И.Гергель

Заказ 5926/47 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, л