Устройство для коррекции ошибок в непозиционном аддитивном коде

Иллюстрации

Показать всеРеферат

УСТРОЛСТВО ДЛЯ КОРРЕК1ЩИ ОШБОК В НЕПОЗИЦИОННОМ АЦДИТИВНОМ КОДЕ, содержащее группу вычитателей по модулю, группу блоков умножения на константу по модулю, три сумматора по модулю, первую схему сравнения с нулем, первый блок элементов запрета, причем информационный вход устройства соединен с входами уменьшаемого вычитателей по модулю группы и первыми входами первого и второго сумматоров по модулю,выходы вычитателей по модулю группы соединены с входами соответствующих блоков умножения на константу по модулю группы, выходы которых соединены с Соответствующими входами третьего сумматора по модулю, выход которого соединен с входом первой схемы сравнения с нулем, выход которой соединен с управляющим входом первого блока элементов запрета, первый информационный вход которого соединен с выходом третьего сумматора , отличающееся тем, что, с целью повышения быстродействия , оно содержит четвертьй сумматор по модулю, два преобразователя в дополнительный код, группу блоков деления на константу по модулю, группу схем сравнения, вторую схему сравнения с нулем, второй блок элементов запрета и элемент И, причем выходы первого и второго сумматоров по модулю соединены с входами соответствую1 (их преобразователей в дополнительный код, выходы вычитателей по модулю группы соединены с соответствующими входами четвертого сумматора по модулю, выходы первого и второго преобразователей в дополнительный код соединены соответственно 9 с (п+1)-и входами четвертого и (Л третьего сумматоров по модулю (где п - количество информационных оснований ) , выход четвертого сумматора по модулю соединен с первыми входами схем сравнения группы и входом второй схемы сравнения с нулем, выход которой соединен с управля00 ющим входом второго блока элементов о запрета, вторым информационным 00 QD входом первого блока элементов запрета и с первым входом элемента И, выход первой схемы сравнения с нулем соединен с первым информационным входом второго блока элементов запрета и с вторым входом элемента И, выход которого является выходом отсутствия ошибки устройства, второй информационный вход второго блока элементов запрета соединен с выходом четвертого сумматора по модулю, выходы первого и второго блоков элементов запрета соединены соответственно с вторыми входами второго и первого сумматоров по модулю, вы

СОК)З СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (SI)4 С 06 Г 11/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

QO

Ю

00 с© 3

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3692424/24-24 (?2) 13.01.84 (46) 23.09.85. Бюл. Р 35 (72) И.Я,Акушский, И.Т.Нак,С.А.Инютин и В.И.Максимов (71) Институт математики и механики АН КазССР (53) 68 1. 3(088 .8) (56) Авторское свидетельство СССР и 960823, кл. G 06 F 11/08, 1980.

Авторское свидетельство СССР

У 932499, кл . С 06 F 11/08, 1980. (54)(57) УСТРОЙСТВО ДЛЛ КОРРЕКИИИ

ОШИБОК В НЕЛОЗИЦИОННОМ /ДДИТИВНОМ

КОДЕ, содержащее группу вычитателей по модулю, группу блоков умножения на конеTRHTV IIO MOII III0, ТрН «óììàтора по модулю, первую схему ñðàâнения с нулем, первый блок элементов запрета, причем информационный вход устройства соединен с входами уменьшаемого вычитателей по модулю группы и первыми входами первого и второго сумматоров по модулю,вы— ходы вычитателей по модулю группы соединены с входами сooTBpT(твующих блоков умножения на константу по модулю группы, выходы которых соединены с соответствующими входами третьего сумматора по модулю, выход которого соединен с входом первой схемы сравнения « нулем, выход которо i соединен с управляющим входом перво o блока элементов запрета, первый HHAopMBIIHoHHbIH вход которого соединен с выходом третьего сумматора, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит четвертый сумма„„SU„„1180897 А тор по модулю, два преобразователя в дополнительный код, группу блоков деления на кон танту по модулю, группу схем сравнения, вторую схему сравнения с нулем, второй блок элементов запрета и элемент И, причем выходы первого и второго сумматоров по модулю соединены с входами соответствующих преобразователей в допол— нительный код, выходы вычитателей по модулю группы соединены «. соответствующими входами четвертого сумматора по модулю, выходы первого и второго преобразователей в дополнительный код соединены соответственно с (n+1)-и входами четвертого и третьего сумматоров по модулю (где п — количество информационных оснований), выход четвертого сумматора по модулю соединен « первыми входами схем сравнения группы и входом второй схемы сравнения с. нулем, выход которой соединен с управляющим входом второго блока элементов запрета, вторым информационным входом первого блока элементов запрета и « первым входом элемента И, выход первой схемы сравнения с нулем соединен с первым информационным входом второго блока элементов запрета и « И, вьгхоц которого является выходом отсутствия ошибки устройства, второй информационный вход второго блока элементов запрета соединен с выходом четвертого сумматора по модулю, выходы первого и второго блоков элементов запрета соединены соот ветственно с вторыми входами второго и первого сумматоров по модулю, вы1180897 группы.

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для автоматического обнаружения и коррекции ошибок в группах двоичных разрядов.

Целью изобретения является повышение быстродействия.

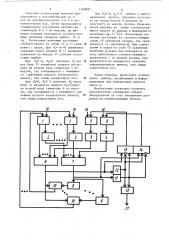

На чертеже представлена схема устройства для коррекции ошибок в непозиционном аддитивном коде.

Устройство для коррекции ошибок в непозиционном аддитивном коде «одержит группу 1 вычитателей по модулю, группу 2 блоков умножения на константу по модулю, преобразователи 3 и 4 в дополнительный код, «умматоры 5 — 8 по модулю, группу 9 блоков деления на константу по модулю, группу сравнения 10 схем, схемы 11 и 12 сравненпя с нулем, "элемент И 13, блоки 14 и 15 элементов запрета, информационный вход

16, выход 17 отсутствия ошибки.

Устройство для коррекции ошибок в непозиционном аддитивном коде работает следующим образом.

Число О а А 9 в аддитивном непозиционном коде (слабоарифметическом коде системы остаточных клас сов) с двумя J

A = Ыт, ° ° °, Kn Mn+g Mn+8 где М; = 1 п с ; — A(mod Р;);

Появление одного из d, d равных нулю, свидетельствует об одномодульной ошибке в контрольном вычете, соответствующем ненулевому элементу синдрома. Синдром, равный нулю, свидетельствует об отсутствии ошибок в числе.

Информационные и контрольные выче35 ты числа А поступают по входам 16 устройства на входы уменьшаемых группы 1 вычитателей по модулю и первые входы сумматоров 5 и 6 по модулю соответственно.

40 Значения информационных вычетов умножаются на номер соответствующегЪ вычета на соответствующих блоках

2 умножения по модулю группы, на выходах которых получаются значения

4> у = ig„.(mod q) . ход третьего сумматора по модулю соединен с входами блоков деления на константу по модулю группы, вы— ходы которых соединены с вторыми

j=1,2 0С п 1= р- g. д(„(mod Q);

i=1

° ° °

P ... Р > — взаимно простые о«) 9 % нования, причем справедливо г„ (,...,(г„

0 — контрольный модуль.

Для экономии разрядности оборудования можно положить О =Р„ )и простое число, тогда 1; =1 и

1 = входами соответствующих схем сравнения группы, выходы которых «ое— динены с входами вычитаемого соответствующих вычитателей по модулю

Такой избыточный код корректирует одномодульные ошибки (т.е. произвольные двоичные ошибки в одной группе бит, соответствующей вычету по одному ин5 формационному или контрольному модулю кода), если для матрицы коэффициентов кода справедливо,(4::::;, !)

H0D () ; Q)=1.

Все миноры матрицы взаимно просты

c Q. Синдром ошибок равен . n

g, (mod Q) — о n+q(mod Q)

i--1 и у,0; (; (mod О) с и+ г (шо 1 Q)

=1

20 Очевидно, что величина ошибок д ; и номер ошибочного основания обнаружены, если выполняется равенство

,= =(,(ЪЬ =(;(я й

1180897 4

При d g О, d P О ошибка в инфсрмационном вычете. Значение поступает на входы блоков 9 деления на я . константу по модулю группы. Произво5 дится деление на номер соответствующего вычета по модулю и формируются у- величины (d (i/ О/Я. Полученные величины поступают на соответствующие схемы 10 сравнения группы, где сравв- 10 ниваются со значением I>. При совпаые денни в одной из схем 10 сравнения т величина d"÷åðåç нее передается на

1 т- вход вычитаемого соответствующего вычитателя 1 по модулю группы, где

15 вычитается из имеющегося значения информационного вычета, тем самым корректируя его.

Значения контрольных вычетов пре образуются в дополнительный до код на преобразователях 3 и 4 в дополнительный код. Затем производите суммирование полученных величин на сумматорах 8 и 7 по модулю, на выходах которых получаются соответств ющие значения синдрома ошибок о „ и

d"2 . Полученные величины поступают соответственно на схемы 12 и 1 I сра нения с нулем. При d"= d - =О единичн значения через элемент И 13 вызываю появление на выходе 17 сигнала отсу ствия ошибки.

При д"„Ф О, сГ2=0 значение сГ„ че рез блок 15 элементов запрета посту пает на второй вход сумматора 5 по модулю, где складывается с имеющимся значением первого контрольного вычета, тем самым корректируя его.

При d =О, d2/ О значение с 2 через блок 14 элементов запрета поступает на второй вход сумматора 6 по моду— лю, где складывается с имеющимся значением второго контрольного вычета, тем самым корректируя его.

Таким образом, происходит исправ20 ление ошибок, возникающих в информационных или контрольных вычетах числа А.

Изобретение позволяет получить дополнительно сокращение объема

25 оборудования за счет уменьшения разрядности обрабатывающих блоков.