Многоканальное устройство для сопряжения вычислительных машин

Иллюстрации

Показать всеРеферат

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ МАШИН, содержащее первую и вторую группы каналов, каждьш из которых содержит выходной триггер и триггер заявок, два элемента ИЛИ, элемент И, первый элемент НЕ, коммутатор и дешифратор адреса, причем в каждом канале входы D- и С-триггера заявок соединены с входами заявок соответствующей группы входов - выходов устройства, прямой выход триггера заявок соединен с первым входом первого элемента ИШ, S-вход выходного триггера подключен к выходу элемента И, первый вход которого соединен с выходом второго элемента ИЛИ, второй вход с выходом дешифратора адреса, а выход - через первый элемент HIс R-входом выходного триггера, информационньй вход коммутатора и выход выходного триггера являются соответственно адресным входом и выходом разрешения канала устройства , вторые входы первых элементов ИЛИ кана.тов первой и второй групп соединены соответственно с первым и вторым входами блокировки устройства, в каждой группе каналов выход первого элемента ИЛИ каждого канала, кроме последнего, соединен с вторым входом первого элемента ИЛИ пocлeдyюIr eгo канала, входы дешифраторов адреса каналов первой группы соединены через первую адресную 111ИНУ с выходами коммутаторов канапов второй группы, а входы дешифраторов адреса каналов второй группы подключены через вторую адресную 1лину к выходам коммутаторов каналов первой группы, отличающеес S с я тем, что, с целью расширения области применения, в кажд1.1Й канал (Л введены элементы ИЛИ, И-НЕ, НЕ, причем в каждом канале первьп вход третьего элемента ИЛИ соединен с входом блокировки канала, второй вход третьего элемента ИЛИ соединен с выходом элемента И-НЕ, а выход с S-входом триггера заявок, инверс00 ный выход которого соединен с первым входом элемента И-НЕ и с входом о со второго элемента НЕ, прямой выход триггера заявок соединен с управляющим входом кoм yтaтopa и выходом запроса канала, второй вход элемента И-НЕ соединен с выходом второго элемента НЕ и с входом и выходом Запрет обмена канала, группа входов второго элемента ИЛИ каждого канала первой группы соединена с прямыми выходами триггеров заявок каналов второй группы, а группа входов второго элемента ИЛИ каждого канала второй группы соединена с прямыми выходами триггеров заявок каналов первой группы.

СОЮЗ СОВЕТСНИХ

СООИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (5П4 С 06 Р 1 3/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3732035/24-24 (22) 21.04.84 (46) 23.09.85. Бюп. !! - 35 (72) F. A.Êèì (71) Проектное конструкторско-технологическое бюро "Узводприборавтоматика" (53) 68 1.3(088.8) (56) Авторское свидетельство СССР

1! 842812, кл. С 06 F 9/46, 1978, Авторское свидетельство СССР

Ф 1043622, кл. 0 06 F 3/04, G 06 F 9/46, 1982. (54) (57) МНОГОКАНАЛЬНОЕ УСТРО!!СТВО

ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ МА!!!ИН, содержащее первую и вторую группы каналов, каждый из которых содержит выходной триггер и три гер заявок, два элемента ИЛИ, элемент И, первый элемент HF, коммутатор и дешифратор адреса, причем в каждом канале входы D- и С-триггера заявок соединены с входами заявок соответствующей группы входов — выходов устройства, прямой выход триггера заявок соединен с первым входом первого элемента ИЛИ, S-вход выходного триггера подключен к выходу элемента И, первый вход которого соединен с выходом второго элемента ИЛИ, второй вход— с выходом денифратора адреса, а выход — через первый элемент Н! с R-входом выходного триггера, информационный вход коммутатора и выход выходного триггера являются соответственно адресным входом и выходом разренения канала устройства, вторые входы первых элементов ИЛИ канадцев первой и второй групп г 1едпнены соответственно

„„SU„„1180910 A с первым и вторым входами блокировки устройства, в каждой группе каналов выход первого элемента ИЛИ каждого канала, кроме последнего, соединен с вторым входом первого элемента ИЛИ последующего канала, входы дешифраторов адреса каналов первой группы соединены через первую адресную нину с вьгходами коммутаторов каналов второй группы, а входы дешифраторов адреса каналов второй группы подкпючены через вторую адресную шину к выходам коммутаторов каналов первой группы, о т л и ч а ю щ е ес я тем, что, с целью расширения области применения, в каждый канал введены элементы ИЛИ, И-НГ, НГ, причем в каждом канале первьпi вход третьего элемента ИЛИ соединен с вхо— дом блокировки канала, второй вход третьего элемента ИЛИ соединен с выходом элемента И-HF., а выход с S-входом триггера заявок, инверс— ный выход которого соединен с первым входом элемента И-НЕ и с входом второго элемента HF. прямой выход триггера заявок соединен с управляющим входом коммутатора и выходом запроса канала, второй вход элемента И-HF. соединен с выходом второго элемента НГ и с входом и выходом

"Запрет обмена" канала, группа входов второго элемента ИЛИ каждого канала первой группы соединена с прямыми выходами триггеров заявок каналов второй группы, а группа входов второго элемента ИЛИ каждого канала второй группы соединена с прямыми выходами триггеров заявок каналов первой группы.

1180910

Изобретение относится к вычислй тельной технике и может найти приме. нение в многомашинных вычислительных комплексах, работающих в составе систем автоматизации технологически- 5 ми процессами.

Цель изобретения — расширение области применения устройства за счет обеспечения корректного двухстороннего выбора и обмена между двумя группами ЭВМ в реальном масштабе времени,.

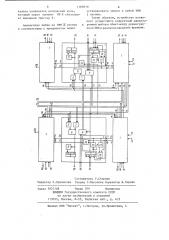

На чертеже представлена блок-схема устройства.

Устройство содержит каналы 1, 15 каждый из которых включает триггер 2 аявок, узел 3 приоритета, коммутатор 4, второй элемент ИЛИ 5, элемент И 6, дешифратор 7 адреса, элемент kIL" 8, выходной триггер 9, 20 вход 10 блокировки, выход 11 блокировки канала, управляющие входы 12 и 13 разрешения работы устройства, входы 14 заявок, выход 15 запроса, информационный вход 16 адреса, вы- 25 ход 17 коммутатора и вход 18 дешиАратора адреса, входы 19 запроса и выход 20 разрешения канала, вход 21 и выход 22 запрета обмена.

Узел 3 приоритета канала состоит З0 пз элемента И-НЕ ?3, первого элемента KIH 24, элемента НЕ 25, третьего элемента ИЛИ 26.

Показаны также первая и вторая адресные шины 27 и 28.

Каналы 1 в верхней части схемы составляют первую группу, остальные каналы принадлежат к второй группе.

Входы 14 и 16 и выход 20 обраayioT группу axopoa t abmopoa ° c no- 40 мощью которых абоненты, например подключаются к устройству.

Устройство работает следующим

I образом, В исходном состоянии (нет заявок 45 на входах 14) триггеры 2 находятся в состоянии нуля.

Пусть приходит заявка на канал М

3 группы 1. Если при этом идет текущий обмен, то на входе — выходе 21 — 22 50 присутствует потенциал блокировки, который через вход элемента И-НЕ 23, элемент ИЛИ 26 блокирует триггер 2, т.е. последний остается в исходном состоянии. В случае, если при поступ-55 ленни заявки на входах М не производится ни один обмен ЭВМ группы с ЗВМ группы П, то на входе — выходе 21 — 22 канала 38M M присутству1 ет потенциал разрешения, который через элементы И-НЕ 23, ИЛИ 26 разрешает работу триггера 2 и последний устанавливается в единичное состояние. При этом потенциалом нуля с инверсного выхода через элемент НЕ 25 устанавливается потенциал единицы на входах — выходах 21—

22 всех каналов группы 1, блокируя таким образом возможность срабатывания триггеров 2 и соответственно возможность их обмена других каналов.

Для устранения блокировки собствен— ного триггера 2 заявок потенциал с инверсного выхода триггера 2 за— явок поступает на вход элемента И-HF. 23. Одновременно с заявкой

ЭВМ через входы 16 выдает в канал. 1 адрес ЭВМ группы П, к которой эта заявка должна поступить. При одновременном поступлении заявок на два канала одной группы, единица с выхода триггера 2 канала более высокого приоритета через свой элемент ИЛИ 24 устанавливает триггер 2 канала бо— лее низкого приоритета в исходное состояние.

В канале 1 с наиболее высоким приоритетом заявка с выхода триггера 2 проходит на выход 15 и управляющий вход коммутаторов 4, выходы которых в исходном состоянии отключены от адресной шины 27. Активный сигнал на управляющем входе коммутаторов 4 переводит их в режим передачи, т.е. адрес, который поступает с входов 16 через коммутаторы 4, передается на выходы 17 канала. Этот адрес далее через адресные шины 27 поступает на входы 18 каналов II группы, а заявка с выхода 15 запрашивающего канала I группы поступает на соответствующие входы 19 запросов каналов

IT группы. Б соответствии с адресом на шинах 28 в одном из каналов М„. второй группы срабатывает дешифратор 7 адреса и заявка с входа 19 поступает на выход элемента ИЛИ 5.

При наличии двух единиц на входах элемента И 6 устанавливается в еди— ницу выходной триггер 9 выбранного канала М . Активный сигнал с выхо1 да 20 канала поступает в соответствующую ЭВМ. После окончания сеанса связи ЭВМ источник сбрасывает триггер 2, а коммутаторы 4 отключаются от шин 28, на выходе элемента И б

1180910

ЯЖ 1Ч

16 1Ч

20 /6 1Ч

21 а 16 1Ч

О16 W

Составитель Г. Стернин

Редактор Е.Лушникова Техред С.Мигунова Корректор В.Гирняк

Заказ 5927/48 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по дегам изобретений и открьггий

113035, Москва, )К-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r.Ужгород, ул.Проектная, 4 канала появляется логический нуль, который через элемент НЕ 8 сбрасывает выходной триггер 9.

Аналогично любая из ЭВМ 3I группы в соответствии с приоритетом может устанавливать запрос к любой ЭВМ группы.

Таким образом, устройство позволяет осуществить корректный двухсторонний выбори обмечмежду двумягруп. пами ЭВМ в реальном масштабе времени.