Элемент памяти

Иллюстрации

Показать всеРеферат

ЭЛЕМЕНТ ПАМЯТИ, содержащий . тиристор, катод которого соединен с шиной ., выборки, транзистор записи, эмиттер которого соединен с шиной запяся, а коллектор - с п-базой тиристора, отличающийс я тем, что, с целью повышения надежности элемента памяти, в него введен второй ключевой транзистор, эмягкр которого подключен к адрешой шине, база соединена с П-базой, а коллектор - с анодом тиристора, база транзистора записи ооеданена с дополнительной шиной записи-считывания. 00 QD 00 О

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (l 9) (11) (51)4 6 11 С 11 40

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЭОБРЕТЕНИ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (л(1 +gal (21) 3492778/24 — 24 (22) 17.09.82 (46) 23.09.85. Бюл. Р 35 (72) М. О. Ботвиник, Ю. Н. Еремин и Ю. И. Кузовлев (53) 68).327.66(088.8) (56) . Авторское свидетельство СССР

Р 3778ol кл. G 11 С 11/34, 1973

Авторское свидетельство СССР пе 888207, кл. G 11 С ll/40, 1981. (54) (57) ЭЛЕМЕНТ ПАМЯТИ, содержащий тиристор, катод которого соединен с шиной ., выборки, транзистор записи, эмиттер которого соединен с шиной завися, а коллектор — с и-базой тирнстора, о т л и ч а ю щ и йс я тем, что, с целью повышения надеж- ности элемента памяти, в него введен второй ключевой транзистор, эмиттер которого подключен к адресной шине, база соединена с п-базой, а коллектор — с анодом тиристора, база транзистора записи соединена с дополнительной шиной записи-считывания.

1180980

Составитель А. Дерюгин

Техред Л.Микеш

Редактор Л. Коссей

Корректор Л.Бескид

Тираж 583

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж.35, Раушская наб., д. 4/5

Заказ 5934/52

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Изобретение относится к вычислительной технике и может быть использовано для построения эапоминавнцих устройств (ЗУ).

Целью изобретения является повышение надежности элемента памяти. S

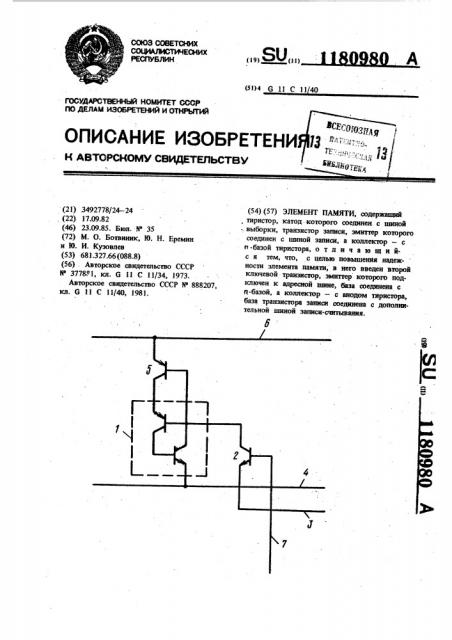

На чертеже представлена электрическая схема элемента памяти.

Элемент памяти содержит тиристор 1, . транзистор 2 записи, шину 3 записи, шину

4 выборки, второй ключевой транзистор 5, адресную шину 6, шину 7 записи-считывания.

Элемент памяти работает следующим образом.

В режиме хранения информации устойчи- 1S вость выключенного состояния обеспечивается вторым ключевым транзистором 5, который в этом случае выключен, и поэтому анод тиристора 1 не подключен к адресной шине 6.

В этих условиях включение тиристора 1 20 невозможно. Устойчивость включенного состояния обеспечивается протеканием через тиристор 1 тока, большего или равного току удержания. Ток включенного состояния протекает по цепи: адресная шина 6, эмиттер- 25 коллектор второго ключевого транзистора 5, анод-катод тиристора 1, шина 4 выборки.

В режиме считывания по шине записисчитывания 7 подается ток, который протекает по цепи: шина записи-считывания 7, базаколлектор транзистора записи 2, и-база-катод тиристора 1. Шина 3 записи в режиме считывания имеет потенциал, исключающий протекание тока по цепи база-эмнттер транзистора записи 2.

Состояние элемента памяти определяется так: наличие тока в шине записи-считывания

7 означает, что тиристор 1 открыт, а его отсутствие что он закрыт.

В режиме записи включение тиристора 1 осуществляется включением транзистора 2 при равных потенциалах на шине 4 выборки и на шине 3 записи. В базу транзистора

2 записи подается ток, необходимый для его включения. При этом появляется ток базы второго ключевого транзистора 5, а затем после егр. включения включается транзистор

1, так как на его и -базы вытекает ток.

Выключение тиристора 1 происходит по тому же электрическому контуру, что и в режиме считывания, с той лишь разницей, что потенциал, формируемый на и-базе тиристора 1 такой, при котором невозможно протекание тока в базовой цепи второго ключевого транзистора 5. Ток, втекающий в fl -базу тиристора 1, выключает его, рассасывая избыточный заряд в базовых областях.