Устройство для контроля микросхем памяти

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МИКРОСХЕМ ПАМЯТИ, содержащее блок дискриминаторов, выход которого является управлякицим выходом устройства , блок индикации, входы первой группы которого являются адресными входами устройства, блок формирователей кода числа, управляющий вход которого является первым управлякяцим входом устройства, выходы являются информационными выходами устройства, а информационные входы соединены с входами первой группы блока дискриминаторов , входами второй группы блока индикации и являются информационными входами устройства, отличающееся тем, что, с целью повышения точности контроля, устройство содержит преобразователь механических колебаний, усилитель, блок сравнения, триггер и блок коммутаторов , один вход которого соединен с первым входом блока сравнения и одним входом блока формирователей кода числа, другие входы блока коммутаторов соединены с выходами блока формирователей кода числа, а выходы соединены с входами второй группы I (Л блока дискриминаторов, один вход которого соединен с выходом триггера , один установочный вход которого является вторым управляющим входом устройства, а другой установочный вход соединен с первым выходом блока сравнения, второй выход которого со-, единен с управляющим входом блока индикации, второй вход соединен с выходом усилителя, вход которого соединен с выходом преобразователя механических колебаний.

СОЮЗ СОВЕТСКИХ

ОЗФЮЛ СП

РЕСПУБЛИН () 9) (И) (5))4 G 11 С 29/00, 7/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3729835/24-24 (22) 25.04.84 (46) 23.09.85. Бюл. Ф 35 (72) Я.М.Беккер, Н.А.Дюсенова, В.И.Ииронцев, Ю.П.Слудняков и Г.А.Пе. тухов (53) 681.327(088.8) (56) Авторское свидетельство СССР

Ф 754423, кл. G. 06 F 11/22, 1978.

Авторское свидетельство СССР

9 826416, кл. G 11 С 7/00, 1979. (54) (57) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

МИКРОСХЕМ ПАМЯТИ, содержащее блок дискриминаторов, выход которого является управляющим выходом устройства, блок индикации, входы первой группы которого являются адресными входами устройства, блок формирователей кода числа, управляющий вход которого является первым управляющим входом устройства, выходы являются информационными выходами устройства, а информационные входы соединены с входами первой группы блока дискриминаторов, входами второй группы блока индикации и являются информационными входами устройства, о т л ич а ю щ е е с я тем, что, с целью повышения точности контроля, устройство содержит преобразователь механических колебаний, усилитель, блок сравнения, триггер и блок коммутаторов, один вход которого соединен с первым входом блока сравнения и одним входом блока формирователей кода числа, другие входы блока коммутаторов соединены с выходами блока формирователей кода числа, а выходы соединены с входами второй группы блока дискриминаторов, один вход которого соединен с выходом триггера, один установочный вход которого является вторым управляющим входом устройства, а другой установочный вход соединен с первым выходом блока сравнения, второй выход которого со-. единен с управляющим входом блока индикации, второй вход соединен с выходом усилителя, вход которого соединен с выходом преобразователя механических колебаний.

Изобретение относится к вычислительной технике, а именно к устройствам для контроля памяти, и может быть ислользовано при контроле качества программирования микросхем 5 постоянной памяти.

Цель изобретения - повышение точности контроля программируемых микросхем за счет отбраковки микросхем с разрушенныки перемычкамй. 10

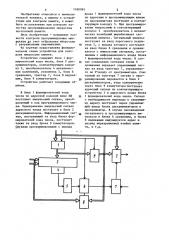

На чертеже представлена функциональная схема устройства для контроля микросхем памяти, Устройство содержит блок 1 формирователей кода числа, блок 2 дискриминаторов, контактирующую колодку 3, преобразователь 4 механических колебаний, усилитель 5, блок 6 сравнения, триггер 7, блок 8 индикации, блок 9 коммутаторов. 20

Устройство работает следующим обрвзом.

В блок 1 формирователей кода числа по адресной кодовой шине КШ поступает импульсный сигнал, преобразуемый в код программируемого числа.. Одновременно импульсный сигнал адресного входа поступает в блок 2 дискриминаторов. Информационный сигнал, поступающий на вход блока формирователей кода числа, поступает также на вход блока 9 коммутаторов.

Сигналы программирования с выхода

80985 г блока 1 формирователей кода числа по адресным и программирующим шинам из программатора поступают в контактирующую колодку 3. При программировании микросхемы в контактирующей колодке 3 преобразователь 4 механических колебаний вырабатывает сигнальный импульс. Сигнальный импульс поступает на вход порогового усилителя 5, с выхода которого поступает на вход блока 6 сравнения и сравнивается с импульсньи сигналом, поступившим с информационного входа блока

1 формирователей кода числа. В случае совпадения сигналов схема 6 сравнения передает управляющий сигнал на вход триггера 7, управляемого по P-входу от программатора. Считанный из триггера 7 сигнал о программировании передается в блок 2 дискриминаторов, куда одновременно через блок 9 коммутатора поступает адресный сигнал из контактирующего устройства 3 и адресного входа блока

25 1 формирователей кода числа. Сигнал о необходимости перехода к следующему адресу поступает через управляющий выход блока дискриминаторов в программатор. В случае несовпадения сигнального и программируницего импульсов в блоке.6 сравнения, в блоке

8 индикации индуцируется адрес и разряд неразрушенной ячейки, памяти, и т.д.