Аналого-цифровой преобразователь в код системы остаточных классов

Иллюстрации

Показать всеРеферат

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ Б КОД СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ, содержащий первый блок вычитания , первый вход которого объединен с первым входом первого компаратора и является входной шиной преобразователя , второй вход подключен к первому выходу первого цифроаналогового преобразователя, второй выход которого подключен к второму входу первого компаратора, а входы - к . соответствующим выходам первого счетчика импульсов, второй счетчик импульсов , выходы которого подключены к соответствующим входам второго ЦАП, выход которого подключен к первому входу второго компаратора, RS-триггер, 5 -вход которого является шиной Запуск, выход подключен к первому входу элемента И, второй .вход которого является шиной тактовых импульсов, первый шифратор, выходы которого подключены к соответствующим входам сумматора по мо дулю наибольшего основания, выходы которого являются выходными шинами преобразователя по наибольшему основанию , отличающийся тем, что, с целью повьш1ения быстродействия , в него введены по числу оснований системы остаточных классов И инверторов, ц-2 шифратора, 11-2 сумматора по модулям других оснований системы остаточньк классов , кроме наименьшего, И дополнительных элементов И, М-2 счетчика импульсов,

114 А

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (51)4 Н 03 M 1/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

1"10 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТР1Й--. (21) 3585890/24-24 (22) 29.04.83 (46) 23.09.85. Бюл. N9 35 (72) С.Н. Хлевной и Н.И. Швецов (53) 681.325 (088.8) (56) Гитис Э.И. Преобразователи информации для электронных цифровых вычислительных устройств. — M.

Энергия, 1970, с. 307.

Авторское свидетельство СССР, Ф 1034170, кл. Н 03 К 13/17, 1982.

\ (54)(57) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В КОД СИСТЕМЫ ОСТАТОЧНЫХ

КЛАССОВ, содержащий первый блок вычитания, первый вход которого объединен с первым входом первого компаратора и является входной шиной преобразователя, второй вход подключен к первому выходу первого цифроаналогового преобразователя, второй выход которого подключен к второму входу первого компаратора, а входы — к соответствующим выходам первого счетчика импульсов, второй счетчик импульсов, выходы которого подключены к соответствующим входам второго

ЦАП, выход которого подключен к первому входу второго компаратора, Ябтриггер, 5 -вход которого является шиной "Запуск", выход подключен к первому входу элемента И, второй .вход которого является шиной тактовых импульсов, первый шифратор, выходы которого подключены к соответствующим входам сумматора по модулю наибольшего основания, выходы которого являются выходными шинами преобразователя по наибольшему основанию, отличающийся тем, что, с целью повышения быстродействия, в него введены по числу оснований системь1 остаточных классов 11 инверторов, П -2 шифратора, П-2 сумматора по модулям других оснований системы остаточных классов, кроме наименьшего, П дополнительных элементов И, И -2 счетчика импульсов, 11 -2 цифроаналоговых преобразователя, П -2 компаратора, первые входы которых объединены с первыми входами П-2 блоков вычита.ния, соединенных последовательно между собой и включенных между выходом первого блока вычитания и вторым входом второго компаратора,вторые входы 11-2 блоков вычитания подключены к первым выходам соответствующих П -2 цифроаналоговых преобразователей, вторые выходы которых подключены к вторым входам соответствующих п -2 компараторов, входык соответствующим выходам соответствующих П -2 счетчиков импульсов, при этом выходы П компараторов подключены к входам соответствующих П инверторов и первым входам соответ- . ствующих П дополнительных элементов И, вторые входы которых объединены и подключены к выходу элемента И, третьи входы дополнительных элементов И, начиная с второго, подключены к выходам 11 -1 инверторов, начиная с первого, выход П -го инвертора подкгчочен к R -входу RG-триггера, при этом выход каждого из и-1 дополнительных элементов И подключен к входу соответствующего счетчика и соответствующему входу соответствующего шифратора, начиная с второго

1181

1 дополнительного элемента И, и с соответствующими входами предыдущих шифраторов, а выход 11 -го дополнительного элемента И подключен к входу второго счетчика, выходы которого являются выходными шинами по наименьшему основанию, выходы ll-2

140 шифраторов подключены к соответствующим входам соответствующих сумматоров по модулям других оснований системы остаточных классов, выходы которых являются выходными шинами по соответствующим основаниям.

Изобретение относится к вычислительной технике и предназначено для преобразования мгновенного значения напряжения в код системы остаточных классов (СОК), с целью сопряжения различных датчиков с вычислительными устройствами, функционирующими в СОК, а. также в составе модемов аппаратуры цифровой связи, использующей коды СОК.

Цель изобретения — повышение быстродействия.

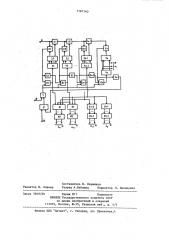

На чертеже изображена функциональная схема аналого-цифрового преобразователя в код СОК.

Предлагаемое устройство содержит блоки 1.1-1.!1-1 вычитания, компараторы 2.1-2.п, цифроаналоговые преобразователи 3.1-3. й, счетчики

4.1-4.п, инверторы 5.1-5. и, дополнительные элементы И 6.1-6.11, эле мент И 7, R5 -триггер 8, шифраторы

9.1-9.11-1, сумматоры 10.1-10.0-1 по модулям оснований СОК, кроме наименьшего, входную шину 11, шину 12 тактовых импульсов, шину

13 "Запуск", выходные шины 14 по соответствующим основаниям.

Устройство работает следующим образом.

В исходном состоянии счетчики 4, сумматоры по модулю 10 и триггер 8 установлены в нулевые состояния цифроаналоговые преобразователи (ЦАП) 3.1-3.11-1 имеют величины maroa квантования равные й-1

ЦАП 3.1 — h, ь. П P

11 и-2

ЦАП 3.2 А2 А .,, г 1 Р

ЦАП З.п-1- „,=a

ЦАП 3.h- h,„=А.

При этом напряжение на первом выходе ЦАП 3, подключенном к входу блоков 1 вычитания, преобразует входные коды а по правилу U à; Ь;,Напряжение на втором выходе ЦАП 3, подключенном к первому входу компаратора 2, преобразуется по правилу

U ; = а, А; > А;,т.е. всегда напряжения на одном из выходов ЦАП 3 превышает напряжение на другом его выходе на величину 6;,.

Компараторы 2 работают по следующему алгоритму.

Если напряжение, подаваемое на компаратор 2 по шине 11 или с выхода предыдущего блока 1 вычитания меньше, чем напряжение на выходе соответствующего ЦАП 3, то на выходе компаратора 2 имеется сигнал логического нуля, в противном случае логической единицы. В начальный момент времени по шине 13 поступает импульс "пуск", триггер 8 устанавливается в единичное состояние и через элемент И 7 с шины 12 поступают на элемент И 6 тактовые импульП-1 сы. Если U ) Л Г1 p, то высокий ло1ъ1

20

25 гический уровень с компаратора 2.1 разрешает прохождение тактовых импульсов на вход счетчика 4.1. При поступлении каждого тактового импульса напряжение на втором выходе

11-1

35 ЦАП 3.1 увеличивается на и П

fl-1

" 411 1- " С 11? Р1

Когда U<, превышает Б компаратор

2.1 запрещает поступление тактовых импульсов на вход счетчика 4.1. На

40 выходе блока 1.1 вычитания образуется напряжение

3 1

3а время счета счетчика 4. 1 на вход шифратора 9.1 поступает а „ импульсов ° При этом каждый раз на выходе шифратора. 9.1 появляется код

n-!

1 1p; pned р«! . Например, для СОК с

«и! основаниями p« = 5, Ip = 7, p = 11 поступает код (5 ° 7)тпой 11=2.

Таким образом, с поступлением каждого импульса на вход шифратора 9.1 содержимое сумматора по модулю 10,1 увеличивается на величину

H.1 г г«

«« pp«o «,В момент окончания счеГп

«и1 та счетчика 4.1 составляет величину п-1 с!„Г1 ; moJ Р„.

«=1

Если в исходном состоянии Vq

««-1

< Ь П Р1 то выходной сигнал логи«=! ческого нуля с компаратора 2.1 через инвертор 5.1 разрешает прохождение тактовых импульсов через элемент И

6.2 и запрещает через элемент И 6.1.

Таким образом, а„ = О.

Во втором цикле преобразования (если U< .- П„ д, > д ) на выходе элемента И 6.1 появляется а „ 1 импульсов, При этом на выходах шифратора !

Il- 2

9.1 появляются коды. (П О;1 woJ .

"n

«=1 и для приведенного примера (5)

mod 11=5. А на выходах шифратора 9.2

181140 4 и-Z пОявляются КОДЫ Г! I« p!!OJ 12 п 1 И

1«.=1 для примера (5) mod 7=5. Следовательно«по окончании поступления импульсов с выхода элемента И 6.2 в сумматоре 10.1 оказывается величина

11-R

«1-1 а„, (1р; ° аеП р,) то4рв т а в орнна—

«в1

««-

15 торе 1О. 2 величина,(nnn- . p jnnn pn-n

Дальнейшая работа устройства продолжается до тех пор, пока на

20 все сумматоры 10.1-10.!1-1 через шифраторы 9.1-9 11-.1 поступит а« импульсов с выхода элемента И 6.11, При этом сумма напряжений на выходах

ЦАП 3.1-3.vl равна величине аА. Нуле25 вой выходной уровень с компаратора

2.11через инвертор 5.1! устанавливает триггер 8 в нулевое состояние.

В сумматорах 10.1-10.Н-1 оказываются величины остатков О «Ф 2,„, к„ содержимое счетчика 4.й соответствует с !, На этом процесс преобразования напряжения U в цифровой код А за!

1 канчивается и коды остатков ж1, d, .q.",«2 ппо шинам 14 выводЯтсЯ из .Устройства.

1181140

Составитель В. Першиков

Техред А.Бабинец Корректор Л. Пилипенко

Редактор И. Бланар

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4

Заказ 5949/60 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5