Умножающий цифроаналоговый преобразователь

Иллюстрации

Показать всеРеферат

Ь УМИОЖАЮи1ИЙ .;ЩФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий источник эталонного напряжения, первая клемма которого подключена к общей шине, генератор тактовых импульсов, выход которого подключен к входу счетчика, И прямых и ti инверсных выходов которого подключены к соответствующим первым прямым и инверс- . ным входам блока сравнения, выход которого подключен к первому входу триггера, ( И-1) прямь1Х и ()1-1) инверсных вторых входов блока сравнения подключены к соответствующим прямьм и инверсньп-1 выходам регистра , П входов которого являются входными шинами преобразователя, первый и второй ключи, выходы которых объединены и подключены к первому входу фильтра, второй вход которого подключен к общей шине, а выход к неинвертирующему входу первого операционного усилителя, выход которого объединен с инвертирующим входом и является выходом преобразователя, отличающийся тем, что, с целью повышения точности преобразования , в него введены элемент 2И-2ШЖ, второй операционньш усилитель , блок модуляции-демодуляции с двухполупериодным преобразованием сигнала, аналоговый вход которого подключен к выходу второго операционного усилителя, первый цифровой вход объединен с вторым входом триггера и подключен к (п+1)-му прямому выходу счетчика, второй цифровой вход подключен к (п+1)-му инверсному выходу счетчика, первьй и второй аналоговые выходы подключены к информационным входам первого и второго ключей, третий аналоговый выход подключен к инвертирующему входу второго операционного усилителя, неинвертирующий : (Я вход которого подключен к второй с клемме источника эталонного напряжения , при этом h-и прямой и И -и инверсньй вторые входы блока сравнения являются соответственно первой и второй шинами постоянного логического сигнала, а И-и прямой и ц -и инверсньй выходы регистра подключеэо ны соответственно к первому и второму входам элемента 2И-2ИЛИ, третий и четвертый вход которого подключены соответственно к прямому и инСП версному выходам триггера, а прямой и инверсный выходы элемента 2И-2ИЛИ подключены соответственно к управляющим входам первого и второго кличей . 2. Преобразователь по п. 1, отличающийся тем, что блок модуляции-демодуляции с двухполупериодным преобразованием сигнала выполнен на фильтре, трансформаторе, первом, втором, третьем, четвертом ключах, информационные входы первого

COIQ3 СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) ® (ll) 3 0 А (51)4 Н 03 M 1/66

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3683048/24-24 (22) 26.12.83 (46) 23.09.85. Бюл. Р 35 (72) В.С. Малов и В,Н. Науменко (53) 681.325(088.8) (56) Титце Ч. и др. Полупроводниковая схемотехника, M.: Мир, 1982, с. 159, рис. 11-37.

Балакай В.Г. и др. Интегральные схемы АЦП и ЦАП,-М.: Энергия, 1978, с. 40, рис. 1-11. (54) (57) 1. УМНОЖАЮЩИЙ ЦИФРОАНАЛОГО-, ВЬ1Й ПРЕОБРАЗОВАТЕЛЬ, содержащий источник эталонного напряжения, первая клемма которого подключена к общей шине, генератор тактовых импульсов, выход которого подключен к входу счетчика, П прямых и rl инверсных выходов которого подключены к соответствующим первым прямьм и инверсным входам блока сравнения, выход которого подключен к первому входу триггера, (и -1) прямых и (и-1) инверсных вторых входов блока сравнения подключены к соответствующим прямым и инверсным выходам регистра, и входов которого являются входными шинами преобразователя, пер вый и второй ключи, выходы которых объединены и подключены к первому входу фильтра, второй вход которого подключен к общей шине, а выход - к неинвертирующему входу первого one рационного усилителя, выход которого объединен с инвертирующим входом и является выходом преобразователя, отличающийся тем, что, с целью повышения точности преобразования, в него введены элемент

2И-2ИЛИ, второй операционный усилитель, блок модуляции-демодуляции с двухполупериодным преобразованием сигнала, аналоговый вход которого подключен к выходу второго операционного усилителя, первый цифровой вход объединен с вторым входом триггера и подключен к (ц+1)-му прямому выходу счетчика, второй цифровой вход подключен к (и+1)-му инверсному выходу счетчика, первый и второй аналоговые выходы подключены к информационным входам первого и второго ключей, третий аналоговый выход подключен к инвертирующему входу второго операционного усилителя, неинвертирующий: вход которого подключен к второй клемме источника эталонного напряжения, при этом и -й прямой и И -й инверсный вторые входы блока сравнения являются соответственно первой и второй шинами постоянного логического сигнала, а t1 -й прямой и и -й инверсный выходы регистра подключены соответственно к первому и второму входам элемснта 2И-2ИЛИ, третий и четвертый вход которого подключены соответственно к прямому и инверсному выходам триггера, а прямой и инверсный выходы элемента 2И-2ИЛИ подключены соответственно к управляющим входам первого и второго ключей.

2, Преобразователь по п. 1, о тл и ч а ю шийся тем, что блок модуляции-демодуляции с двухполупе- риодным преобразованием сигнала выполнен на фильтре, трансформаторе, первом, втором, третьем, четвертом ключах, информационные входы первого

1181 и второго ключей объединены и являются аналоговым входом блока модуляции-демодуляции с двухполупериодным преобразованием сигнала, управляющий вход первого ключа объединен с управляющим входом третьего ключа и является первым цифровым входом блока модуляции-демодуляции с двухполупериодным преобразованием сигнала, управляющий вход второго ключа объединен с управляющим входом четвертого ключа и является вторым цифровым входом блока модуляции-демодуляции с двухполупериодным преобразованием сигнала, выходы первого и второго ключей подключены соответственно к началу и концу первичной обмотки трансформатора, средняя. точка которой подключена к общей шине, начало вторичной обмотки трансформатора является первым аналоговым выходом блока модуляции-демодуляции с двухполупериодным преобразованием сигнала и подключено к информационному входу третьего ключа, конец вторичной обмотки трансформатора является вторым аналоговым выходом блока модуляции-демоцуляции с двухполупериодным преобразованием сигнала и подключен к информационному входу четвертого ключа, выход которого является третьим аналоговым выходом блока модуляции-демодуляции с двухполупериодным преобразованием сигнала, объединен с выходом третьего. ключа и через фильтр подключен к общей шине и средней точке вторичной обмотки трансформатора.

Изобретение относится к автоматике и вычислительной технике и может быть использовано к системах обработки информации для обеспечения ввода информации на управляемые объекты, Цель изобретения — повышение точ" ности преобразования.

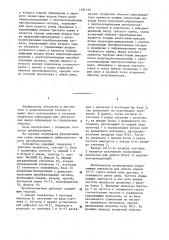

На чертеже изображена функциональ ная схема умножающего ци4роаналого- 1p вого преобразователя.

Устройство содержит генератор 1 тактовых импульсов, счетчик 2, блок

3 сравнения, регистр 4, первый 5 и и второй 6 ключи, триггер 7, элемент 2И-2ИПИ 8, фильтр 9, первый операционный усилитель 10, второй операционный усилитель 11, источник

12 эталонного напряжения, блок 13 модуляции-демодуляции с двухполу- 2О периодным преобразованием сигнала, включающий первый, второй, третий, четвертый ключи 14-17, трансформатор

18, фильтр 19.

Преобразователь работает следую- 25 щим образом.

С выхода генератора 1 тактовые импульсы f поступают на вход счетчика 2. Регистр 4 хранит установленный цифровой код И(). Импульсы и разрядов со счетчика 2 и (п-1) разрядов с регистра 4 поступают на блок 3, где происходит их поразрядное сравнение. В момент, когда сигналы со счетчика 2 равны сигналам с регистра

4, на выходе блока 3 формируется потенциал; поступающий на первый вход триггера 7 и определяющий сигнал конца временного интервала, пропорциональному входному коду N(t). Частота импульсов с выхода блока 3 равна частоте импульсов с выхода n-ro разря" да счетчика 2.

Выходы (п+1)-ro разряда счетчика

2 являются источником управляющих импульсов для работы блока 13 модуляа ции-демодуляции.

Длительности полупериодов управляющих импульсов для работы ключей

14-17 строго равны один другому, а скважность равна двум. Частота управляющих импульсов в два раза меньше частоты импульсов сравнения с выхода блока 3. Выходные импульсы триггера 7 по частоте и скважности строго соответствуют частоте и скважности управляющих импульсов, но по фазе оказываются сдвинутыми на величину временного интервала, пропорциональному входному коду N(t). Ha крайних выводах вторичной обмотки

1181

ВНИИПИ Заказ 5949/60 Тираж 871 Подписное

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная, 4 трансформатора 18 возникает переменное импульсное напряжение с частотой и скважностью управляющих импульсов. Выпрямленное напряжение на третьем выходе блока 13 по амплитуде и полярности всегда равно Uz . Отрицательная обратная связь позволяет стабилизировать также амплитуду переменного импульсного напряжения первым и втором выходах блока

131 которая становится равной U T, °

Управляющие импульсы с выхода триггера 7. поступают на элемент

2И-2ИЛИ 8, который пропускает входные сигналы с повторением или инверсией фазы в зависимости от управляющих сигналов на первом и втором входах элемента 2И-2ИЛИ 8, поступающих с знакового разряда регистра 4.

Инверсия фазы управляющих импульсов ключей 5 и 6 приводит к строго симметричной инверсии полярности его вьгходного напряжения без изменения амплитуды. Все изменения U зт прямопропорционально передаются на 25 выход предложенного умножающего ЦАП.

Все изменения. входного кода N{t) также приводят к соответствующему сдвигу фаз управляющих импульсов ключей 5 и 6 соответствующему изме- р нению выходного напряжения.

Преобразователь работает с и-разрядным двоичным кодом. Фактически (n-1) младших разрядов кода определяют амплитуду выходного напря35 жения ЦАП. Старший и-й разряд кода

1. 0 4 определяет полярность выходного напряжения.

Особенностью предлагаемого технического решения является то, что кодировка входного кода может быть различной. При любой кодировке блок

3 производит сравнецие и-разрядных двоичных кодов и частота импульсов с выхода блока 3 равна частоте импульсов с выхода п-го разряда счетчика 2. При работе предлагаемого ЦАП в режиме "Прямой код плюс знак" постоянный логический сигнал Бп на первой шине постоянного логического сигнала соответствует логической 1

iT u

При работе в режиме "Обратный код плюс знак" постоянный логический сигнал U соответствует логическому

"О". На второй шине постоянного логического сигнала присутствует сигнал

Uö инверсный сигналу первой шины.

Предлагаемый ЦАП может работать в режиме с двоично-смещенным кодом.

При этом все и разрядов входного кода необходимо подать на блок 3, связь и-го разряда входного кода, на первый и второй входы элемента

2И-2HJIli 8 отсутствует. В этом случае . осуществляется преобразование кода о в фазу в интервале 0-180 от начала периода управляющих импульсов. Нулевому значению кода соответствует выходное напряжение, равное входному максимальному значению кодавыходное напряжение с обратной полярностью по амплитуде равное входному U „ с погрешностью до дискрета.