Шифратор троичного кода

Иллюстрации

Показать всеРеферат

ШИФРАТОР ТРОИЧНОГО KO.riA, содержащий, два троичных логических элемента, причем первый и второй информационные входы шифратора соединены соответственно с первым и вторым входами сложения первого троичного логического элемента, третий и четвертьи информационные входы шифратора соединены соответственно с первым и вторым входами сло .жения второго троичного логического элемента, пятый и шестой информационные входы шифратора соединены соответственнос первыми входами вычитания первого и второго троичных логических элементов, третий и пяTbiii информационные входы шифратора соединены соответственно с вторыми входами вычитания первого и второго троичных логических элементов, о тличающийся тем, что, с целью упрощения шифратора, в нем первый и второй информационные входы шифратора соединены соответственно с третьими входами сложения и вычиi тания второго троичного логического элемента, седьмой и восьмой инСЛ формационные входы шифратора соединены соответственно с третьими входами сложения и вычитания первого троичного логического элемента, выходы первого и второго троичных логических элементов являются соответственно выходами первого и второго разрядов шифратора. 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИ Х

РЕСПУБЛИН

OIlNCAHHE ИЗОБРЕТЕНИЯ

Н ABT0PGH0IVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬГТИЙ (21) 3727117/24-24 (22) 22.02.84 (46) 23.09.85. Бюл, Р 35 (72) И.С. Кочнев и С.И. Шароватов (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 881731, кл. С 06 Г 5/04, 1980.

Авторское свидетельство СССР

У 750479, кл. С 06 F 5/02, 1978.

Авторское свидетельство СССР

520709, кл. Н 03 К 19/00, 1976. (54)(57) ШИФРАТОР ТРОИЧНОГО КОДА, содержащий. два трончных логических элемента, причем первый н второй информационные входы шифратора соединены соответственно с первым и вторым входами сложения первого троичного логического элемента, третий и четвертьп информационные входы шифратора соединены соответственно с первым и вторым входами сло,жения второго троичного логического

„„SU„„11 1154 A элемента, пятый и шестой информационные входы шифратора соединены соответственно с.первыми входами вычитания первого и второго троичньтх логических элементов, третий и пятьп1 информационные входы шифратора соединены соответственно с вторыми входами вычитания первого и второго троичных логических элементов, о тл и ч а ю шийся тем, что, с иелью упрощения шифратора, в нем первый и второй информационные входы шифратора соединены соответственно с третьими входами сложения и вычитания второго троичного логического элемента, седьмой и восьмой информационные входы шифратора соединены соответственно с третьими входами сложения и вычитания первого троичного логического элемента, выходы первого и второго троичных логических элементов являктся соответственно выходами первого и второго разрядов шифратора.

1181

Таблица 1

Состояние

30 выхода элемента

Таблица 2

Информационные входы

Выходы

35

0

1,2,3

2,3

10

1,2,3

2,3

Изобретение относится к вычислительной технике и может быть использовано при построении систем обра- ботки дискретной информации.

Цель изобретения — упрощение шифратора.

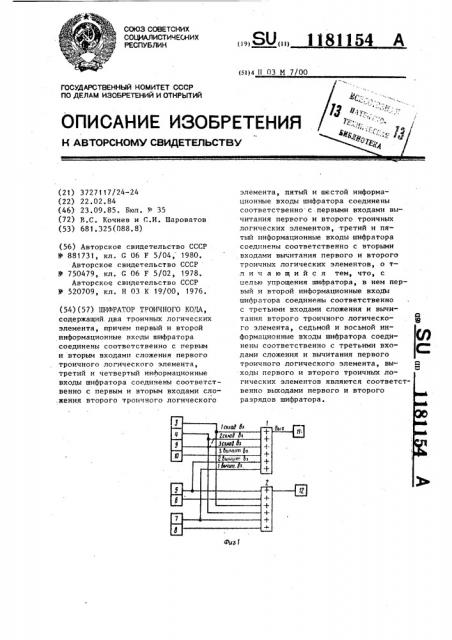

На фиг. 1 изображена схема блокшифратора троичного кода (1, О, 1), на фиг. 2 - фаэо-импульсная диаграмма его работы с условными обозначениями.lO

Шифратор содержит троичные логи<ческие элементы 1 и 2, информацион, ные входы 3-10 и выходы 11 и 12.

Устройство работает следующим образом. 15

Шифратор содержит два троичных логических элемента, каждый из которых выполняет троичные операции, описываемые табл. 1. Указанные операции образуют функционально полную 20 систему логических функций. Троичные логи..вские элементы могут быть реализованы, например, на магнитных логических ячейках.

Общее количество импульсов, поступающих на входы .

Склады- Вычитающие вающие

154 г

Обозначены также (фиг. 2) фазоимпульсные диаграммы 13 и 14, первой и второй фаз тактового питания, соответственно, диаграммы 15 — 22 сигналов на соответствующих входах 3-10, диаграммы 23-24 сигналов на выходах элементов 1 и 2 соответственно.

Система тактового питания шифратора — двухфазная, при этом сигнал положительный полярности на один из информационных входов 3-10 элементов 1 и 2 поступают через две фазы (один такт) передачи информации по элементам шифратора (фиг. 2).

Сигналы поступают на один из информационных входов во время тактового импульса первой фазы. Тактовым импульсом второй фазы считывается информация с элементов 1 и 2.

На один из информационных входов

3-10 подается сигнал положительной полярности, при этом на выходах

11 и 12 (на выходах элементов 1 и 2) появляются кодовые комбинации в троичной форме (по выходу 11 с естественным весом 3, по выходу 12-3), однозначно соответствующие информационному входу, согласно табл. 2. а

Тактовым импульсом первой фазы первого такта, согласно логике работы элемента, записанной в табл. 1, сигнал положительной полярности свхода 3 передается на первый вход сложения элемента 1 и третий вход

1181154

8-и

Л- импульсы д5уцпзндц испючника питаюя. Запись „+1

22

Фиг. Г

Составитель M. Аршавский

Техред А.Бабинец Корректор:,М. Максимишинец

Редактор M. Бланар

Заказ 5949/60 Тираж 871 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, R-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 сложения элемента 2, тактовым им- пульсом второй фазы сигналы положительной полярности с выходов 11 и

12 (с выходов элементов 1 и 2) выходят из шифратора, образуя выходную комбинацию (11), соответствующую сигналу на входе 3.

1-й Я Я И я b- g 7-д

ma m такт пакт такт така такт так

Аналогично (фиг. 1, 2 и табл. 2) происходит преобразования сигнала на последующих информационных входах 4-10, при этом на выходах сигналу положительной полярности соответствует код "1", а сигналу отрицательной полярности — код "1".

- - Запись „-1"

- - счшпы3ание „ i1 Счилыйюг „-1" cuumb4upep „С"