Преобразователь последовательного кода в параллельный

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ ПОСЖДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ, содержащий D-триггер, генератор импульсов, счетчик, С-вход которого соединен с выходом генератора импульсов, элемент И, дешифратор синхросигнала, регистр сдвига ,

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51)4 Н 03 M 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H ABT0PCH0lNY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬП ИЙ (21) 3728700/24-24 (22) 16.04.84 (46) 23.09.85 ° Бюл. №- 35 (72! А,K.Íîâèêîâ (53) 681.325(088.8) (56) Авторское свидетельство СССР

¹ 562814, кл. G 06 F 5/04, 1975.

Авторское свидетельство СССР

¹ 783789, кл. G 06 F 5/04, 1979. (54) (57) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ, содержащий D-триггер, генератор импульсов, счетчик, С-вход которого соединен с выходом генератора импульсов, элемент И, дешифратор синхросигнала, регистр сцвига,(2n+2) выходов которого, где n — разрядность кодового представления синхросигнала, соединены с входами дешифратора синхросигнала, выход которого соединен с первым входом элемента И, и блок контроля, отличающийся тем, что, с целью расширения класса решаемых задач путем обеспечения возможности преобразования фазоманипулированного представления кодов и повышения достоверности преобразования информации, в преобразователь введены блок пороговых элементов, блок элементов дифференцирования, первый и второй элементы ИЛИ, три элемента задержки, выходной регистр, формирователь импульсов, блок гальванической развязки, прямой и инверсный выходы которого соединены соответственно с первым и вторым входами блока пороговых элементов, а вход является первым разрядным входом преобразователя, второй разрядный вход которого соеди„„SU„„1181155 А нен с первым входом первого элемента ИЛИ и первым входом блока элементов дифференцирования, второй и третий входы которого соединены соответственно с первым и вторым выхода,ми блока пороговых элементов, первый выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с информационным входом регистра сдвига, тактовый вход которого соединен с выходом формирователя импульсов и через пер-. вый элемент задержки — с вторым входом элемента И, вход которого соединен с входом записи выходного регистра и через второй элемент задержки — с выходом импульсов сопровождения преобразователя, информационные выходы которого соединены с выходами выходного регистра, вход первого разряда которого соединен с выходом первого разряда регистра сдвига, выход (2n+1)-го разряда которого сое динен с входом второго разряда выходного регистра и первым входом блока ! контроля, входы с второго по к-й которого соединены соответственно с выходами с (2п+3)-й по (m-1)-й регистра сдвига и входами с третьего по (к-1)-й разряды выходного регистра, где к — разрядность входного информационного слова, а ш-2n+k+3, входы (к+2) и (к+3) разрядов которого соединены соответственно с прямым и инверсным выходами блока контроля, (к+1)-й вход которого соединен с выходом (ш+1)-ro регистра сдвига, выходы блока элементов дифференцирования соединены с входами второго элемента ИЛИ, выход которого соединен с синхровходом D-триггера, прямой выход которого соединен с входом сброса счетчика, выход переполнения которого соединен с входом формирователя импульсов, а выход заема

1181155 счетчика через третий элемент задержки соединен с входом сброса D-триггера, D-вход которого соединен с входом логической единицы преобразователя.

Изобретение относится к автоматике: и вычислительной технике и может найти применение в системах передачи данных по цифровым каналам для преобразования последовательного кода в параллельный.

Цель изобретения — расширения класса решаемых задач путем обеспечения возможности преобразования фазоманипулированного представления кодов и повышение достоверности преобразования информации.

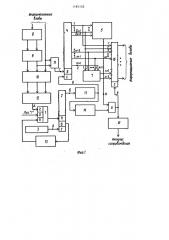

На фиг. 1 изображена структурная схема преобразователя последовательного кода в параллельный; на фиг. 2- 15 временные диаграммы, поясняющие его работу для случая, когда, например, п=3, k=16, р=4, И щ = 100... 10

И„ „= 0; на фиг. 3 — структурная схема выполнения дешнфратора синхросиг- 20 нала. .Преобразователь последовательного кода в параллельный содержит (фиг.1)

D-триггер 1, счетчик 2, генератор 3 импульсов, регистр 4 сдвига, дешифратор 5 синхросигнала, элемент И 6, блок контроля, блок 8 гальванической развязки который, например, может быть выполнен на трансформаторе со средней точкой, блок 9 порого- ЗО, вых элементов, блок. 10 элементов диф« ференцирования, первый 11 и второй 12 элементы ИЛИ, первый 13, второй 14 и третий 15 элементы задержки, выходной регистр 16, формирователь 17 импульсов

Дешифратор 5 синхросигнала содержит (фиг. 3) первую 18 и вторую 19 группы элементов НЕ, элемент -ИСКЛЮЧАЮЩЕЕ ИЛИ 20, первый 21 и второй 22 4g элементы И и элемент ИЛИ 23, выход которого является выходом дешифратора синхросигнала.

Ф

Преобразователь работает следующим образом. 45 исходном состоянии когда сигналы на информационные входы преобразователя не подаются, на выходе Р-триггера 1 (фиг. 1) установлен уровень логического "0". Тактовые импульсы частотой ZpF, где р— целое число, F — частота следования импульсов на информационных входах преобразователя, подаются с выхода генератора 3 импульсов (фиг. 2 А) на С-вход счетчика 2, с выхода которого тактовые импульсы частотой 2F (поз. Б) через формирователь 17 импульсов поступают на С-вход регистра 4 сдвига (поз. В), по фронту которых в последний записываются уровни логического "0" с выхода элемента ИЛИ 11 (поз. Г). Уровень логического "0" присутствует на выходе элемента ИЛИ 12 и (m+1)-м выходе регистра 4 сдвига, а также на выходах дешифратора 5 синхросигнала,, элемента И 6 и импульса сопровождения преобразователя (соответственно позиции Д-И и позиция "Импульс сопровождения"). На информационных выходах преобразователя присутствуют параллельный код последнего преобразованного слова.

Преобразуемое слово представляет собой последовательность логических "0" и "1", „причем начало слова (и разрядов) служит синхросигналом, далее следует к информационных разрядов и последним является разряд контроля четности. Преобразуемое слово поступает, например, из межприборной магистрали на вход блока 8 гальванической развязки и далее через блок 9 пороговых элементов — на блок 10 элементов дифференцирования и элемент ИЛИ 11. По каждому изменению, например, полярности сигнала, поступающего на информационные входы преобразователя, блок 10 элемен3 11811 тов дифференцирования формирует импульс синхронизации, который через элемент ИЛИ 12 подается на С-вход

D-триггера 1, устанавливая последний в "единичное" состояние. Уровень логической "1" поступает íà R-вход счетчика 2, сбрасывая его в "0".

На выходе заема счетчика 2 появляется уровень логической "1", который через элемент 13 задержки поступает 10 на R-вход D-триггера 1, устанавливая

его в исходное состояние. Счетчик 2 отсчитывает P импульсов генерато2 ра 3 импульсов, после чего формирователь 17 импульсов подает на С-вход

15 регистра 4 сдвига тактовый импульс, по фронту которого в регистр записывается соответствующий логический уровень с выхода элемента ИЛИ 11..

Последующие тактовые импульсы формирователь 17 импульсов формирует через каждые P импульсов с выхода генератора 3 импульсов.

Указанный процесс повторяется до тех пор, пока на входах дешифратора 5 синхросигнала не установится одна из определенных заданных кодовых комбинаций. В этом случае на выходе дешифратора 5 синхросигнала появляется уровень логической "1" и тактовый импульс с выхода формирователя 17 импульсов через элемент 14 задержки и элемент И 6 поступает на С-вход выходного регистра 16, обеспечивая запись в него информа- 35 ционной части преобразуемого слова

55 4 и служебных сигналов — вида синхросигнала и выходных сигналов блока 7 контроля четности. С выхода элемента И 6 через элемент 15 задержки поступает сигнал на выход импульса сопровождения преобразователя.

Дешифратор 5 синхросигнала работает следующим образом.

В исходном состоянии на выходе . элемента ИЛИ 23 (фиг. 3) присутствует уровень логического "0".

Если на входы дешифратора синхросигнала с 1-го по и поданы уровни логической "1", с (и+1)-ro по 2.пуровни логического "0", а на входы (2п+1) и (2n+2)-комбинации сигналов разного уровня, т.е. один разряд информационной части слова, представленный в виде фазоманипулированного сигнала, то на всех входах элемен та И 21 устанавливаются уровни логической "1". В результате чего на выходе дешифратора синхросигнала по-, является уровень логической "1".

Дешифратор синхросигнала срабагывает также в том случае, если на его входы с 1-го по и будут поданы уровни логического "0", с (и+1)-ro по 2n — уровни логической "1", а на входы (2п+1) и (2n+2). — комбинация сигналов разного уровня. В результате чего.на всех входах элемента И 22 устанавливаются уровни логической "1", а.следовательно - и на выходе дешифратора синхросигнала.

1181155

Инрориацивнные

Ьоды

1181155

Фиг,2

И

Мн рюрюацюнные Зыоды

Иипуяьс сцпро5вяйния

1181155

Zni

Редактор М.Бианар

Заказ 5950/61 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент"., г.ужгород, ул.Проектная, 4

it<1

2п.

En+1

Составитель М. Аршавский

Техред M.Íàäü Корректор Л.Пилипейко