Цифровое устройство фазовой синхронизации

Иллюстрации

Показать всеРеферат

ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ, содержащее последовательно соединенные цифровой фазовьй детектор, усредняющий блок и первый сумматор, последовательно соединенные опорный генератор, формирователь импульсов, блок добавления-вычитания импульсов, делитель частоты, регистр и второй сумматор, при этом выходы первого сумматора соединены с вторыми входами второго сумматора, выход делителя частоты соединен с входом цифрового фазового детектора и является выходом устройства, входом устройства является второй вход цифрового фазового детектора, отличающеес я тем, что, с целью повьшения точности синхронизации путе устранения фазовых девиаций опорного генератора в выходном сигнале в него введены сумматор по модулю два и два коммутатора, при этом выход знакового разряда регистра соединен с первым входом сумматора по модулю два, второй вход которого соединен с управляющим входом первого коммутатора , вторым входом блока добавлениявычитания импульсов и выходом знакового разряда усредняющего блока, i выход сумматора по модулю два соединен с управляющим входом второго коммутатора и третьим входом блока добавления-вычитания импульсов, выходы первого коммутатора соединены с первыми входами второго коммутатора, выходы которого соединены с вторыми входами первого сумматора, первые входы первого коммутатора являются 00 входами прямого кода постоянного числа, а его вторые входы являются входами дополнительного кода посел тоянного числа, вторые входы второ;о го коммутатора являются входами нулевого кода.

СОЮЗ СОВЕТСНИХ

3 Р

РЕСПУБЛИН

„„SU„„3 1359 (51)4 Н 04 ? 7/02

Ф

ОПИСАНИЕ ИЗОБРЕТЕНИЯ/

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР по делАм изоБРетений и ОтнРытий (21) 3729762/24-09 .(22) 20.04.84 (46) 23.09.85. Вюл. 9 35 (72) Н.И.Козленко, А.P.Ïîïîâ и Л.И.Алгазинова (53) 621.394.662.2(088.8) (56) Системы фазовой автоподстройки частоты с элементами дискретизации. Под ред. В.В.Шахгильдяна. M.:

Связь, 1979, с. 152, рис. 4.29..

Авторское свидетельство СССР и 1116545, кл. Н 04 L 7/02, 1983. (54) (57) ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ„ содержащее последовательно соединенные цифровой фазовый детектор, усредняющий блок и первый сумматор, последовательно соединенные опорный генератор, формирователь импульсов, блок добавления-вычитания импульсов, делитель частоты, регистр и второй сумматор, при этом выходы первого сумматора соединены с вторыми входами второго сумматора, выход делителя частоты соединен с входом цифрового фазового детектора и является выходом устройства, входом устройства является второй вход цифрового фазового детектора, о т л и ч а ю щ е ес я тем, что, с целью повышения точности синхронизации путем устранения фазовых девиаций опорного генератора в выходном. сигнале в него введены сумматор по модулю два и два коммутатора, при этом выход знакового разряда регистра соединен с первым входом сумматора по модулю два, второй вход которого соединен с управляющим входом первого коммутатора, вторым входом блока добавлениявычитания импульсов и выходом знакового разряда усредняющего блока, выход сумматора по модулю два соединен с управляющим входом второго коммутатора и третьим входом блока добавления-вычитания импульсов, выходы первого коммутатора соединены с первыми входами второго коммутатора, выходы которого соединены с вторыми входами первого сумматора, первые входы первого коммутатора являются входами прямого кода постоянного числа, а его вторые входы являются входами дополнительного кода постоянного числа, вторые входы второго коммутатора являются входами нулевого кода.

1181159

Изобретение относится к радиотехнике, и может быть использовано для фазовой синхронизации в приемниках дискретной информации.

Цель изобретения — повьппение точности синхронизации путем устранения фазовых девиаций опорного генератора в выходном сигнале.

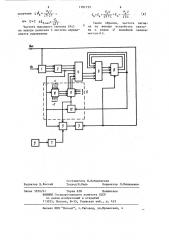

На чертеже представлена струк турная электрическая схема цифрового 10 устройства фазовой синхронизации.

Цифровое устройство фазовой синхронизации содержит цифровой фазовый детектор 1, усредняющий блок 2, делитель 3 частоты, первый сумматор 4, блок 5 добавления-вычитания импульсов, второй сумматор 6, формирователь 7 импульсов, регистр 8, опорный генератор 9, первый коммутатор 10, второй коммутатор 11, сумматор 12 по модулю два.

Цифровое устройство фазовой синхронизации работает следующим образом.

На вход цифрового фазового детек- 2 тора 1 поступает входной сигнал с выхода делителя 3. В усредняющем .блоке 2 происходит усреднение значений кода фазового рассогласования.

Первый и второй сумматоры 4 и 6, регистр 8, блок 5, делитель 3 частоты выполняют функции цифрового перестраиваемого генератора.

Изменение кода на выходе усредняющего блока 2 вызывает приращение

Qf частоты на выходе устройства. Код на выходе усредняющего блока 2 будет меняться до тех пор, пока выходной .сигнал не подстроится под входной.

Расмотрим работу цифрового перестраиваемого генератора.

На первые входы первого сумматора 4 поступает код И, определяющий частоту выходного сигнала. А знако45 вый разряд этого кода подается на второй вход сумматора 12, на управляющий вход первого коммутатора 10 и на второй вход блока 5. На первый вход сумматора 12 поступает знаковый разряд регистра 8. Сумматор 12

50. производит сравнение знака кода U со знаком числа y(n), хранящегося в регистре 8 в момент времени

= nT, где t = 0, 1, 2, 3, Т = f — частота импульсов, Кт постуйающих на тактовый вход регистра 8.

Если знаки чисел U и y(n) совпадают (SignU Sign y(n)$, то на первый сумматор 4 одается код постоянной величины С, знак которой противоположен знаку кода U. Если знаки чиселП и у(п)различны, то на входы второго слагаемого первого сумматора 4 с выхода второго коммутатора 11 снимается нулевой код. Результат, полученный в первом сумматоре 4, складывается во втором сумматоре 6 с содержимым у(п) регистра 8. В моменты прихода тактовых импульсов сумма, вычисленная во втором сумматоре 6, переписывается в регистр 8. Тактовые импульсы формируются в делителе 3 частоты делением частоты опорного генератора 9 в

K Раз (fz =, rpe К = 1,2,3...).

Значение кода, записываемого в регистре 8 в момент времени — (и+1) Т (+")=U+V()-C. Г („) () () 5(Z g) "R 0 y»Q u = Z

sigh 0+ Б -в Z где y(n) — значение кода, записываемого в регистр 8 в момент времени t=n -Т

С . — код постоянной величины,.

По знаку y(n+1) производят коррекцию Ч (п)-,фазы регистрирующих импульсов сдвигом на величину Уо (У(п1,0).

Для приращения фазы аЧ (и) выходного сигнала S(t) в момент времени

= и Т можем записать q („) y s t>>(nn),u), .*..,(.) =, (" )-, (1.

Суммируя левую и правую части уравнений (1) и (2) в пределах от

К до K+P-1 и подставляя значение суммы от Spy(n), Uj из уравнения (1) в (2), получаем (к+ г) (к1

Выражая приращения фазы выходного сигнала .за время t = PT через приращение частоты (< p) g (K)=2 » и f РТ, (3}

1181159

vu eu о g o

В= о 27)ТС 0 г)1С

Составитель Н.Лебедянская

Техред М, Надь Корректор Л.Пилипенко

Редактор П.Коссей

Заказ 5950/61 Тираж 658 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r.Óæãoðîä, ул.Проектная, 4 з чеU получаем е е

#СТ лри U=C

5" " 27Т

Частота выходного сигнала S(e) на выходе делителя 3 частоты определяется выражением

Таким образом, частота сигна5 ла на выходе устроиства связана с кодом U линейной зависимостьв(4 1