Измеритель фазовых сдвигов

Иллюстрации

Показать всеРеферат

ИЗМЕРИТЕЛЬ ФАЗОВЫХ СДВИГОВ, содержащий на входе блок высоких частот, два выхода которого соединены с входами смесителей, о т л ичающийся тем, что, с целью повьппения быстродействия при сохранении высокой точности путем устранения амплитудно-фазовой погрешности вследствие проведения измерений при двух значениях опорной частоты и обработки результатов измерений, в него введены вычислительный блок, синтезатор частот, коммутатор, ба .лансньш модулятор, фильтр и блок управления, причем первые два входа вычислительного блока подключены к выходам смесителей, вход синтезатора частот соединен с выходом одного из смесителей, первый выход синтезатора частот подключен к третьему входу вычислительного блока, второй вьЕсод - к первому входу балансного i модулятора, а-третий и четвертый выходы через коммутатор - к второму входу балансного; модулятора, при этом выход (балансного модулятора через фильтр соединен с вторыми входами смесителей, кроме того, вход блока управления подключен к выходу вычислительного блока, а выходы соединены с -управляющими входами коммутатора и вычислительного блока.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСИИХ

РЕСПУБЛИК (51)4 С 01 R 25/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPGKOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3667282/24-21 (22) 28.11.83 (46) 30.09.85. Бюл. ¹ 36 (72) В.Л. Кофанов и В.Я. Николаев (71) Винницкий политехнический институт (53) 621.3 17.77(088.8) (56) 1. Поздняков И.К. Определение амплитудных погрешностей фазометров.—

В кн.: Исследования в области радиотехнических измерений. — Труды институтов Комитета Стандартов), вып. 70 (130). — М.: Стандартгиз, 1963.

2. Манасевич В. Синтезаторы частот.

Теория и проектирование. — M.: Связь, 1979, с. 320-324, рис. 7.19.

3. Вишенчук И.М. и др. Электромеханические.и электронные фаэометры.—

М.-Л.: Госэнергоиздат, 1962, с. 292. (54) (57) ИЗМЕРИТЕЛЬ ФАЗОВЫХ СДВИГОВ, содержащий на входе блок высоких частот, два выхода которого соединены с входами смесителей, о т л ич а ю шийся тем, что, с целью повышения быстродействия при сохра„„SU„„11 24 4 A нении высокой точности путем устранения амплитудно-фазовой погрешности вследствие проведения измерений при двух значениях опорной частоты и обработки результатов измерений, в него введены вычислительный блок, синтезатор частот, коммутатор, ба.лансный модулятор, фильтр и блок управления, причем первые два входа вычислительного блока подключены к выходам смесителей, вход синтезатора частот соединен с выходом одного из смесителей, первый выход синтезатора частот подключен к третьему входу вычислительного блока, второй выход — к первому входу балансного i модулятора, а третий и четвертый выходы через коммутатор — к второму входу балансного модулятора, при этом выход (балансного модулятора через фильтр соединен с вторыми входами смесителей, кроме того, вход блока управления подключен к выходу вычислительного блока, а,выходы со динены с .управляющими входами коммутатора и вычислительного блока.

1182434

Изобретение относится к фазоизмерительной технике и может быть использовано для измерения разности фаз сигналов, фазочастотных характеристик и группового времени запаздывания радиоустройств.

Цель изобретения — повышение быстродействия при сохранении высокой точности путем устранения амплитудно-фазовой погрешности вследствие .проведения измерений при двух значениях опорной частоты.

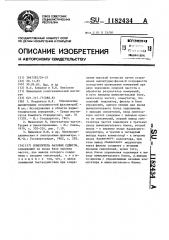

На чертеже приведена структурная схема измерителя.

Измеритель содержит блок 1 высо- 15 ких частот, смесители 2 и 3, вычислительный блок 4, синтезатор 5 частот, коммутатор 6, балансный модулятор 7, фильтр 8 и блок 9 управления.

К входу измерителя подключен блок 1 20 высоких частот, два выхода которого соед; нены с входами смесителей 2 и 3, первые два входа вычислительного блока 4 подключены к выходам этих

"месителей,.вход синтезатора 5 час- 25 тот соединен с выходом смесителя 3, первый выход синтезатора 5 частот подключен к третьему входу вычислительного блока 4, второй — к первому входу балансного модулятора 7, 3д а третий и четвертый через коммутатор 6 — к второму входу балансного модулятора .7, выход которого через фильтр 8 соединен с вторыми входами смесителей 2 и 3. Вход блока 9 управления подключен к выходу вычислительного блока 4, а выходы сое- . динены с управляющими входами коммутатора 6 и вычислительного блока 4.

Измеритель работает следующим <0 образом.

Блок 1 высоких частот предназначен для переноса измерений исследуемого фазового сдвига между вход= ными сигналами в диапазоне рабочих $ частот на фиксированную частоту 4).

При измерении фазовых характеристик исследуемые сигналы поступают на входы блока 1 высоких частот, содержащего, например, в каждом ка- Я нале смесители, входы которых соеди" нены с входами измерителя, и перестраиваемый гетеродин, соединенный с вторыми входами этих смесителей, причем частота гетеродина отлича- 55 ется от частоты исследуемых сигналов на величину с1 . В результате преобразования частот на выходе. блока 1 образуются сигналы с частотой GJ, разность фаз между которыми равна исследуемой разности фаз между входными сигналами.

При измерении группового времени запаздывания на входы блока 1 высоких частот поступают, например, амглитудно-модулированные колебания с подавленной несущей, причем информация о задержке огибающей содержится в фазовом сдвиге модулирующей частоты О . В блоке 1 высоких частот, содержащем в каждом канале амплитудные детекторы, соединенные с входами измерителя, путем детектирования выделяются сигналы огибающей частоты ы, разность . фаз между которьп и пропорциональна исследуемому групповому времени запаздывания.

Смесители 2 и 3 и балансный модулятор 7 предназначены для устранения амплитудно-фазовой погрешности, возникающей в каналах измерителей при изменении амплитуд входных сигналов.

С помощью синтезатора 5 частот и балансного модулятора 7 достигается частота спектра сигнала на вторых входах смесителей 2 и 3, что дополнительно способствует повышению точности измерений.

В смесителях 2 и 3 сигнал частоты И с выходов блока 1 высоких частот преобразуется в колебания промежуточной частоты g . При этом роль гетеродинного сигнала с частотой Я вЂ” B.или & + Я выполняет напряжение на выходе балансного модулятора 7, которое через фильтр 8 поступает на вторые входы смесителей 2и 3.

В синтезаторе 5 частот из напряжения опорного генератОра и напряжения промежуточной частоты 17 поступающего на вход синтезатора

5 частот с выхода смесителя 3, известными методами деления, умножения и преобразования частот $2( формируются сигналы частот M + g

Я,+-Sl, Q, — Q, Напряжение с частотой M a g подводится к одному входу балансного модулятора 7 непосредственно, а на второй вход его с помощью коммутатора 6 поочередно подключаются сигналы с частотой Я, + Д и Q — П . В результате преобразования частот на выходе балансного модулятора 7 с помощью 1 1 Я 4% Щ2 Ч

25 фильтра 8 выделяются возникающие поочередно сигналы разностных частот G3--Q и И Я.

Пусть на входы смесителей 2 и 3 с выходов блока 1 высоких частот .поступают сигналы соответственно где (— исследуемый фазовый сдвиг (постоянными фазовыми сдвигами в каналах пренебрегаем, так как они учитываются при калибровке измерителя).

В первом положении коммутатора 6 к вторым входам смесителей 2 и 3 поступает сигнал а во втором положении — сигнал где Я,, Ч вЂ” фазовые сдвиги вносимые узлами 5-8.

Тогда на выходах смесителей 2 и 3 в первом положении коммутатора

6 выделяются сигналы промежуточной частоты где Ь,, Ь - дополнительные фазовые сдвиги, возникающие в первом и втором каналах измерителя, если напряжения U< и 0 отличаются от напряжений входных сигналов, при которых производилась калибровка измерителя.

Во втором положении коммутатора 6 доказанные сигналы имеют вид

0 б п(Й1 (f -Ц)4 hg 1 (3) 1 (й 92+ 4Я2) -- (4) причем фазовые сдвиги ЬЦ,, Ь ф приводящие к амплитудно-фазовой по82434 4 грешности Ь = Ь q — 5 ц>,,остаются

I прежними, т.к. в обоих положениях коммутатора 6 ампгитуда входных сигналов остается практически неизменной.

В вычислительном блоке 4 осуществляется измерение исследуемого фазового сдвига, обработка и индикация результатов измерений. Блок

4 содержит, например, последовательно соединенные триггерный фаэометр, схему совпадения, реверсивный счетчик импульсов, регистр и цифровой индикатор.

В первом положении коммутатора 6 на входы триггерного фазометра в вычислительном блоке 4, соединенные с выходами смесителей 2 и 3, поступают сигналы (1), (2), в ре2б зультате чего на выходе этого триггерного фазометра образуются импульсы, длительность которых пропорциональна разности фаз этих сигналов

Во втором положении коммутатора 6 длительность названных импульсов пропорциональна.разности фаэ сигналов (3), (4) На третий вход вычислительного блока 4, соединенными с входом схемы совпадения, поступает сигнал частоты заполнения (квантующей частоты), сформированный в синтезаторе 5 час4О тот. Второй вход схемы совпадения в вычислительном блоке 4 соединен с выходом триггерного фазометра, поэтому на выходе схемы совпадения поочередно образуется последова45 тельность импульсов, число которых пропорционально фазовым сдвигам (, И Ф2 °

С помощью блока 9 управления процесс измерения осуществляется в два такта. С выхода вычислительного блока 4, представляющего собой выход измерительного триггера, на вход блска 9 управления поступают импульсные сигналы промежуточной частоты Я, из которых в блоке 9 управления формируются импульсы, управляющие работой коммутатора 6 и вычислительного блока 4. В тече1182434

Составитель В.Быков

Редактор Л.Пчелинская, Техред А.Бабинец

Корректор В. Гирняк

Заказ 6101/44

Тираж 747 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 ние первого такта управляющий сигнал с выхода блока 9 управления подводится к коммутатору 6 и переводит его в первое положение. При этом сигналом с выхода блока 9 управления, поступающим на управляющий вход вычислительного блока 4, реверсивный счетчик в этом блоке

4 переводится в режим суммирования.

Последовательности импульсов с выхода элемента совпадения вычислительного блока 4 подключаются при этом к суммирующему входу счетчика блока 4; в результате чего в последнем записывается код, пропорциональный фазовому сдвигу

Во втором такте управляющими импульсами с выходов блока 9 управления коммутатор 6 переключается во второе положение и реверсивный счетчик в вычислительном блоке 4 переводится в режим вычитания, При этом на вычитающий вход счетчика блока 4 поступает число импульсов, пропорциональное фазовому сдвигу () .

Таким образом, в результате двух тактов измерительного цикла в счетчике блока 4 оказывается записанным код, пропорциональный фазовому сдвигу p,-(p, = 2q,причем амплитудно-фазовая погрешность dq с помощью такой обработки измерений исключается.

По окончании второго такта управляющим импульсом с блока 9 управления, поступающим на вход вычислительного блока 4, результирующий код, пропорциональный измеряемому фазовому сдвигу, переписывается из реверсивного счетчика блока 4 в регистр блока 4 и индицируется цифровым индикатором вычислительного блока 4. Далее процесс измерений повторяется.