Генератор случайных чисел

Иллюстрации

Показать всеРеферат

ГЕНЕРАТОР СЛУЧАЙНЫХ ЧИСЕЛ содержащий сумматор, генератор так товых импульсов, выход которого подключен к первому адресному вход первого блока памяти, первый выход которого подключен к первому входу умножителя, второй вход которого соединен с выходом источника равно мерно распределенных случайных чисел, выход умножителя подключен к входу первого регистра памяти, отличающийся тем, что с целью повышения быстродействия, в него введены второй и третий регистры памяти, первый и второй блоки целочисленного деления, а также второй блок памяти, при этом выход второго регистра памятиподключен к первому входу первого блока целочисленного деления, второй вход которого соединен с выходом умножителя, а выход первого блока целочисленного деления подключен к входу управления считыванием второго блока памяти, выход которого подключен к второму адресному входу первого блока памяти и к входу третьего регистра памяти, выход которого соединен с первым входом сумматора, выход которого является выходом устройства, второй выход первого блока памяти подключен к первому входу второго блока целочисленного деления, второй вход которого соединен с выходом первого регистра памяти, а выход - с вторым входом сумматора, выход генератора тактовых импульсов подключен к входу источника равномерно распределенньк случайных чисел.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК рц4 G 06 F 7/58

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3732345/24-24 (22) 28.04.84 (46) 30.09.85. Бюл. М - 36 (72) С.С. Гусев (71) Грозненское научно-производственное объединение "Промавтоматика" (53) 681.333(088.8) (56) Авторское свидетельство СССР

У 260969, кл. G 06 F 7/58, 1968.

Авторское свидетельство СССР

Р 857983, кл. С 06 F 7/58, 1979. (54)(57) ГЕНЕРАТОР СЛУЧАЙНЫХ ЧИСЕЛ, содержащий сумматор, генератор тактовых импульсов, выход которого подключен к первому адресному входу первого блока памяти, первый выход которого подключен к первому входу умножителя, второй вход которого соединен с выходом источника равномерно распределенных случайных чисел, выход умножителя подключен к входу первого регистра памяти, отличающийся тем, что, с целью повышения быстродействия, в него введены второй и третий ре„„SU„„1182516 гистры памяти, первый и второй блоки целочисленного деления, а также второй блок памяти, при этом выход второго регистра памяти подключен к первому входу первого блока целочисленного деления, второй вход которого соединен с выходом умножителя, а выход первого блока целочисленного деления подключен к входу управления считыванием второго блока памяти, выход которого подключен к второму адресному входу первого блока памяти и к входу третьего регистра памяти, выход которого соединен с первым входом сумматора, выход которого является выходом устройства, второй выход первого блока памяти подключен к первому входу второго блока целочисленного деления, второй вход которого соединен с выходом первого регистра памяти, а выход — с вторым входом сумматора, выход гене ратора тактовых импульсов подключен к входу источника равномерно

\ распределенных случайных чисел.

1182516

1с= Р+ d

Составитель И.Столяров

Редактор М.Циткина Техред С..Мигунова Корректор Е.Сирохман

Заказ 6108/48

Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Изобретение относится к вычислительной технике и может быть использовано для статистического моделирования сложных систем, решения задач теории надежности.

Цель изобретения — повышение быстродействия устройства.

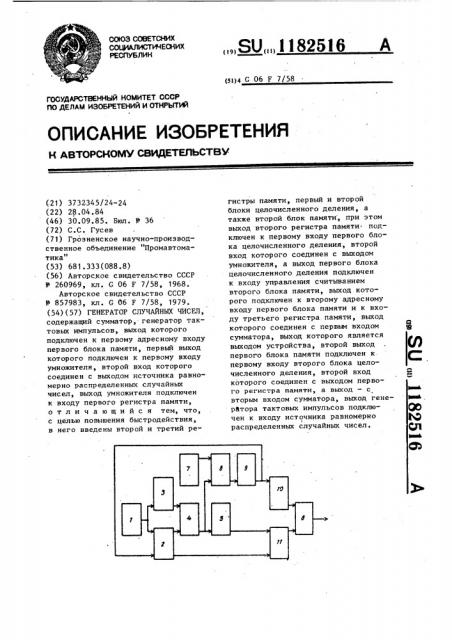

На чертеже представлена структурная схема генератора.

Генератор содержит генератор 1 тактовых импульсов, блок 2 памяти, источник 3 равномерно распределенных случайных чисел, умножитель 4, регистр 5 памяти, сумматор 6, регистр 7 памяти, блок 8 целочисленного деления, блок 9 памяти, регистр 10 памяти, блок 11 целочисленного деления.

Генератор работает следующим образом.

В блок 2 памяти заносятся заранее рассчитанные значения сумм вероятностей отказов элементов системы - . В блок 9 памяти заносятся значейия о, в регистр 7 памяти значение Я,„;и . Работа генератора тактируется генератором тактовых импульсов 1. Все устройство запускается подачей импульса на первый вход блока 2 памяти и на вход источника 3 равномерно распределенных случайных чисел и поэтапно выполняет следующие операции. На первом этапе запускается источник 3 и считывается значение сумм из блока

2 памяти. На втором этапе по первому выходу блока 2 памяти на первый вход умножителя 4 поступает значение сумм у„, а на второй вход умножителя 4 - значение чис- ла „, поступающее с выхода источника 3. Случайное число Е из ин1 тервала (О, ф ), равное произнедению значения из блока 2 памяти и числа, поступает на вход регистра 5 памяти и на второй вход блока 8 целочисленного деления.

5 На первый вход блока 8 поступает значение Д,„;„ с выхода регистра 7 памяти. На третьем этапе производится запись значения в регистр 5 памяти и деление нацело значения

10 с на значение 9„„„ = z/ .3.

На четвертом этапе этот результат поступает на вход блока 9 памя15 ти, после чего на вход регистра

10 памяти и на второй вход блока 2 памяти поступает приближенное значение номера элемента = о „.На пятом этапе производится считыва20 ние значения суммы у, хоанящег гося в блоке 2 памяти, которое поступает на второй вход блока 11 целочисленного деления, на первый вход которого поступает значение

25 случайного числа Е с выхода ре3 гистра 5 памяти. На шестом этапе производится деление нацело значег ния на значение ьо (Ei I t e l.

На седьмом этапе этот результат поступает на второй вход сумматора 6, а на первый вход сумматора поступает значение с выхода регистра 10 памяти. В сумматоре определяется сумма значений 0 и ct, которая согласно алгоритму, равна номеру отказавшего элемента в системе:

Далее процесс выбора очередного номера отказавшего элемента для следующего испытания повторяется, начиная с первого этапа.