Устройство для контроля радиоэлектронной аппаратуры

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ, содержащее первый и второй элементы ИЛИ, первые элементы совпадения, о т л ичающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены генератор тактовых импульсов, генератор импульсов сброса, регистр сдвига, формирователь контрольного сигнала, генератор тестов, первые дешифраторы , блоки постоянной памяти, вентиль, счетный триггер, второй элемент совпадения , блок оперативной памяти, преобразователь кодов и индикатор, причем выход генератора тактовых импульсов соединен с синхровходами второго элемента совпадения, формирователя контрольного сигнала, регистра сдвига и генератора импульсов сброса, Соединенного выходом с установочными входами блока оперативной памяти, регистра сдвига, с р -входом счетного триггера и с установочным входом формирователя . контрольного сигнала, соединенного выходом через генератор тестов с выходами устройства, а непосредственно с информационным входом регистра сдвига, соединенного выходами с первыми входами соответствующих первых элементов совпадения, соединенных вторь ми входами через соответствующие первые дешифраторы с соответствующими входами устройства, а выходами - с входами соответствующих блоков постоянной памяти и с входами первого элемента ИЛИ, соеi диненного выходом с первым входом вентиля, соединенного вторымвходом с инверсным выходом счетного триггера , выходом - с С-входом счетного триггера, соединенного инверсным выходом с вторым входом второго элемента совпадения, соединенного третьим входом с выходом второго элемента ИЖ, соединенного входами с выходами соответств%тощих блоков пос00 тоянной памяти, информационный вход IsD блока оперативной памяти соединен 01 с выходом второго элемента совпадения выход через преобразователь кодов с входом индикатора. 2. Устройство по п. 1, о т л и .чающееся тем, что формирователь контрольного сигнала содержит счетчик, соединенный счетным входом с синхровходом фopмlipoвaтeля, установочным входом - с установочным входом формирователя, выходами с входами второго дешифратора, соединенного выходами с выходами формирователя.

СООЗ СОВЕТСНИХ

СОЩ1АЛИСТИЧЕСНИХ

РЕСПУБЛИН д

/ Q

ОПИСАНИЕ ИЗОБРЕТЕНИ

И ABTOPCHGMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3731091/24-24 (22) 16,04.84 (46) 30.09.85. Бюл. И- Зб (72) В,А. Пономарев и 10.Н. Горбунов (53) 681.326(088.8) (56) Авторское свидетельство СССР № 264793, кл. r. Об F 15/46, 1969.

Вайда П.П. О диагностике цифровых устройств методом контроля последовательности импульсов.-В сб;:

Электроника и моделирование. — Киев, Институт математики АН УССР, 1977, вып. 15 с. 100, рис. 2. (54)(57) 1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ, содержащее первый и второй элементы ИЛИ, первые элементы совпадения, о т л ич а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства, в него введены генератор тактовых импульсов, генератор импульсов сброса, регистр сдвига, формирователь контрольного сигнала, генератор тестов, первые дешифраторы, блоки постоянной памяти, вентиль, счетный триггер, второй элемент совпадения, блок оперативной памяти, преобразователь кодов и индикатор, причем выход генератора тактовых импульсов соединен с синхровходами второго элемента совпадения, формирователя контрольного сигнала, регистра сдвига и генератора импульсов сброса, соединенного выходом с установочными входами блока оперативной памяти, регистра сдвига, с -входом счетного триггера и с (5t)4 6 06 Р !5/46 G 01 R 31/28 установочным входом формирователя контрольного сигнала, соединенного выходом через генератор тестов с выходами устройства, а непосредственно — с информационным входом регистра сдвига, соединенного выходами с первыми входами соответствующих первых элементов совпадения, соединенных вторыми входами через соответствующие первые дешифраторы с соответствующиии входами устройства, а выходами — с входами соответствующих блоков постоянной памяти и с входами первого элемента ИЛИ, соединенного выходом с первым входом вентиля, соединенного вторым входом с инверсным выходом счетного триггера, выходом — с C-входом счетного триггера, соединенного инверсным выходом с вторым входом второго элемента совпадения, соединенного третьим входом с выходом второго элемента ИЛИ, соединенного входами с выходами соответствующих блоков постоянной памяти, информационный вход блока оперативной памяти соединен с выходом второго элемента совпадения выход через преобразователь кодов— с входом индикатора.

2. Устройство по п. 1, о т л и.ч а ю щ е е с я тем, что формирователь контрольного сигнала содержит счетчик, соединенный счетным входом с синхровходом формирователя, установочным входом — с установочным входом формирователя, выходами с входами второгодешифратора,соединенного выходамис выходамиформирователя.

1182541

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля радиоэлектронной аппаратуры.

Цель изобретения — расширение 5 функциональных возможностей устройства.

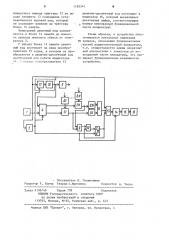

На чертеже изображена схема устройства.

Устройство содержит генератор тактовых импульсов, генератор 2 импульсов сброса, формирователь 3 контрольного сигнала, регистр 4 сдвига, генератор 5 тестов, первые дешифраторы б. 1 -6.8, где М вЂ” количество кон- 15 троя;*руi»,.rx ьункциональньгх частей аппаратуры, первые элементы 7.1-7. М совпадения, блоки 8. 1-8. М постоянной памяти, первый элемент 9 ИЛИ, вентиль lO, второй элемент ИЛИ 11, 20 счетный триггер 12, второй элемент

13 совпадения, блок 14 оперативной памяти, преобразователь 15 кодов, индикатор 16, счетчик 17 и второй дешифратор 18. 25

Лешифраторы 18, 6. 1-6. N выполняются на инверторах и элементах совпадения, конкретная схема дешифратора дня каждого значения дешифруемого кода различна. Генератор 1 тактовых 30 импульсов и генератор 2 импульсов сброса представляют собой генераторы прямоугольных имнульсов. Частота следования импульсов на выходе генератора 2 импульсов сброса значительно ниже, чем частота следования импульсов на выходе генератора 1 гактовых импульсов. Генератор

5 тестов генерирует тестовый много" разрядный код при приходе с формнро- 4р вателя 3 контрольного сигнала в виде импульса. Сигнал теста задается в промежутке между двумя тактовыми импульсами, Генератор 5 тестов может быть BbIIIoJIHPH на двухвходовых элемен-45 тах совпадения, на один вход которых заведен логический нуль или логическая единица, а на другой вход — сигнал с выхода формирователя 3 контрольного сигнала. В блоки 8. 1-8. и 50 постоянной памяти записываются двоичные значения кодов номеров, присвоенных функциональным частям конГ ролируемой аппаратуры. Блоки 8.1-8.Ж; могут быть выполнены на логических двухвходовых элементах совпадения, на один вход. которых постоянно задан сигнал логического нуля или единицы, а на второй вход — сигнал опроса элементов 7.1-7.hf совпадения.

Преобразователь 15 кодов преобразуеФ двоичный код в десятичный и представляет собой дешифратор. Блок 16 ин- дикации содержит цифровые индикаторы, например, семисегментные, выполненные на светодиодах, которые высвечивают десятичные цифры. Блок 14 оперативной памяти может быть выполнен на R5 -триггерах.

Устройство работает следующим образом.

Тактовые импульсы с выхода генератора 1 поступают на вход счетчика

17. В определенном такте на выходах счетчика 17 устанавливается код, по которому на выходе дешифратора 18 вырабатывается логическая единица.

При всех остальных состояниях счетчика 17 на выходе дешифратора 18 имеется логический ноль. Сформированный в формирователе 3 контрольный сигнал поступает на вход регистра 4 сдвига и на вход генератора 5 тестов. При появлении логической единицы на входе генератора 5 тестов он вырабатывает на выходе многоразрядный тестовый код, который поступает на вход контролируемой аппаратуры.

Тактовые импульсы с выхода генератора f поступают также на вход синхронизации регистра 4 сдвига, на вход генератора 2 импульсов сброса и на вход элемента 13 совпадения.

Логическая единица сформированного контрольного сигнала с выхода дешифратора 18 записывается в первый разряд регистра 4 сдвига. Последующими тактовыми импульсами логическая единица сдвигается из одного разряда регистра 4 сдвига в,цругой. Сигналы с выходов каждого разряда регистра сдвига 4 поступают на входы элементов 7.1-7.й совпадения.

С выхода генератора 1 тактовых импульсов тактовые импульсы поступают на вход генератора 2 импульсов сброса. Генератор 2 .импульсов сброса формирует из тактовых импульсов прямоугольные импульсы, имеющие более низкую частоту следования. Импульсы сброса поступают на вход установки в нуль счетчика t7, регистра 4, триггера 12, блока 14 памяти. Импульсы сброса, используемые для сброса счетчика t7 и регистра 4, задают

1182541 цикл контроля. Импульсы сброса триггера 12 и блока 13 совпадений могут быть более редкими. Они используются для обнуления цепей, вырабатывающих и индицирующих сигнал неисправности

Каядая 1-я функциональная часть контролируемой аппаратуры подключена к соответствующему дешифратору

6.1, который настроен на соответствующий этой части код, выдаваемый при ее исправности.

С выходов функциональных частей контролируемой аппаратуры сигналы через дешифраторы 6.1-6.N, в которых дешифрируемый контрольный код преобразуется в логическую единицу, поступают на входы элементов 7.1-7. Ж совпадения, которые последовательно опрашиваются сигналами с выходов ре" гистра 4 сдвига.

Такты времени, в которые на входы элементов 7.1-7..й совпадения посту— пают контрольные тестовые сигналы с выходов дешифраторов 6.1-6.К и сигналы опроса с выходов регистра

4 сдвига, совпадают. Сигнал опроса с регистра 4 сдвига поступает в,виде логической единицы. С выхода дешифратора 6. в случае исправной работы 30 контролируемой аппаратуры поступает на соответствующий элемент 7.1 совпадения сигнал логического нуля.

На выходе элемента 7.i совпадения в этом случае формируется логический нуль. В случае неисправной рабо ты аппаратуры с выхода,дешифратора

6. на вход элемента 7.i совпадения поступает логическая единица, которая при наличии логической еди- 4б ницы с регистра 4 сдвига проходит на выход элемента 7.i совпадения.

Если на выходе одного из элементов 7.1-7. И совпадения, например, элемента 7.) появилась логическая 4S единица, она поступает на вход соответствующего блока 8. памяти и опрашивает его. При опросе блока 8. памяти логической единицей на его выходе появляется код, соответствую- р щий номеру отказавшего узла. Этот код поступает на вход элемента ИЛИ 11 и через него на вход элемента 13 совпадения.

Сигналы с выходов элементов 7.1-7. 5 совпадения поступают также на входы элемента 9 ИЛИ и через него в открытый вентиль 10 — на вход синхрониэации счетного триггера 12. На другой вход вентиля 10 при этом поступает логическая единица с инверсного выхода триггера 12, так как триггер 12 находится с обнуленном состоя нии после прихода импульса сброса на вход 8 от генератора 2. Логическая единица с инверсного выхода триггера 12 поступает на вход элемента

13 совпадения и разрешает прохождение кодов с выхода блока 8.1 памяти через элемент 13 совпадения. На синхронизирующий вход элемента 13

-совпадения поступают тактовые импульсы с выхода генератора 1 тактовых импульсов.. Тактирование элемента 13 совпадения необходимо для исключения дешифраторных помех, которые возникают при работе дешифраторов 6. 1-6.N. После того, как сигнал блока 8. i памяти переписан в блок 14 памяти, триггер 12 устанавливается в ".единицу". Сигнал логического нуля с инверсного выхода триггера 12 поступает на вход вентиля 10 и на третий вход блока 13 совпадения и закрывает их для прохождения последующих сигналов неисправности. Триггер 12 работает и tr как защелка, обеспечивая отработку и индикацию первого по. времени опроса сигнала неисправности и запрещение индикации последующих сигналов неисправности.

Выходной код элемента ИЛИ 11 поступает на вход элемента 13 совпадения и в случае наличия на его других входах логической единицы с инверсного выхода триггера 1? и тактового импульса с генератора

1 проходит на вход элемента 13 совпадения и далее на вход блока 14 па- мяти.

В исходном состоянии на выходе триггеров блока 14 памяти имеется логический нуль. При наличии неисправности на В-входы триггеров блока 14 памяти поступают сигналы в виде логического нуля или в виде логической единицы, представленной импульсом, равным по длительности тактовому импульсу. Этими импульсами триггеры блока 14 памяти устанавливаются в "единицу ". В результате в триггеры блока 14 памяти за пйсывается код с, выхода элемента 13 совпадения. При закрывании элемента

13 совпадения сигналом "отсечки" с

) 182541

Составитель Н. Главизнина

Редактор F.. Копча Техред С.Мигунова Корректор А. Тяско

Заказ 6109/49 Тираж 709 Подписное

ВИИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 7(-35, Раушская наб., д. 4/5

Филиал ЕПП "Патент", r. Ужгород, ул. Проектная, 4 инверсного выхода триггера 12 на выходе элемента 13 совпадения устанавливается нулевой код, который не оказывает влияния на триггеры блока 14 памяти.

Записанный двоичный код запоминается в блоке 14 памяти до момента прихода, импульса сброса от генератора 2.

С выхода блока 14 памяти двоич- ный код поступает на вход преобразователя 15 кодов, в котором он пре-.образуется в двоична-десятичный код необходимый для работы индикатора

16, (, выхода преобразователя 15

l двоично-десятичный код поступает в индикатор 16, который высвечивает десятичные цифры, соответствующие номеру неисправной функциональноч части аппаратуры.

Таким образом, в устройстве обеспечивается визуальная индикация

1О номеров, отказавших функциональных частей радиоэлектронной аппаратуры, т.е. осуществляется режим оперативной диагностики с точностью до неисправной части аппаратуры, что рас15 ширяет функциональные возможности устройства.