Устройство для считывания информации из ассоциативной памяти

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ ИЗ АССОЦИАТИВНОЙ ПАМЯТИ, содержащее элементы И, элементы ИЛИ и элементы НЕ, причем первые входы первого и второго элементов И и выход первого элемента ИЛИ являются I соответственно входами третьего и :второго разрядов и выходом объединенного сигнала устройства, выход второго элемента И.ЛИ соединен с входом первого элемента НЕ, выход которого, подключен к вторым входам первого и второго элементов И, выход второго элемента И соединен с первым входом третьего элемента ИЛИ, выход которого подключен к входу второго элемента НЕ, выход которого соединен с третьим входом первого элемента И и первьш входом третьего элемента И, выходы элементов И, с первого по третий, являются соответственно выходами третьего, второго и первого разрядов устройства, адресными выходами которого являются выходы элементов НЕ, о т л и ч а ющ е е с я тем, что, с целью повышения надежности и быстродействия i устройства, в него введены четвертый и пятый элементы И, первые входы которых являются соответственно входами первого и нулевого разрядов устройства, а вторые входы соединены с четвертым входом первого и третьим; входом второго элементов И и являются управляющим входом устройства, яА причем выходы четвертого и пятого 00 элементов И подключены соответственr D сд но к первому входу второго элемента ИЛИ и второму входу третьего мента И и к вторым входам второго со и третьего элементов ИЛИ, входы первого элемента ИЛИ соединены с первы|Ми входами первого, второго, четвер|того и пятого элементов И,выход пятого элемента И является выходом нулевого разряда устройства.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (sl)4 С 11 С 15/00

ВСЕС6ВЗИДа

g 1 :, .:...,„„,,,„13/ зют д

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABT0PCHGMV СВИДЕТЕЛЬСТВУ

"ОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЬП ИЙ (21) 3731437/24-24 (22) 17.04.84 (46) 30.09.85. Бюл. Ф 36 (72) А.Д.Скляр, В.M.Òðóñôóñ, M.З.Шагивалеев и А.У.Ярмухаметов (71) Казанский ордена Трудового

Красного Знамени и ордена Дружбы народов авиационный институт им. В.Н.Туполева (53) 684.327(088.8) (56) Валиев К.А., Орликовский А.А.

Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах, M. Сов. радио, 1979, с. 259, 296, рис. 9.3.

Фостер К. Ассоциативные параллельные процессоры, М.: Энергоиздат, 1981, с. 240, с. 168, рис. 7.12, 7.13. (54) (57) УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ

ИНФОРМАЦИИ ИЗ АССОЦИАТИВНОЙ ПАМЯТИ, содержащее элементы И, элементы ИЛИ и элементы НЕ, причем первые входы первого и второго элементов И и выход первого элемента ИЛИ являются . соответственно входами третьего и

1 второго разрядов и выходом объединенного сигнала устройства, выход второго элемента ИЛИ соединен с входом первого элемента НЕ, выход которого подключен к вторым входам первого и второго элементов И, вы„„SU„„1182579 A ход второго элемента И соединен с первым входом третьего элемента ИЛИ, выход которого подключен к входу второго элемента HE выход которого соединен с третьим входом первого элемента И и первым входом третьего элемента И, выходы элементов И, с первого по третий, являются соответствеино выходами третьего, второго и первого разрядов устройства, адресными выходами которого являются выходы элементов НЕ, о т л и ч а ющ е е с я тем, что, с целью повышения надежности и быстродействия устройства, в него введены четвертый и пятый элементы И, первые входы которых являются соответственно входами первого и нулевого разрядов уст- . ройства, а вторые входы соединены с четвертым входом первого и третьим; входом второго элементов И и являются управляющим входом устройства, причем выходы четвертого и пятого элементов И подключены соответственно к первому входу второго элемента ИЛИ и второму входу третьего элемента И и к вторым входам второго и третьего элементов ИЛИ, входы первого элемента ИЛИ соединены с первы- ! ми входами первого, второго, четвертого и пятого элементов И,„выход пятого элемента И является выходом нулевого разряда устройства.

1 1182

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано для считывания информации из ассоциативной памяти, а также в различных устройствах управления, связанных с приоритетной обработкой сигналов запроса.

Цель изобретения — повышение надежности быстродействия устройства.

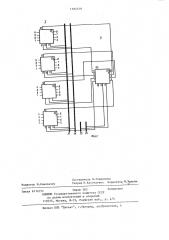

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 структурная схема многоуровневой структуры, организованной из предложенных устройств для считывания ин15 формации из ассоциативной памяти (например, для шестнадцати входов).

Устройство содержит входы нулевого 1, первого 2, второго 3, третьего 4 разрядов, выходы нулевого 5, первого 6, второго 7, третьего 8 раз20 рядов, выход 9 объединенного сигнала, адресные выходы 10 и 11, вход l2 выборки, элементы И 13-17 с первого по пятый, элементы ИЛИ 18-20 с перво25 го по третий, первый 21 и второй 22 элементы НЕ.

На фиг. 2 обозначены устройства 23 первого уровня и 23 второго уровня, адресные шины адреса. старших разрядов 24 и 25 и младших разрядов 26, 27 адреса. Объединение выходов 10, устройств 23 . в шины 26 и 27 выполнено с использованием монтажного

KK.

Предложенное устройство (фиг. 1) 35 работает следующим образом.

На входы 1-4 устройства поступает входной код. При использовании устройства в ассоциативной памяти входной код поступает с регистра откликов (не показан). Устройство преобразует входной код в код указателя, в котором единичный сигчал присутствует только в позиции, соответствующей первой из ячеек с положительным откликом на поиск по ассоциативному критерию. На выходах 10 и 11 элементов 21 и 22 формируется адрес этой ячейки (под первой ячейкой понимается здесь ячейки с меньшим адресом).

В случае использования устройства в системах управления входной код поступает с регистра управляющих признаков или регистра прерывания (не показаны). 55

Если входной код содержит единичные разряды, то элемент ИЛИ 18 формирует единичный сигнал на выходе 9.

579 2

Этот сигнал используется при построении многоуровневой структуры устройства. Код указателя в устройстве формируется элементами И 13-17 под управлением запрещающих сигналов (потенциалов логического нуля). Запрещающие сигналы и код адреса формируются элементами ИЛИ 19, 20 и элементами НЕ 21, 22. Для формирования кода указателя и кода адреса на вход 12 подается разрешающий сигнал (потенциал логической единицы).

Рассмотрим работу устройства в случае, когда во входном коде присутствуют единичные сигналы на входе 1 или 2 (адреса 00 или 01) ° Эти сигналы через элементы И 16 или 17 и элемент ИЛИ 19 поступают на элемент НЕ 21, На выходе элемента НЕ 21 формируется потенциал логического нуля,,являющийся запрещающим для прохождения сигналов со входов 3 и 4 через элементы И 13, 14. Одновременно этот потенциал формирует первый разряд кода адреса (00 или

01) на выход 10. Таким образом, сигналы на выходах 7, 8 (код указателя) и 10 (первый разряд кода адреса) могут быть единичными, если нет единичных разрядов входного кода с.адресами 00 или 01.

Аналогично, если во входном коде имеются первые единичные разряды на входах 1 или 3 (с адресами 00 или 10), они проходят через элементы И 17 или 14, элемент ИЛИ 20 на вход элемента НЕ 22, на выходе которого формируется потенциал логического нуля, являющийся запрещающим для прохождения единичных сигналов входного кода с входов 2 или 4 через элементы И 15 или 13. Одновременно этот потенциал формирует второй разряд кода адреса на выходе 11 (адреса 00, 10).

Таким образом, при любых сочетаниях сигналов входного кода в устройстве вырабатывается код адреса первой единицы во входном коде, нулевые разряды которого одновременно являются запрещающими сигналами для всех остальных единичных разрядов входного кода, за счет чего повышается надежность устройства.

При использовании многоуровневой структуры, например двухуровневой (фиг. 2), разряды входного кода делятся на четверки и поступают на входы 1-4 устройств 231 первого уров3 1 ня. Если в пределах четверки имеется единичный разряд входного кода, то формируется сигнал единицы на выходе 9 соответствующего устройства 23„.

Сигналы с выходов 9 устройств 23

1 образуют входной код для устройства 23 . На входе 12 устройства 232

2 постоянно поддерживается разрешающий сигнал.

Устройство 23 формирует код ука2 зателя, единичный разряд которого соответствует первой из четверок разрядов входного кода, содержащих единичные значения. Разряды кода указа теля с выходов 5-8 устройства 23 поступают на входы 12 соответствующих устройств 23 . При этом разрешаю1

1 щий сигнал поступает на вход 12 лишь того устройства 23„, чей сигнал с выхода 9 был первой единицей входного кода устройства 232 Таким образом, только одно из устройств 231 будет формировать код адреса и код указателя с единичным разрядом. Полный код указателя в многоуровневой структуре формируется из кодов указателей устройств 23„. Код адреса фор182579 4 мируется устройством 23> (старшие разряды на шинах 24 и 25) и одним из устройств 23„, выбранным единичным разрядом кода указателя устройства 23 (младшие разряды на шинах 26 и 27).

Входы элемента ИЛИ 19 соединены через элементы И 16 и 17 с входами 1 и 2 (нулевого и первого) разрядов

10 входного кода (фиг. 1) поэтому при комбинации входного кода 0110 единица по входу 3 может быстрее, чем в прототипе, пройти на элементы ИЛИ 20 и НЕ 22 и запретить прохождение первой единицы на выход 6. Единица с входа 1 после задержки в элементе И

17 поступит на элементы ИЛИ 19 и

HE 21.

Таким образом, на выходах 1О и 11 будет сформирован адрес с задержкой, примерно в два раза меньшей, чем в прототипе.за счет меньшего числа элементов, создающих задержку.

Формирование сигнала на выходе 9 также выполняется с меньшей задержкой, чем в прототипе, за счет исключения элементов И. гие.1

1182579

27 Ж

Редактор И. Ковальчук

Заказ 6112/51 Тираж 583

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Подписное

Ф

2

Составитель В.Гордонова

Техред Л.Кастелевич Корректор И.Эрдейи, г.Филиал ППП "Патент", г.ужгород, ул.Проектная, 4