Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее элементы памяти на первом и втором триггерах, дифференциальный усилитель, выход которого является первым выходом устройства, компаратор, первый вход которого является входом устройства, выход компаратора соединен с первым, входом первого триггера, генератор импульсов,, шину сброса, соединенную с первым входом второга триггера, и шину управления, отличающееся тем, что, с целью повышения точности устройства, в него введены первый и второй реверсивные счетчики, первый и второй цифроаналоговые преобразователи, элементы И, элемент ИЛИ-ЯЕ, инвертор и третий триггер, выход которого соединен с первым входом первого эле- :мента И, второй вход первого элемента И соединен с выходом генератора импульсов, входы третьего триггера соединены соответственно с выходом второго элемента И и с выходом инвертора , вход которого соединен с первым входом второго элемента И и с шиной управления, второй вход второго элемента .И соединен с выходом третьего элемента И и с первым входом второго триггера, второй вход которого соединен с выходом элемента ИЛИ-НЕ, первый выход второго триггера соединен с первым входом четверго элемента И и с первыми входами реверсивных счетчиков, выходы которых соединены соответственно со входами цифроаналоговых преобразователей , выход первого элемента И соединен с вторым входом четвертого элемента И и с вторыми входами реверсивных счетчиков, третьи входы которых соединены соответственно с выходом и с первым входом первого триггера, выходы цифроаналоговых преобразователей соединены соответ00 N9 ственно с входами дифференциального усилителя, выходы первого реверсивСП ного счетчика соединены с входами элемента ИЛИ-НЕ, выходы второго ре00 версивного счетчика соединены с входами третьего элемента И, второй вход компаратора соединен с выходом второго цифроаналогового преобразова;теля , выход четвертого элемента И является вторым выходом устройства, выход второго триггера является третьим выходом устройства.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (S))4 С 11 С 27 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3729122/24-24 (22) 19.04.84 (46) 30.09.85. Бюл. № 36 (72) А.Ф.Архипенко, С.К.Никифоров, И.P.Øåñòàêîâ, Е.В.Кириевский, В.П.Данилов и В.П.Малов (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

¹ 482815, кл. G 11 С 27/00, 1975.

Авторское свидетельство СССР

¹ 997584, кл. G 11 С 27/00, 1982. (54) (57) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО, содержащее элементы памяти на первом и втором триггерах, дифференциальный усилитель, выход которого является первым выходом устройства, компаратор, первый вход которого является входом устройства, выход компаратора соединен с первым входом первого триггера, генератор импульсов,. шину сброса, соединенную с первым входом второго триггера, и шину управления, о т л и ч а ющ е е с я тем, что, с целью повышения точности устройства, в него введены первый и второй реверсивные счетчики, первый и второй цифроаналоговые преобразователи, элементы И, элемент ИЛИ-HE инвертор и третий триггер, выход которого соединен с первым входом первого элемента И, второй вход первого элемента И соединен с выходом генератора импульсов, входы третьего триггера

„„Я0„„1182580 Д соединены соответственно с выходом второго элемента И и с выходом инвертора, вход которого соединен с первым входом второго элемента И и с шиной управления, второй вход второго элемента .И соединен с выходом третьего элемента И и с первым входом второго триггера, второй вход которого соединен с выходом элемента ИЛИ-НЕ, первый выход второго триггера соединен с первым входом четверго элемента И и с первыми входами реверсивных счетчиков, выходы которых соединены соответственно со входами цифроаналоговых преобразователей, выход первого элемента И соединен с вторым входом четвертого элемента И и с вторыми входами реверсивных счетчиков, третьи входы которых соединены соответственно с выходом и с первым входом первого триггера, выходы цифроаналоговых преобразователей соединены соответственно с входами дифференциального усилителя, выходы первого реверсивного счетчика соединены с входами элемента ИЛИ-НЕ, выходы второго реверсивного счетчика соединены с входами третьего элемента И, второй вход компаратора соединен с выходом второго цифроаналогового преобразователя, выход четвертого элемента И является вторым выходом устройства, выход второго триггера является третьим выходом устройства.

1182580

Изобретение относится к вычислительной технике и может быть использовано в аналого-цифровых преобразователях.

Целью изобретения является повыше- 5 ние точности устройства.

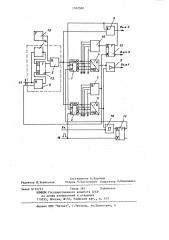

На чертеже представлена функциональная схема устройства.

Схема содержит реверсивные счетчики 1 и 2, цифроаналоговые преобразо- 10 ватели 3 и 4, элементы И 5-8, дифференциальный усилитель 9, компаратор 10, триггеры 11-13, инвертор !4, генератор 15 импульсов, элемент ИЛИНЕ 16, шину 17 управления, шину t8 15 сброса.

Устройство работает следующим образом.

В момент появления импульсного сигнала на шине 18 реверсивные счет- 20 чики 1 и 2 обнуляются, а счетчик 2 подготавливается к суммированию импульсов, вырабатываемых генератором 15 импульсов и прошедших через элемент И 5. Начиная с момента исчез-25 новения импульса на шине 18, разре-. шается запоминание напряжения, присутствующего íà входе устройства, Реверсивным счетчиком 2 начинается суммирование импульсов, а на вы- 30 ходе цифроаналогового преобразователя 3 формируется равномерно-ступенчатое напряжение Б„„д,равное

° И

О х цс п в (1) 35

МАРКС где U — напряжение питания цифроаналогового преобразователя 3;

N — количество импульсов, за- 40 фиксированное счетчиком 2, Nм„- максимальная емкость реверсивного счетчика 1.

Напряжение U«„> постоянно сравнивается с напряжением О „,имеющимся на входе устройства и подлежащем запоминанию. В момент их равенства на выоде компаратора 10 вырабатывается игнал, который переключает триггер 11, ыходным сигналом триггера 11 счетчик 1 подготавливается к регистрации импульсов, поступающих с выхода элемента И 5. Количество импульсов N„, зафиксированное реверсивным счетчиком 2 при Бвх — Пцс, Рпределяется 55 выражением т.е. оно пропорционально входному напряжению. В момент времени, когда U, = U

U = (3) цФп где N — количество импульсов, зарегистрированное счетчи.ком 1, М2 — максимальная емкость реверсивного счетчика 1.

При этом напряжение на выходе дифференциального усилителя 9 Пвьи „ > равно

"вык*м= Пц»> Пцмп 1 (4)

С Учетом, что 1,ц„кс= „щ„с иткс соотношение (3) примет вид

U и = — ---(N — N ) вы g.

= Я вЂ” „ Пекцц ï3 UB< (5) макс

Полученное соотношение (5) подтверждает, что на выходе дифференциального усилителя 9 напряжение Ue,x будет равно входному напряжению U ек независимо от разрядности реверсивных счетчиков 1 и 2. Поэтому в моменты регистрации счетчиком 2 максимального, а счетчиком 1 минимального количества импульсов выходными сигналами элементов И 7 и ИЛИ-НЕ 16 с помощью триггера 12 осуществляется периодическое и синхронное изменение режима работы реверсивных счетчиков 1 и 2 на суммирование или вычитание. Частота f „„ переключения цифроаналоговых преобразователей 3 и 4

IÃ зависит от входного напряжения UBx емкости счетчиков N и напряжения макс питания и определяется выражением

f (6) ц» Пек

N (1- — -) макс 4

Импульсы указанной частоты присутствуют на третьем выходе устройства частотного сигнала (вых.3).

Используя элемент И 8, на один вход которого поступает сигнал с прямого выхода триггера 12, а на другой — счетные импульсы генератоi 182580 ра 15, предварительно прошедшие через элемент И 5, на втором выходе получают последовательный цифровой код, пропорциональный входному напряжению и равный

N = N (1- — -) (7)

Uex

2 ма U

При наличии на шине 1 7 управления высокого уровня напряжения реализуется статический режим хранения входного напряжения. В этом случае прямым выходом триггера 13 запрещается прохождение через элемент И 5 импульсов генератора 12 на счетные входы реверсивных счетчиков 1 и 2.

В этом случае значение параллельных кодов указанных счетчиков будет определяться количествами зафиксированных в счетчиках 1 и 2 импульсов.

На выходах счетчика 1 состояние параллельного кода определяется количеством импульсов N, в соответствии

1 с выражением (2). При этом .на выходах реверсивного счетчика 2 присутствует цифровой код, соответствующий его максимальной емкости. При поступлении на шину 17 низкого уровня напряжения управления реализуется динамический режим хранения входного напряжения. В этом случае прямым выходом триггера 13 разрешается прохождение через элемент И 5 импульсов генератора 15 на счетные входы реверсивных счетчиков 1 и 2 и один из входов элемента И 8. Информацию о запомненном значении входного напряжения можно считывать с выходов устройства соответственно в видах последовательного цифрового ко5 да частотного или аналогового сигналов.

Длительность процесса статичес кого или динамического хранения инфЬрмации о входном напряжении на любом из выходов устройства никакими факторами не ограничивается и определяется лишь наличием напряжения питания на функциональных элементах устройства.

Повышение точности запоминания и хранения в предложенном устройстве достигается за счет замены формирования двух линейно-изменяющихся ф напряжений, у которых практически невозможно реализовать одинаковые постоянные времени и исключить их нелинейность, формированием двух равномерно-ступенчатых напряжений с помощью реверсивных счетчиков и цифроаналоговых преобразователей, работающих от одного генератора импульсов. Следовательно, при запоминании входного напряжения в виде разности двух равномерно-ступенчатых напряжений ошибка запоминания и хранения, вызванная нелинейностью и отличием их постоянных времени, отсутствует и при каждом изменении знаков угловых коэффициентов формируемых напряжений ее накопление йе происходит.

1182580

Составитель А.Воронин

Техред Я.Кастелевич Корректор Л.Пилипенко

Редактор И.Ковальчук

Филиал ППП "Патент", г.Ужгород, ул.Проектная, 4

Заказ 6112/51 Тираж 583 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5