Устройство для задержки импульсов

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ ЗАДЕР ККИ ИМПУЛЬСОВ, содержащее первый элемент И-НЕ, первый вход которого соединен с входной шиной и через инвертор с первым входом второго элемента И-НЕ, второй вход которого соединен с вторым входом первого элемента И-НЕ, выход которого соединен с входом запуска триггера, вход сброса которого соединен с выходом второго элемента И-НЕ, прямой выход - с первым входом третьего элемента И-НЕ, выход которого соединен с первым входом четвертого элемента И-НЕ, и выходную шину, отличающеес я тем, что, с целью повышения надежности, в него введены резистивно-емкостная интегрирующая цепь и пятьй элемент И-НЕ, выход которого соединен с вторым входом четвертого элемента И-НЕ, первый вход - с инверсным выходом триггера, второй вход - с входной шиной, второй вход третьего элемента И-НЕ соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с выходом резистивно-ёмкостной интегрирующей цепи, ВХОД которой соединен с выходом четвертого элемента И-НЕ. 2.Устройство по п. 1, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения регулирования времени задержки, в него введен переменньйрезистор, которьй подключен параллельно конденсатору резистивно-ёмкостной интегрирующей цепи. 3.Устройство по п. 1, отли,чающееся тем, что, с целью расширения функциональных возможностей путем получения импульсов удвоенной частоты, в него введена дополнительная выходная шина, которая соединена с выходом четвертого элемента И-НЕ.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (я) 4 Н 03 К 5/13

/

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3722868/24-21 (22) 06. 04. 84 (46) 30.09.85. Вюл. Ф 36 (72) Н.Д.Поршнева и В.И.Горшков (53) 62 1.374 . 2(088 .8) (56) Авторское свидетельство СССР

N9 817992, кл. Н 03 К 5/13, 21.05.79.

Авторское свидетельство СССР

Ф 921067, кл. Н 03 К 5/13, 17.07.80. (54) (57) 1. УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ

ИМПУЛЬСОВ, содержащее первый элемент

И-НЕ, первый вход которого соединен с входной шиной и через инвертор с первым входом второго элемента

И-НЕ, второй вход которого соединен с вторым входом первого элемента

И-НЕ, выход которого соединен с входом запуска триггера, вход сброса которого соединен с выходом второго элемента И-НЕ, прямой выход — с первым входом третьего элемента И-НЕ, выход которого соединен с первым входом четвертого элемента И-НЕ, и выходную шину, о т л и ч а ю щ е ес я тем, что, с целью повышения надежности, в него введены .резистивно-емкостная интегрирующая цепь и

„„SU„„1182649 А пятый элемент И-НЕ, выход которого соединен с вторым входом четвертого элемента И-НЕ, первый вход — с инверсным выходом триггера, второй вход - с входной шиной, второй вход третьего элемента И-HE соединен с первым входом второго элемента

И-НЕ, второй вход которого соединен с выходом резистивно-емкостной интегрирующей цели, вход которой соединен с выходом четвертого эле" мента И-НЕ.

2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей путем обеспечения регулирования времени задержки, в него введен переменный резистор, который подключен параллельно конденсатору резистивно-емкостной интегрирующей цепи ..

3. Устройство по п. 1, о т л и.ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей путем получения импульсов удвоенной частоты, в него введена дополнительная выходная шина, которая соединена с выходом четвертого элемента И-НЕ.

1182649

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники.

Цель изобретения — повышение на- 5 дежности и, кроме того, расширение функциональных возможностей путем обеспечения регулирования времени задержки и путем получения импульсов удвоенной частоты. 10

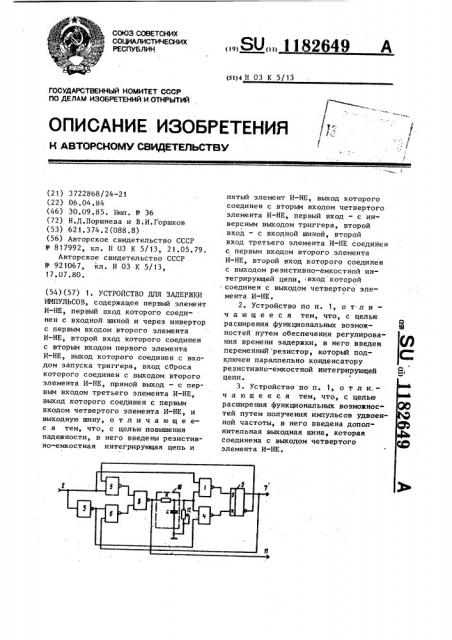

На чертеже приведена электрическая функциональная схема устройства для задержки импульсов.

Устройство для задержки импульсов содержит элемент 1 И-НЕ, первый I5 вход которого соединен с входной шиной 2 и через инвертор 3 с первым входом второго элемента 4 И-НЕ, второй вход которого соединен с вторым входом первого элемента 1 И-НЕ, вы- 20 ход которого соединен с входом запуска триггера 5, вход сброса которого соединен с выходом второго элемента

4 И-НЕ, прямой выход — с первым вхоРом третьего элемента 6 И-НЕ и с 25 выходной шиной 7, выход третьего элемента б И-НЕ соединен с первым входом четвертого элемента 8 И-НЕ, пятый элемент 9 И-НЕ, выход которого соединен с вторым входом четвертого 30 элемента 8 И-НЕ, первый вход - с инверсным выходом триггера 5, второй вход — с входной шиной 2, второй вход третьего элемента 6 И-НЕ соединен с первым входом второго элемента З5

4 И-НЕ, второй вход которого соединен с выходом резистивно-емкостной интегрирующей цепи 10, вход которой соединен с выходом четвертого элемента 8 И-НЕ, а также дополнитель- 40 ную выходную шину 11, соединенную.с выходом четвертого элемента 8 И-НЕ, и переменный резистор 12, который подключен параллельно конденсатору резистивно-емкостной интегрирующейцепи.45

Устройство работает следующим образом.

Перед подачей положительного импульса на шину 2 триггер 5 находится в нулевом состоянии, при этом на 50 его прямом выходе имеется низкий уровень, на выходах элементов б.и 8 ИALE " высокие уровни, на выходе элемента 8 И-НŠ— низкий уровень, а на выходах элементов 1 и 4 И-НŠ— вы- 55 сокие уровни.

В момент начала входного импульса на выходе элемента 9 И-НЕ формируется низкий уровень, после чего на выходе элемента 8 И-НЕ устанавливается высокий уровень. В интегрирующей цепи 10 происходит заряд емкости до уровня срабатывания элемента

1 И-НЕ, так как на другом его входе присутствует высокий уровень сигнала с шины 2. После этого. срабатывает триггер 5, на прямом выходе которого появляется высокий уровень выходного импульса, задержанный относительно входного, а на инверсном выходе — низкий уровень, после чего на выходе элемента 9 И-НЕ устанавливается высокий уровень, а на выходе элемента 8 И-НŠ— низкий уровень, что приводит к быстрому разряду емкости цепи 10. На выходе элемента

1 И-НЕ появляется высокий уровень, после чего на выходах всех элементов, кроме триггера 5 и инвертора 3, устанавливаются уровни, соответствующие исходному состоянию, которые не изменяются до момента окончания импульса на нине 2. После окончания импульса на шине 2 на выходе инвертора 3 появляется высокий уровень, при этом к обоим входам элемента

6 И-НЕ приложены высокие уровни, а на его выходе — появляется низкий уровень. На выходе элемента 8 И-НЕ присутствует высокий уровень. В интегрирующей цепи 10 происходит заряд емкости до уровня срабатывания элемента 4 И-НЕ, на его выходе появляется низкий уровень, и триг"

rep 5 переключается в нулевое состояние. На инверсном выходе триггера 5 появляется высокий уровень, на прямом выходе — низкий уровень, соответствующий окончанию формирования задержанного импульса на шине

7. После этого на выходе элемента

Ь И-НЕ устанавливается высокий уровень, а на выходе элемента 8 И-НЕ— низкий уровень, что приводит к быстрому разряду емкости цепи 1О.

На выходе элемента 4 И-НЕ появляется высокий уровень. Таким образом, устройство оказалось в исходном состоянии и готово к приему следующего входного импульса.

Переменный резистор 12 позволяет изменять постоянную времени цепи

10 и регулировать время задержки входного импульса и длительность импульсов удвоенной частоты на допол- нительной нине 11.