Делитель частоты с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ, содержащий счетчик с постоянным коэффициентом счета, два счетчика с переменным коэффициентом счета, два элемента ИЛИ, триггер коммутации, два запоминающих триггера, два элемента И-НЕ, три элемента И, первые входы которых соединены с входной шиной, второй вход первого элемента И со« динен с нулевым выходом триггера коммутации, единичный выход которого соединен с вторым входом второго элемента И, выход счетчика с постоянным коэффициентом счета соединен со счетным входом первого счетчика с -переменным коэффициентом счета, выход которого подключен к 5-входам триггера коммутации и первого запоминающего триггера, единичный выход которого соединен с вторым входом третьего элемента И, выход второго счетчшса с переменным коэффициентом счета подключен к R -входу триггера коммутации и к 6-входу второго запоминающего триггера, единичный выход которого соединен с третьим входом третьего элемента И, выход которого подключен к выходной шине и к первым входам первого и второго элементов И-НЕ, вторые входы которых соединены с выходами соответственно первого и второго элементов ИЛИ, а выходы - с R-входами соответствующих запоминающих триггеров, шина кода коэффициента деления десятки соединена с соответствующими информационными входами первого счетчика с переменным коэффициентом счета и входами первого элемента ИЛИ, а шина кода коэффициента деления единицы с соответствующими информационными входами второго счетчика О) с переменным коэффициентом счета и входами второго элемента ИЛИ, о тл и чающийся тем, что, с целью повьшения быстродействия и-точности при одновременном упрощении, введены.дополнительные S- и R-входы и триггер коммутации и дополнительные 5-входы и запоминающие триггеры, причем дополнительный 6-вход триггера коммутации соединен с выходом первого элемента ИЛИ, с входом сброса счетчика с постоянным коэффициентом счета и с дополнительным 5-вх6дом первого запоминающего триг-; гера, дополнительный R-вход триггера коммутации соединен с вы:4одом второго элемента ИЛИ и с дополнительным 5-входом второго запоминающего триггера , а нулевые выходы первого и второго запоминающих триггеров подключены к входам установки соответствующих счетчиков с переменным коэффициентом счета, при этом выход первого элемента И соединен со счетным входом счетчика с постоянным

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51)4 Н 03 К 23/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3665610/24-21 (22) 25. 11. 83 (46) 30.09.85. Бюл. № 36 (72) В.И. Антюфеев, Н.И. Власов и В.Н.Маслий (53) 621.374.4 (088.8) I (56) Авторское свидетельство СССР

¹ 875642, кл. Н 03 К 23 / 02, 19.02.84.

Авторское свидетельство СССР № 801254, кл. Н 03. К 23/00, 10.01.79.

/ (54) (57) ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ, соде ржащий счетчик с постоянным коэффициентом счета, два счетчика с переменным коэффициентом счета, два элемента ИЛИ, триггер коммутации, два запоминающих триггера, два элемента

-HE три элемента И, первые входы которых соединены с входной шиной, второй вход первого элемента И соединен с нулевым выходом триггера коммутации, единичный выход которого соединен с вторым входом второго элемента И,-выход счетчика с постоанным коэффициентом счета соединен со счетным входом первого счетчика с переменным коэффициентом счета, выход которого подключен к 5 -входам триггера коммутации и первого запоминающего триггера, единичный выход которого соединен с вторым входом третьего элемента И, выход второго счетчика с переменным коэффициентом счета подключен -к R -входу триггера коммутации и к 6-входу второго запоминающего триггера, единичный выход которого соединен с треть„„SU„„1182667 A им входом третьего элемента И, выход которого подключен к выходной шине и к первым входам первого и второго элементов И-НЕ, вторые входы которых соединены с выходами соответственно первого и второго элементов

ИЛИ, а выходы — с R -входами соответствующих запоминающих триггеров, шина кода коэффициента деления десятки соединена с соответствующими информационными входами первого счетчика с переменным коэффициентом счета и входами первого элемента ИЛИ, а шина кода коэффициента деления единицы — с соответствующими инфор- g мационными входами второго счетчика с переменным ноэ4фнцнентом счета и Q) входами второго элемента ИЛИ, о тл и ч а ю шийся тем, что, с целью повышения быстродействия и точ- Я ности при одновременном упрощении, введены, дополнительные 8- и R --входы и триггер коммутации и дополнительные 6-входы и запоминающие триггеры, причем дополнительный 5-вход триггера коммутации соединен с выходом первого элемента ИЛИ, с входом сброса счетчика с постоянным коэффициентом счета и с дополнительным

5-входом первого запоминающего триггера, дополнительный R -вход триггера коммутации соединен с вы2одом второго элемента ИЛИ и с дополнительным

6-входом второго запоминающего триггера, а нулевые выходы первого и второго запоминающих триггеров подключены к входам установки соответствующих счетчиков с переменным коэффициентом счета, при этом выход первого элемента И соединен со счетным входом счетчика с постоянным l182667 коэффициентом счета, а выход второ- второго счетчика с переменным коэфго элемента И вЂ” со счетным входом Фициентом счета.

Изобретение относится к импульсной технике и может быть использовано в цифровых синтезаторах частоты приемно-передающей аппаратуры, в устройствах дискретной автоматики 5 и вычислительной техники.

Цель изобретения — повышение быстродействия и точности при одновременном упрощении устройства.

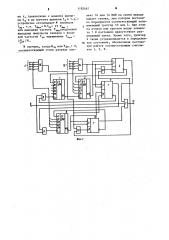

На фиг. 1 приведена электрическая 10 функциональная схема делителя частоты с переменным коэффициент деления; на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство содержит счетчик 1 с постоянным коэффициентом счета, вы-ход которого подключен к счетному входу первого счетчика 2 с переменным коэффициентом счета, выход которого соединен с 5-входами первого запоминающего триггера 3 и триггера

4 коммутации, первый, второй и третий элементы 5, 6 и 7 И, первые входы которых соединены с входной шиной

8, выход первого элемента 5 И соеди- 2э нен со счетным входом счетчика 1 с постоянным rîçôôèöèåíòoì счета, выход второго элемента 6 И соединен со счетным входом второго счетчика

9 с переменным коэффициентом счета, 30 выход которого подключен к R --входу триггера 4 коммутации и 8 -входу второго запоминающего триггера 10, единичные выходы первого и второго запоминающих триггеров 3 и 10 подключены срответственно ко второму и третьему входам третьего элемента 7 И, выход которого подключен к выходной шине 11 и к первым входам первого и второго элементов 12 и щ

13 И-НЕ, выходы которых подключены к Я -входам соответственно первого ,и второго запоминающих триггеров 3 и 10, нулевой выход первого запоминающего триггера 3 соединен с вхо- 4s. дом установки счетчика 2 с переменным коэффициентом счета, а нулевой выход второго запоминающего триггера

10 соединен с входом установки второго счетчика 9 с переменным коэффициентом счета, нулевой и единичный выходы триггера 4 коммутации соединен с вторыми входами соответственно первого и второго элементов 5 и

6 И, дополнительные 6-входы первого запоминающего триггера 3 и триггера коммутации 4 соединены между собой и подключены ко второму входу второго элемента 12 И-НЕ, к входу сброса счетчика 1 с постоянным коэффициентом счета и к выходу первого элемента 14 ИЛИ, входы которого соединены с информационными входами первого счетчика 2 с переменным коэффициентом счета и с шиной 15 кода коэффициента деления десятки, донолнительный 8-. вход второго запоминающего триггера 10 и дополнительный Й -вход триггера 4 коммутации соединены с вторым входом второго элемента

13 И-НЕ и подключены к выходу второго элемента 16 ИЛИ, входы которого соединены с информационными входами второго счетчика 9 с переменным коэффициентом счета и с шиной 17 кода коэффициента деления единицы .

Устройство работает следующим об- разом.

Счетчик 1 имеет постоянный коэффициент H<= 10 счета. Счетчики 2 и 9 имеют переменные коэффициенты Й и я9 счета соответственно от 1 до 10 которые устанавливаются с помощью сигналов двоичного кода на шинах

15 и .17 соответственно. Общий коэффициент деления устройства определяется из выражения

N Ni Nz 149 (Ой Nq=NAec "eA p где Наес 10Н "ед = Ng.

Последовательно включенные счетчики 1 и 2 обеспечивают получение слагаемого N4e (десятки), а счетчик 9з 1182667 4 слагаемого М (единицы) в общем ед второму входу элеме коэффициенте деления N за счет пооче- ного выхода триггер редной работы счетчиков 9 и 1, 2. Мо решающий сигнал. Зд менты окончания работы каждого из ду, что триггер 4 в счетчиков 2 и 9 запоминаются соответ- 5 чения устройства ус. ственно 3 и 10. Очередность работы вольно в состояние, счетчиков определяется выходными сиг- его единичном выход калами триггера 4, коммутирующими уровень логической элементы 5 и 6 И. При этом входные вполне допустимо, т импульсы с шины 8 проходят либо на -10 ность работы счетчи счетный вход счетчика 1, либо на на получение величи счетный вход счетчика 9. Очередность не влияет). начала работы счетчиков произволь- Согласно времени ная и определяется начальным со- первым начинает раб стоянием триггера 4 коммутации. 15 (разряд единицы). П

Рассмотрим работу устройства с этим счетчиком числ

Ф учетом временной диаграммы, приве- ных импульсов на er денной на фиг. 2, для которой Й = 23, ся сигнал, опрокиды пр ем ОеА = М9 = 3, КАec= 10 Н2 = времени 1! ) По перв

= 20, где Hq = 2. rep 10 (фиг.2б) и п

До подачи кода величины 1 на ши- триггер 4 (фиг.2в,г нах 17 и 15 присутствуют уровни ное состояние. При логических нулей, при этом на выхо- выходе последнего и дах элементов 16 и 14 ИЛИ, а соот- по вторым входам бл ветственно и на дополнительных 6 -вхо-25 6 И и деблокирующий дах триггеров 3 и 10 устанавлива- э том случае ч ер ез э ется уровень логического нуля. ные импульсы начин

В этом случае оба триггера 3 и 10 устанавливаются в единичное состоя. ние, при котором на втором и третьем входах элемента 7 И присутствуют разрешающие сигналы. Одновременно на нулевых выходах этих триггеров, а следовательно, и на входах установки счетчиков 2 и 9 устанавливаются 35 уровни логических нулей, при которых в этих счетчиках обеспечивается запись коэффициентов счета. В этом случае при подаче на шины 17 кода числа 3 и на шины 15 кода числа 2 <0 в счетчиках 9 и 2 осуществится запись коэффициентов счета Н = 3

= Мед и М = 2 = A„ . При поступлении на шину 8 входных импульсов (в момент времени 4 фиг.2а) начинается 45 работа устройства, при которой первый входной импульс проходит на выход элемента 7 И вЂ” шину 11 и через элемент 12, 13 И-НЕ опрокидывает по

; R-входу соответственно триггеры 3 и 10 в нулевое состояние, при котором !

; блокируется элемент 7 И и запрещается дальнейшее прохождение входных импульсов на выход устройства. Одновременно этот же входной импульс 55 поступает через элемент 6 И на счетный вход счетчика 9, который начинает счет числа H = 3. При этом по нта 6 И с единича 4 поступает разесь имеется в вимомент вклютановился произпри котором на е присутствует единицы. Это ак как очередков устройства ны М = М,4+ М е, ой„диа гр амме, отать счетчик 9 осле отсчета а " = 3 вход9 о выходе появитвающий (момент ому 5-входу триго первому R -входу

) в противоположэтом на единичном оявляется сигнал, окирующий элемент элемент 5 И. В лемент 5 И входают поступать на счетный вход счетчика 1, имеющего

И = 10, и счетчик 2 начинает счет числа Nд,,..е= H, > = 10 Й = 10 ° 2 = 20 входных импульсов. При этом на третьем входе элемента 7 И с выхода триггера 10 присутствует разрешающий сигнал в течение всего времени работы счетчиков 1 и 2 °

После отсчета счетчиком 2 числа

Н Аес= 20 входных импульсов, последний своим выходным сигналом опрокидывает по б-входам триггер 3 в единичное состояние, а триггер 4 — в начальное состояние (момент времени

1 ), при котором соответственно на вторых входах элементов 6 и 7 И появляются разрешающие сигналы. При этом следующий (очередной) входной импульс поступает .на вход счетчика

9 и повторяется вышеописанный цикл работы счетчика 9, и одновременно этот же входной импульс проходит через элемент 7 И на шину 11 (фиг.2е) и на -входы триггеров

3 и 10, возвращая их в исходное состояние (момент времени, фиг.2д и 2б соответственно), лри котором повторяется вышеописанный процесс работы устройства (начиная с момента времени 4 ) Таким образом, с момента времени и до момента време1182667 ни,(аналогично с момента времени Ф, и до момента времени t и т.д.) устройство отсчитывает М периодов

Твк, т.е. Т ы„= N Тв„= 23 Тщ„, или выходная частота Гвщ„следования выходных импульсов связана с входной частотой Fв выражением Гвь „= в выл

aF i„ / N „

Ь случаях, когда Мед или Й, с,= О, соответствующий этому разряду элемент 16 или 14 ИЛИ на своем выходе выдает сигнал, при котором постоянно блокируется соответствующий sanoминающий триггер 10 или 3. При этом на втором или третьем входе элемента 7 И постоянно присутствует разрешающий сигна. Кроме того, триггер

4 также устанавливается в определен1р ное состояние, обеспечивая постоянную работу соответствующих счетчиков 1, 2, 9.

1182667

Составитель А. Соколов

Редактор М. Бандура Техред А. Бабинец Корректор В. Бутяга

Заказ 6119/55 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4