Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ , содержащий регистр, прямые выходы триггеров которого через цифроаналоговый преобразователь соединены с первым входом компаратора, второй вход которого соединен с шиной преобразуемого сигнала, первую группу элементов И, выходы которых соединены с гходами обнуления соответствующих триггеров регистра, а первые входы - с выходами соответствующих элементов И второй группы, первые входы которых подключены к прямым выходам соответствующих триггеров регистра, кроме триггера младшего разряда, вторые входы - к выходам соответствующих элементов И третьей группы, первые входы которых соединейы с инверсными выходами соответствующих триггеров, кроме триггеров старшего и младшего разрядов, вторые входы - с выходами соответствующих элементов И третьей группы предьдущих разрядов, дополнительные входы обнуления триггеров регистра, кроме триггера старшего разряда, а также вход установки триггера старшего разряда и вход обнуления триггера управления объединены и подключены к шине запуска, прямой выход триггера управления соединен с шиной Готовность к преобразованию, инверсньй выход - с входом ждущего генератора, отличающийс я тем, что, с целью повышения быстродействия, в него введены элементы И четвертой группы и дополнительный элемент И, первьй вход которого соединен с выходом компаЖ ратора, второй вход объединен с (Л первыми входами элементов И четвертой группы и подключен к выходу ждущего генератора, вторые входы элементов И четвертой группы соединены с выходами соответствующих элементов И второй группы предьщущих разрядов, а выходы - с входами 00 установки соответствующих триггеров ю регистра, кроме триггера старшего О) фазряда, и триггера управления, причем выход дополнительного элемен та И подключен к вторьм входам элементов И первой группы, а прямой выход триггера мпадшего разряда регистра соединен с первым входом соответствующего элемента И первой и вторым входом соответствующего элемента И второй групп, а инверсный выход с вторыми входами соответств тощих элементов И второй и третьей групп предпоследнего разряда.

COOS СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1182674 (з1)4 Н 03 И 1/38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,; "

К ABTOPGHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3733104/18-24 (22) 21.04.84 (46) 30.09.85. Бюл. Р 36 (72) Л.А. Надирадзе, Т.N, Хиникадзе и В.Н. Голубничий (71) Научно-исследовательский институт автоматизации производственных процессов в промьппленности (53) 681.325(088,8) (56) Авторское свидетельство СССР

У 451190, кл. Н 03 К 13/17, 1974.

Авторское свидетельство СССР У 1014139, кл. Н 03 К 13/17, 1980. (54)(57) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий регистр, прямые выходы триггеров которого через цифроаналоговый преобразователь соединены с первым входом компаратора, второй вход которого соединен с шиной преобразуемого сигнала, первую группу элементов И, выходы которых соединены с входами обнуления соответствующих триггеров регистра, а первые входы — с выходами соответствующих элементов И второй группы, первые входы которых подключены к прямым выходам соответствующих триггеров регистра, кроме триггера младшего разряда, вторые входы — к выходам соответствукщих элементов И третьей группы, первые входы которых соединены с инверсными выходами соответствукицих триггеров, кроме триггеров старшего и младшего разрядов, вторые входы — с выходами соответствующих элементов И третьей группы предыдущих разрядов, дополнительные входы обнуления триггеров регистра, кроме триггера старшего разряда, а также вход установки триггера старшего разряда и вход обнуления триггера управления объединены и подключены к шине запуска, прямой выход триггера управления соединен с шиной

"Готовность к преобразованию", инверсный выход — с входом ждущего генератора, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия, в него введены элементы И четвертой группы и дополнительный элемент И, первый вход которого соединен с выходом компаратора, второй вход объединен с первыми входами элементов И четвертой группы и подключен к выходу ждущего генератора, вторые входы элементов И четвертой группы соединены с выходами соответствующих элементов И второй группы предыдущих разрядов, а выходы — с входами установки соответствующих триггеров .регистра, кроме триггера старшего

;разряда, и триггера управления, причем выход дополнительного элемента И подключен к вторым входам элементов И первой группы, а прямой выход триггера младшего разряда регистра соединен с первым входом соответствующего элемента И первой и вторым входом соответствующего элемента И второй групп, а инверсный выход— с вторыми входами соответствующих элементов И второй и третьей групп предпоследнего разряда.

1182674

Изобретение относится к технике аналого-цифрового преобразования и может быть использовано при передаче аналоговых сигналов по дискретным каналам связи. 5

Целью изобретения является повышение быстродействия.

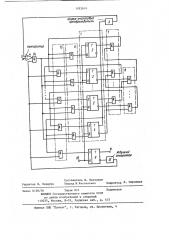

На чертеже приведена функциональная схема устройства, Аналого-цифровой преобразователь 10 содержит регистр 1, прямые выходы триггеров 2 которого через цифроаналоговый преобразователь (ПДП) 3 соединены с первым входом компаратора 4, второй вход которого соединен с ши- 15 ной 5 преобразуемого сигнала, первую группу 6 элементов И, вторую группу 7 элементов И, третью группу 8 элементов И, триггер 9 управления, вход 10 обнуления которого и вход установки 2Î триггера 2 старшего разряда объединены и подключены к шине 11 "Готовность к преобразованию", ждущий генератор

12, четвертую группу 13 элементов И, дополнительный 14 элемент И, 25

Аналого-цифровой преобразователь работает следующим образом.

Перед каждым преобразованием аналогового сигнала на шине 5 входного сигнала подается импульс запуска на шине 10 запуска, которым в регистре 1 установится двоичный код 100 ... 00.

На выходе ЦАП 3 появится соответствующий этому коцу аналоговый сигнал, 1 равный — U где U — верхний предел 35 диапазона входного аналогового сигнала. Этот сигнал сравнивается с аналоговым сигналом U „в компараторе 4 рк

9 на выходе которого установится сигнал логического нуля, PcJIH U 6 7 2 U ю

&х или сигнал логической единицы в противном случае.

Импульс запуска перебрасывает триггер 9 в нулевое положение, в связи с чем ждущий генератор 12 начинает генерацию прямоугольных импульсов.

Первым импульсом от ждущего генератора 12 в регистре 1 установится двоичный код а„„ 10 ... 00, где ап .1— двоичная цифра первого (старшего) разряда цифрового кода входного сигнала.

До появления второго импульса от ждущего генератора 12 на выходе ЦАП

3 появится соответствующий коду

a„- 10 ... 00 сигнал (— 2 а„„+ — 4) U

1 1 в соответствии с которым установится аналогично на выходе компаратора 4 сигнал логического нуля или единицы.

Поэтому вторым импульсом в регистре

1 установится код а„„а „10 ... 00.

Аналогично, предпоследним (n-1)-м импульсом в регистре 1 установится код а,,, а „ .. ° a„ 1, а последним и-м импульсом — код а „,, а „, ... а„а„.

Последним импульсом в триггере 9 установится также состояние логической единицы и поэтому прекратится выцача импульсов от ждущего генератора 12 и появится сигнал логической единицы на шине 11 "Готовность к преобразованию".

1182674

Составитель В. Махнанов

Техред Ж. Кастелевич

Корректор Е. СиРохман

Редактор N. Бандура

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 6120/56 Тираж 871

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5