Устройство для сопряжения разноскоростных вычислительных устройств

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ РАЗНОСКОРОСТНЫХ ВЫЧИСЛИТЕЛЬНЫХ УСТРОЙСТВ , содержащее первый триггер, первый и второй элементы задержки, блок памяти, реверсивный счетчик, дешифратор нуля, счетчики записи и считывания, две группы элементов И, группу элементов ИЛИ, выходы которых соединены с адресным входом блока памяти, а первые и вторые входы элементов ИЛИ группы соединены соответственно с выходами элементов И первой и второй групп, первые входы элементов И первой группы соединены с выходами соответствующих разрядов счетчика записи, вторые входы элементов И первой группы объединены между собой и соединены с входом первого элемента задержки, счетным входом счетчика записи и суммирующим входом реверсивного счетчика, вычитающий вход которого соединен со счетным входом счетчика считывания, с входом второго элемента задержки и с первыми входами элементов И второй группы, выход реверсивного счетчика соединен с входом дешифратора нуля, а вход считывания устройства соединен с первым входом первого триггера, выходы первого и второго элементов задержки соединены соответственно с входами записи и считывания блока памяти, выход которого является информационным выходом устройства, выход счетчика считывания подключен к вторым входам элементов И второй группы, отличающееся тем, что, с целью расширения области применения, в устройство введены регистр, второй и третий триггеры, два элемента НЕ, третий и четвертый элементы.задержки и элемент И, первый и второй входы которого соединены соответственно с выходом дешифратора нуля и выСП ходом первого триггера, второй вход которого подключен к выходу третьего элемента задержки, вход которого соединен с выходом второго зле- .. мента задержки, а вход записи устройства соединен с первым входом второго триггера и с входом стробирования ре00 Од гистра, информационный вход которого является информационным входом СО устройства, а выход регистра подклю J чен к информационному входу блока паСП мяти, выход элемента И подключен к первому входу третьего триггера,второй вход которого соединен с выходом второго триггера, а первый и второй выходы третьего триггера соединены соответственно с в-ходами первого и второго элементов НЕ, выходы которых подключены к входам второго и первого элементов задержки,выход первого элемента задержки соединен с входом четвертого элемента задержки,вьсход которого соединен с вторым входом второго триггера.

ÄÄSUÄÄ 1183975

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А (51) 4

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЪ|ТИЙ

ОПИСАНИЕ ИЗОБРЕ

Н ABYOPGHOMY СВИДЕТЕЛЬСТВУ вого триггера, выходы первого и второго. элементов задержки соединены соответственно с входами записи и считывания блока памяти, выход которого является информационным выхо.дом устройства, выход счетчика считывания подключен к вторым входам элементов И второй группы, о т л ич а ю щ е е с я тем, что, с целью расширения области применения, в устройство введены регистр, второй и третий триггеры, два элемента НЕ, третий и четвертый элементы задержки и элемент И, первый и второй входы которого соединены соответственно с выходом дешифратора нуля и выходом первого триггера, второй вход которого подключен к выходу третьего элемента задержки, вход которого соединен с выходом второго эле- .. мента задержки, а вход записи устройства соединен с первым входом второго триггера и с входом стробирования регистра, информационный вход которого является информационным входом устройства, а выход регистра подключен к информационному входу блока паподключены к входам второго и первого элементов задержки, выход первого элемента задержки соединен с входом четвертого элемента задержки, выход которого соединен с вторым входом второго триггера. (21) 3732608/24-24 (22) 27.04.84., (46) 07.10.85. Бюл. к- 37 (72) С.Ф. Иванов (71) .Куйбышевский институт инженеров железнодорожного транспорта (53) 681.3(088.8) (56) Авторское свидетельство СССР

В 989555, кл. G 06 F 3/04, 1982.

Авторское свидетельство СССР

Ф 752321, кл. С 06 F 3/04, 1979. (54)(57) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

РАЗНОСКОРОСТНЫХ ВЫЧИСЛИТЕЛЬНЫХ УСТРОЙСТВ, содержащее первый триггер, первый и второй элементы задержки, блок памяти, реверсивный счетчик, . дешифратор нуля, счетчики записи и считывания, две группы элементов И, группу элементов ИЛИ, выходы которых соединены с адресным входом блока памяти, а первые и вторые входы элементов ИЛИ группы соединены соответственно с.выходами элементов И первой и второй групп, первые входы элементов И первой группы соединены с выходами соответствующих разрядов счетчика записи, вторые входы элементов И первой группы объединены между собой и соединены с входом первого элемента задержки, счетным входом счетчика записи и суммирующим входом реверсивного счетчика, вычитающий вход которого соединен со счетным входом счетчика считывания, с входом второго элемента задержки и с первыми входами элементов И второй группы, выход реверсивного счетчика соединен с входом дешифратора нуля, а вход считывания устройства соединен с первым входом пермяти, выход элемента И подключен к, первому входу третьего триггера,второй вход которого соединен с выходом второго триггера, а первый и второй выходы третьего триггера соединены соответственно с входами первого и второго элементов НЕ, выходы которых

1183975

Изобретение относится к вычислительной и информационно-измерительной технике и может найти применение для организации обмена информацией между устройствами, работающими с разной скоростью.

Целью изобретения является расширение области применения устрой: ства .

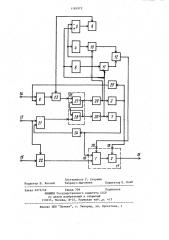

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит элементы 1 памяти группы, элементы И 2 группы, второй элемент 3 задержки, счетчик

4 считывания, реверсивный.счетчик

О

5, первый триггер 6, первый элемент

7 задержки, счетчик 8 записи, дешифратор 9 нуля, элементы 10 И второй группы, элементы И 11 первой группы, элементы ИЛИ 12 группы, управляющие входы 13 записи и входы 14 считывания устроства, информационные входы

15 и выходы 16 устройства, блок 17 памяти с первым 18, вторым 19 управляющими и адресным 20 входами, вто25 рой триггер 21, регистр 22, элемент

И 23, четвертый 24 и третий 25 элементы задержки, третий триггер 26, выполненный на элементах 27 и 28

И-HE первый 29 и второй 30 элементы НЕ.

Устройство работает следующим образомм.

В исходном состоянии счетчики 8 и 4, реверсивный счетчик 5, триг- 35 геры 6 и 21 обнулены, на адресном входе 20 блока 17 памяти находится потенциал, соответствующий "0"1на выходе дешифратора 9 находится запирающий потенциал. 40

При поступлении на вход 15 параллельного кода на .вход 13 приходит сигнал, который заносит код со входа 15 в регистр 22 и устанавливает триггер 21 в единичное состояние, 45 означающее запрос на запись информации в блок 17 памяти устройства.

Запрос на запись высоким потенциалом поступает на второй вход триггера

26, и если к этому моменту на пер- 50 вом входе данного триггера отсутствует запрос на считывание, то на его втором выходе устанавливается низкий потенциал, а на выходе элемента 30 HE — сигнал записи, 55 по которому информация переписывается иэ регистра 22 в блок 17 памяти по нулевому адресу. Код адреса, по которому происходит запись, подается на вход 20 блока

17 памяти с выхода счетчика 8 через элементы И 11. Длительность сигнала записи на входе 19 блока 17 определяется элементом 24 задержки. По сбросу сигнала записи запись кода в блок 17 памяти завершается, содержимое счетчика 8 и реверсивного счетчика 5 увеличивается на единицу. На этом завершается цикл обслуживания запроса записи.

При поступлении следующего кода на вход 15 и сигнала íà вход 13 цикл обслуживания запроса записи повторяется.

При подаче на вход l4 сигнала считывания триггер 6 устанавливается в единичное состояние, означающее запрос на считывание информации иэ блока 17 памяти устройства. Запрос на считывание при наличии на первом входе элемента 23 И разрешающего потенциала с выхода дешифратора 9 нуля поступает через этот элемент

И на первый вход триггера 26, и если к этому моменту на втором входе данного триггера отсутствует запрос на запись, то на его первом выходе устанавливается низкий потенциал, а на выходе элемента 39 НЕ— сигнал считывания. Этот сигнал с задержкой, обеспечиваемой элементом

3 задержки, поступает на вход 18 блока 17 памяти, разрешая считывание информации и выдачу кода на выход 16 данного блока. Причем код первого адреса (нулевой), по которому происходит считывание, подается с выхода счетчика 4 через элементы

10 И группы. Длительность сигнала считывания на входе 18 блока 17 определяется элементом 25 задержки.

По сбросу сигнала считывания считывание из блока памяти завершается, содержимое счетчика 4 увеличивается, а реверсивного счетчика 5.уменьшается на единицу. На этом завершается цикл обслуживания запроса считывания. При поступлении на вход 14 устройства следующего считывающего сигнала цикл обслуживания запроса считывания повторяется.

При считывании всей информации из блока памяти содержимое реверсивного счетчика становится равным нулю, вследствие чего дешифратор

9 нуля формирует сигнал, блокирующий

11839

° элемент 23 И. Поступивший после этого в устройство запрос на считывание не обслуживается, но хранится в триггере 6.

После записи хотя бы одного кода блокировка снимается и разрешается обслуживание поступившего ранее запроса на считывание.

Если сигнал считывания на вход 14 устройства приходит во время обслужи- !О вания запроса записи, сигнал запроса считывания блокируется до окончания обслуживания запроса записи,,т.е. до сброса триггера 21. После сброса триггера 21 начинается цикл обслужи- 15 вания запроса считывания. Аналогично, если сигнал записи на вход 13 устройства поступает во время обслуживания запроса считывания, то обслуживание запроса записи начнется после,О окончания обслуживания запроса считывания, т.е. после сброса триггера 6.

При одновременном поступлении сигналов записи и считывания триггер 26 устанавливается в одно из двух сос- 25 тояний. Пусть, например, это будет состояние, когда на выходе элемента

28 И-НЕ устанавливается потенциал

75 4 логического нуля, выдаваемый с выхода элемента 30 НЕ как потенциал обслуживания запроса записи. По окончании цикла обслуживания запроса записи триггер 21 будет установлен в нулевое состояние, разрешая тем самым выполне- ние цикла обслуживания запроса считывания. По концу цикла обслуживания запроса считывания триггер 6 также устанавливается в нулевое состояние.

На этом процедура обслуживания одновременно поступивших в устройство запросов на запись и считывание информации завершается.

Таким образом, предлагаемое устройство осуществляет прием и выдачу информации без искажений при любом временном расположении друг относительно друга сигналов записи и считывания на входе устройства, в том числе и при их совпадении. Нормальная работа устройства не нарушается и при попытке считывания из устройства, когда информация в нем отсутствует.Тем самым повышается функциональная надежность устройства для сопряжения при незначительном усложнении кокс прукции.

1 l83975

Составитель Г. Стернин

Техред С Лигунова Корректор Т. Колб

Редактор П. Коссей

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 6272/49 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб.,д. 4/5