Устройство для оперативного контроля в системах автоматизированного управления

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ ОПЕРАТИВНОГО КОНТРОЛЯ В CHCTEbiAX АВТОМАТИЗМ- РОВАННОГО УПРАВЛЕНИЯ, содержащее регистр , блок ввода информации, первые выходы которого соединены с первыми входами блока управления,-подключенного первыми выходами к блоку памяти , вторым вьпсодом - к первому входу блока индикации, отличающееся тем, что, с целью упрощения и повышения быстродействия устройства, в него введены два элемента ИЛИ, элемент ЗАПРЕТ, сумматор и счетчик.адреса , первые входы которого соединены с третьими выходами блока управления, второй вход - с вторым выходом блока ввода информации, а выход - с вторьм входом блока памяти и через первый элемент ИЛИ - с вторым входом блока индикации,- третий выход блока ввода информации подключен к третьему входу блока памяти и через второй элемент ИЛИ - к входу регистра, выход которого соединен с первым входом сумма (Л тора, подключенного вторым входом к выходу блока памяти, первым выходом к второму входу блока управления, а вторым выходом - к второму входу первого элемента ИПИ и через элемент ЗАПРЕТ - к второму входу второго элемента ИЛИ. 00 О9 СО 00 о

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А (st)4 С 06 F 15/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPCHOMY СВИДЕТЕЛЬСТВУ г©СУДАРСТВЕКНЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКР61ТИЙ (21) 3749640/24-24 (22) 06.04.84 (46) 07.10.85. Бюл. В 37 (72) И.И. 1!орев, В.С. Воробьев, В.И. Брусиловский, A.Ï..Äóä÷åíêî и Д.Л ° Ошерович (71) Новосибирский филиал Всесоюзного научно-исследовательского института транспортного строительства и Автобаза -Треста "Мостострой-10" (53) 621.503.55(088.8) (56) Авторское свидетельство СССР

У 431517, кл. С 06 F 15/46, 1974.

Авторское свидетельство СССР

Ф 399870, кл. С 06 F 15/46, 1974. (54)(57) 1. УСТРОЙСТВО ДЛЯ ОПЕРАТИВНОГО КОНТРОЛЯ В СИСТЕМАХ АВТОМАТИЗИРОВАННОГО УПРАВЛЕНИЯ, содержащее регистр, блок ввода информации, первые выходы которого соединены с первыми входами блока управления,.подключенного первыми выходами к блоку памяти, вторым выходом — к первому входу

„„Я0„„1183986 блока индикации, о т л и ч а ю щ ее с я тем,.что, с целью упрощения и повышения быстродействия. устройства, в него введены два элемента ИЛИ, элемент ЗАПРЕТ, сумматор и счетчик. адреса, первые входы которого соединены с третьими выходами блока управления, второй вход — с вторым выходом блока ввода информации, а выход — с вторым входом блока памяти и через первый элемент ИЛИ вЂ” с вторым входом блока индикации, третий выход блока ввода информации подключен к третьему входу блока памяти и через второй элемент

ИЛИ вЂ” к входу регистра, выход которого соединен с первым входом сумматора, подключенного вторым входом к выходу блока памяти, первым выходом— к второму входу блока управления, а вторым выходом — к второму входу первого элемента ИЛИ и через элемент

ЗАПРЕТ вЂ” к второму входу второго элемента ИЛИ.

1183986

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок управления содержит первый и второй счетчики импульсов, два триггера, последовательно соединенные генератор импульсов, первый элемент И, первый элемент ИЛИ, первый элемент задержки, второй элемент И и второй элемент ИЛИ, а также последовательно соединенные третий элемент ИЛИ, первый триггер, третий элемент И, четвертый элемент ИЛИ, второй элемент задержки и четвертый элемент И, выход которого соединен с третьим выходом блока управления и через первый счетчик импульсов — с . вторым входом второго элемента ИЛИ, выход которого подключен к выходу блока управления и через второй „ счетчик импульсов — к первому входу второго триггера и к первому входу третьего элемента ИЛИ, вторым входом

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства контроля технологических или производственных процессов, состояния оборудования, оперативного контроля в системе управления, в сфере управления транспортными перевозками, для управления ходом работ по сетевым графикам, а также для отображения преобразова- 10 ния информации задач оптимального планирования.

Цель изобретения — упрощение устройства и повышение его быстродействия. 15

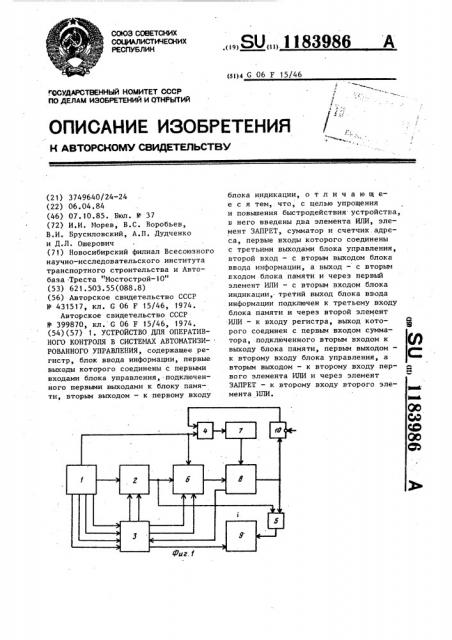

На фиг. 1 представлена функциональная схема устройства; на фиг.2— схема блока управления; на фиг. 3— блок ввода информации. Устройство содержит блок 1 ввода информации, 2п счетчик 2 адреса, блок 3 управления, элементы ИЛИ 4 и 5, блок 6 памяти, регистр 7, сумматор 8, блок 9 индика ции, элемент 10 запрета.

Блок управления (фиг. 2) содержит д счетчики 11 и 12 импульсов, элементы

ИЛИ 13-16, элементы И 17-20, триггеры 21-23, элементы задержки 24 и подключенного к соответствующему первому входу блока управления, выход второго триггера подключен к второму входу первого элемента И, а второй вход — к входу блока управления, первый выход третьего триггера соединен с вторым входом второго элемента И, а второй выход — с вторым входом четвертого элемента И, а вход — с соответствующим первым входом блока управления, третий вход второго элемента ИЛИ соединен с соответствующим первым входом блока управления, вторые входы первого и четвертого элементов ИЛИ подключены к соответствующим первым выходам блока управления, а также к выходам третьего и первого элементов И соответственно, второй выход первого триггера подключен к второму выходу блока управления.

25, генератор 26 импульсов, а также входы 27-31 и выходы 32-36.

Блок ввода информации 1 (фиг. 3) содержит фотосчитывающий блок 37, регистр 38 для кратковременного хра-. нения адреса, элементы И 39, И 40, ИЛИ 41, ИЛИ 42, пульт 43 управления, формирователь 44 сигнала.

Назначение кнопок следующее: с — кнопка выбора режима прямой или транспонированной матрицы, 5 — набор кно-. пок установки начального адреса, в кнопка записи начального адреса; кнопка включения режима "Запись в ЗУ";

3 — кнопка включения режима "Чтение

ЗУ".

Чтение информации из фотосчитывающего блока 37 синхронизируется сигналами тактового генератора. Элементы

И 39, И 40 обеспечивают передачу считываемой информации в направлении одного из выходов, в зависимости от заданного режима.

Все указанные блоки и элементы реализованы на основе типовых. Например, в качестве запоминающего устройства, счетчиков, регистра, сумматора, триггеров, элементов И, ИЛИ могут

1183986 использоваться интегральные микросхемы К565РУ2, К155НЕ7, К155ИЕ5,К155ИР1, К155ИХЗ, К155ТИ2, К155ЛАЗ, К155ЛЕ1 и др, В устройстве может быть использован блок индикации ИМГ-1-03. Блок 5 ввода содержит пульт для ручного ввода информации, а также фотосчитывающее устройство FS-1501.

Устройство работает следующим образом.

В режиме записи показателей С;.

1) на адресные входы блока 6 памяти поступают адреса ячеек, формируемые счетчиком 2 адреса. Адресная информация поступает на вход счетчика 2 адреса из блока 1 ввода и записывается в счетчик адреса по сигналу, поступающему с выхода 32 блока управления. Этот сигнал формируется в блоке ввода, поступает на вход счетчика адреса через элемент ИЛИ 13 блока управления. Информация С" поступа1) ет из блока ввода на информационный вход блока 6 памяти в такт с сигналом записи, возникающим на выходе 34 блока управления.

Если показатели должны быть представлены в виде прямой матрицы, то сначала в счетчик адреса записывается адрес первой страницы блока, а 30 затем поочередно формируются адреса всех ячеек этой страницы добавлением в счетчик адреса единицы. При. работе с прямой матрицей триггер 21 блока управления находитсяв нулевомсостоянии, поэтому элемент И 17 закрыт, а элемент И 18 открыт. Сигнал записи с выхода блока ввода поступает на вход 29 блока управления, устанавливает триггер 22 этого блока в еди- 40 ничное состояние и открывает элемент

И 19. Тактовые импульсы поступают с выхода 34 блока управления на вход записи блока 6 и одновременно через элементы ИЛИ 15, задержки 25, И 18 45 поступают на вход прибавления единицы счетчика адреса и вход счетчика

12. Каждый тактовый импульс записывает показатель С" в выбранную ячей1) ку блока 6 памяти и формирует адрес 50 следующей ячейки, т.е. добавляет единицу в счетчик адреса.. Заполнение счетчика 12 происходит одновременно с перебором всех ячеек указанной страницы. При заполнении счет- 55 чика 12 сигнал с его выхода через элемент ИЛИ 13 записывает в счетчик адреса следующей страницы и добавляет единицу в счетчик 11. После этого счетчик 12 обнуляется (цепь обнуления не показана). Информация записывается в ячейки следующей страницы аналогично. При заполнении всех страниц блока памяти 6 счетчик 11 также заполняется и подает сигнал, который переключает триггер 22 в нулевое состояние ° Запись информации окончена.

При занесении информации с одновременным транспортированием матрицы показателей вначале записывается адрес первой страницы блока. памяти в счетчик адреса. Информация записывается в ячейку блока памяти, соответствующую этому адресу. Затем номера страниц поочередно переключаются. Для записи информации с транспортированием матрицы триггер 21 переключается в единичное положение сигналом с выхода блока ввода. Элемент И 17 открывается, а И 18 закрывается ° Сигналом с выхода блока ввода триггер 22 переключается в единичное положение и открывает элемент И 19. Тактовые импульсы поступают на вход записи блока 6 памяти и через элементы ИЛИ

14, задержки 24,И17, ИЛИ 13,поступают на вход записи счетчика адреса и вход счетчика 11. Каждый тактовый импульс записывает информацию в первую ячейку выбранной страницы блока 5 памяти и записывает адрес следующей страницы в счетчик адреса.

Заполнение счетчика 11 происходит одновременно с перебором всех стра» ниц блока 6 памяти, поэтому после записи информации в ячейку последней страницы ЗУ на выходе этого счетчика появляется сигнал, который переключает триггер 22 в нулевое состояние.

Заполненная таким образом матрица показателей будет транспонированной по отношению к исходной.

В режиме поиска адреса по показателю С . триггер 23 сигналом с вы \) хода блока ввода переключается в еди ничное состояние. Элемент И 20 открывается и тактовые импульсы поступают с выхода 35 блока управления на вход чтения блока памяти и одновременно поступают на вход прибавления единицы или вход записи адреса страницы в зависимости от положения триггера

21. Считываемая информация поступает на вход первого слагаемого сумматора

8. На вход второго слагаемого этого сумматора поступает обратный код

1183986 сравниваемого показателя С;, предварительно эачисанного в регистр 7 иэ блока ввода через элемент ИЛИ 4.

Суммматор в этом случае работает как схема сравнения, что обеспечивается подачей сигнала на управляющий вход элемента 10 запрета и на вход переноса нулевого разряда сумматора (не показано). При совпадении считанного иэ 10 блока памяти показателя с показателем, записанным в регистре 7, на выходе переноса последнего разряда сумматора появляется единичный сигнал, который поступает на вход 31 блока управления 15 и через элемент ИЛИ 16 переключает триггер 23 в нулевое состояние. Эле-.. мент И 20 закрывается, запрещая прохождение тактовых импульсов. Адрес ячейки ЗУ, из которой была считана ин-20 формация в последнем такте, выводится в блок индикации. При этом элементы

24 и 25 обеспечивают задержку записи нового адреса в счетчик адреса до окончания процесса записи или чтения 25 блока памяти и передачи информации в блок индикации.

Если необходимо просуммировать показатели С.. по строкам или столб 5 цам матрицы, т.е. по одноименным ячеи30 кам всех страниц или всем ячейкам одной страницы, то адресная информация формируется аналогично построению транспонированной или прямой матрицы соответственно с подачей импульсов чтения блока памяти синхронно с изменением адресов. Информация, считываемая из блока памяти, поступает на вход сумматора, который работает в этом случае как накапливаю- 40 щий. Это обеспечивается снятием сигнала с управляющего входа элемента 10 запрета и входа переноса нулевого разряда сумматора. В процессе сумми рования информация накапливается в регистре 7 (цепь записи в регистр также не показана).

После чтения всех адресов триггер

23 обнуляется сигналом из счетчика

11 и информация выводится из сумматора в-блок индикации.

При решении задач сортировки данных, требующих осуществлять выборочную запись и чтение информации в блоке памяти, данное устройство позволяет получить выигрыш во времени по сравнению с известным. Это возможно благодаря адресному обращению к нужной странице ЗУ, организованному с помощью счетчика адреса.

В известном устройстве обращение ко всем строкам и столбцам матрицы блока памяти осуществляется лишь последовательно с помощью регистров сдвига, что исключает возможность выборочного обращения к нужной строке или столбцу.

Блок ввода выполняет стандартные функции и не требует подробного описания. В простейшем случае он содержит клавиатуры набора информации и набора адреса, кнопки записи адреса в счетчик адреса и записи информации в блок памяти, кнопки чтения блока памяти, установка режима записи показателей в виде прямой или транспортированной матрицы. В режимах поиска адреса и суммирования показателей выдача адресной информации из блока ввода в счетчик адреса тактируется. генератором тактовых импульсов (не показано).! 183986

Фиг.2

1 l 83986

Составитель И. живец

Техред С.Мигунова

Корректор О. Луговая

Редактор П. Коссей

Тираж 709

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

133035, Москва, И-35, Раушская наб., д. 4/5

° В.

Заказ 6272/49

Подписное

Филиал KIII "Патент", г. Ужгород, ул. Проектная, 4