Квадратичный аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

1. КВАДРАТИЧНЫЙ АНАЛОГОЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий сумматор, квантователь на компараторах, источник опорного напряжения , отличающийся тем, что, с целью повьпиения надежности и точности преобразования, в него введены аналоговый сумматор, преобразователь кода, генератор равномерно распределенного напряжения , генератор стабильной частоты, делитель частоты, вход которого объединен с первыми входами сумматора , преобразователя кода компараторов квантователя и соединен с выходом генератора стабильной частоты , а выход делителя частоты соединен с входом генератора равномерно распределенного напряжения, при этом первый вход аналогового сумматора является входной шиной, второй вход соединен с выходом генератора равномерно распределенного напряжения , а выход - с вторыми входами компараторов квантователя, выходы которых соединены с соответствующими вторы -1и входами преобразователя кода, выходы которого соединены с соответствующими вторыми входами сумматора, выход которого является выходной шиной, причем третьи входы компараторов соединены с соответствующими выходами источника опорного напряжения. 2. Преобразователь по п. 1, о т личающийся тем, что прес образователь кода выполнен на логи@ ческом блоке вьзделения приоритета, (Л программируемом постоянном запоминающем устройстве, счетчике, ключе, первый вход которого является первым входом преобразователя кода, второй вход ключа соединен с первым выходом логического блока вьщеления приоритета, а выход - с первым вхо00 дом счетчика, вторые входы которого ul объединены с соответствующими входами программируемого постоянного запоминающего устройства и соединены с соответствующими вторыми выходами . логического блока вьщеления приоритета , входы которого являются соответствующими вторыми входами преобразователя кода, при этом выходы прог .раммируемого постоянного запоминающего устройства и счетчика являются соответствующими выходами преобразователя кода.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

{я)4 Н 03 К 13/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3705492/24-24 (22) 28.02.84 (46) 07,10.85. Бюл. У 37 (72) О.А.Голышевский, В.А.Юрманов, В.Д.Иихотин и В.И. Шляндин (71) Пензенский политехнический институт (53) 681.325(088.8) (56} Смеляков В.В. Цифровая измерительная аппаратура частот. М.:

Энергия, 1975, с. 74-75.

Авторское свидетельство СССР

Ф 1002974, кл. G 01 R 19/22, 1981. (54)(57) 1 ° КВАДРАТИЧНЫЙ АНАЛОГОЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий сумматор, квантователь на компараторах, источник опорного напряжения, отличающийся тем, что, с целью повышения надежности и точности преобразования, в него введены аналоговый сумматор, преобразователь кода, генератор равномерно распределенного напряжения, генератор стабильной частоты, делитель частоты, вход которого объединен с первыми входами сумма.тора, преобразователя кода компараторов квантователя и соединен с выходом генератора стабильной частоты, а выход делителя частоты соедиS нен с входом генератора равномерно распределенного напряжения, при этом первый вход аналогового сумматора является входной шиной, второй вход соединен с выходом генератора равномерно распределенного напряже-.

„„SU„„1 40 3 ния, а выход — с вторыми входами компараторов квантователя, выходы которых соединены с соответствующими вторыми входами преобразователя кода, выходы которого соединены с соответствующими вторыми входами сумматора, выход которого является выходной шиной, причем третьи входы компараторов соединены с соответствующими выходами источника опорного напряжения.

2. Преобразователь по п. 1, о т л и ч а ю шийся тем, что преобразователь кода выполнен на логическом блоке выделения приоритета, программируемом постоянном запоминающем устройстве, счетчике, ключе, первый вход которого является первым входом преобразователя кода, второй вход ключа соединен с первым выходом логического блока вьделения приоритета, а выход — с первым входом счетчика, вторые входы которого объединены с соответствующими входами программируемого постоянного запоминающего устройства и соединены с соответствующими вторыми выходами ,логического блока выделения приоритета, входы которого являются соответствующими вторыми входами преобразователя кода, при этом выходы прог.раммируемого постоянного запоминающего устройства и счетчика являются соответствующими выходами преобразователя кода.

1 1184083

Изобретение относится к электроизмерительной технике и может быть использовано для определения квадрата мгновенного значения переменно. го напряжения в широком частотном диапазоне.

Целью изобретения является повышение надежности и точности преобразования.

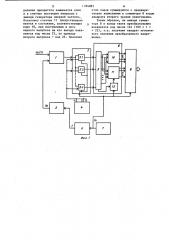

На фиг. 1 представлена структур- 10 ная схема предлагаемого квадратичного преобразователя, на фиг. 2— временные диаграммы, поясняющие

его работу.

Квадратичный преобразователь со- 15 держит аналоговый сумматор 1, генератор 2 равномерно распределенного напряжения, квантователь 3, состоящий из и компараторов, источник 4 опорного иапряжения, делитель 5 часто-20 ты, преобразователь 6 кода, генератор 7 стабильной частоты, сумматор 8.

Преобразователь 6 кода выполнен на логическом блоке 9 выделения приоритета> программируемого постоянно- 25 го запоминающего устройства (ППЗУ)

10, счетчика 11 и ключа 12.

Принцип работы преобразователя заключается в следующем.

При этом мгновенное значение входного сигнала в первом такте преобразования, определяется выражением

П 1 = 1 „, 1 во втором такте

Преобразователь кода 6 работает следующим образом.

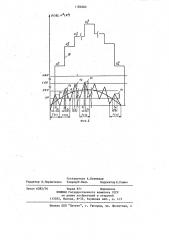

Размер преобразуемого напряжения

U „(t) для момента времени Т, (фиг. 2) равен Ц„(Т,), т.е. срабатывают два нижних по схеме компара-. тора. Логический блок 9 выделения приоритета выделяет сигнал с выхода старшего из сработавших компараторов квантователя. Размер напряжения, соответствующего второму уровню квантования, идентифицируется двоичным кодом числа 10, т.е. это соответствует поступлению в счетчик 11 десяти импульсов опорной частоты.

Из ППЗУ 10 в сумматор 8 переносится код квадрата числа 10. Сигналом с выхода логического блока 9 выделения приоритета счетчик 11 предустанавливается в состояние, соответствующее второму уровню квантования (т.е. числу 10). Счетчик организован таким образом, что последовательности натуральных чисел на его входе однозначно соответствует на его выходе последовательность чисел, взятых по нечетному ряду, т.е. при поступлении на вход счетчика первого импульса на его выходе появляется код числа 1, по приходу второго импульса — на выходе появляется код,числа 3, поступлению третьего импульса соответствует код числа 5, ..., приходу десятого импульса — код 19, одиннадцатого импульса — код 21, двенадцатого импульса — код 23 и т.д. Одновременно сигналом с второго выхода логического блока 9 выЬ (t) + Uðj7j U.30

Кривая с (фиг. 2), характеризующая изменение входного напряжения

U)((t) за полуперпод Тх/2 суммируется с выходным напряжением Uр(t) генератора равномерно распределепного напряжения 2. Характер изменения напряжения Up может носить как детерминированный, так и случайный характер. Примером детерминированного сигнала может служить сигнал треугольной

40 формы. При случайном характере Up таким сигналом может служить сигйал, имеющий равномерный закон распределения и конечное число градаций в пределах шага квантования или белый шум.

Полученная сумма входного и равномерно распределенного напряжения (кривая Б, фиг. 2) поступает на первые Tl входы компараторов квантователя 1. На вторые и входы поступает

50 опорное напряжение U состоящее из суммы ряда постоянных уровней U,, взятых с равномерным шагом ДБ.

Квантователь 3 выделяет интервалы времени t„, в течение которых выпол55 няется неравенство

UЪ U1, + kt дЦ + kt э

Ъ2 где k — коэффициент пропорциональности.

Таким образом, мгновенное значе» ние U входного сигнала в i момент времени равно

U» = (m 1) DU+ kt где m — - порядковый номер сработавшего компаратора.

В ППЗУ хранятся коды, соответствующие квадратам значений уровней квантования квантователя 3. Э

1184083 деления приоритета замыкается ключ и в счетчик поступают импульсы с выхода генератора опорной частоты.

Поскольку счетчик 11 предустанавливается в состояние, соответствующее коду 10, при поступлении в него первого импульса на его выходе появляется код числа 21, по приходу второго импульса - код 23. Значения этих кодов суммируются с предварительно записанным в сумматоре 8 кодом квадрата второго уровня квантования.

Таким образом, на выходе сумматора 8 к концу такта преобразования появляется код числа 144 (100 + 1 +

+ 23), т.е. получают квадрат мгновенного значения преобразуемого напряжения.

1184083 осв1, uÀ.вЧ

ndV

idU

gdV

Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 6282/54

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Составитель А.Кузнецов

Редактор О.Черниченко Техред М,Надь Корректор Е.Рошко