Устройство фазовой автоподстройки

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ , содержащее блок фазирования и выходной триггер, отличающееся тем, что, с целью получения выходного сигнала, среднего по фазе между двумя опорными сигналами, в него введены блок приоритета , первый и второй инверторы, входы которых подключены к первому и второму выходам блока приоритета соответственно, и дополнительный блок фазирования, каждый блок фазирования выполнен в виде последовательно соединенных первого и второго элементов задержки, фазового детектора и интегратбра, выход которого подключен к управляющим входам первого и второго элементов задержки, при этом выход первого элемента задержки каждого блока фазирования подключен к соответствующе . му входу выходного триггера, первый и второй выходы блока приоритета подключены к первому элементу задержки и другому входу фазового детектора блока фазирования соотQ ф ветственно, а выходы первого и второго инверторов подключены к входу (О первого элемента задержки и другому входу фазового детектора дополнительного блока фазирования соответственно , при этом входы блока приоритета являются входами первого и второго опорных сигналов.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧ ЕСНИХ

РЕСПУБЛИК () 9) (I )) (51)4 ц 03 1. 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPGHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЪПИЙ (21) 3612228/24-09 (22) 27.06.83 (46) 15.10.85. Бюл. )) 38 (72) О.Ф. Бузин и В.А. Чулков (53) 621.396.666 (088.8) (56) Авторское свидетельство СССР

У 855931, кл. H 03 L 7/00, 1975.

Авторское свидетельство СССР

У 327 62, кл. H 03 L 7/00, 1970. (54) (57) УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ, содержащее блок фазирования и выходной триггер, о т л и— ч а ю щ е е с я тем, что, с целью получения выходного сигнала, сред- него по фазе между двумя опорными сигналами, в него введены блок приоритета, первый и второй инверторы, входы которых подключены к первому и второму выходам блока приоритета соответственно, и дополнительный блок фазирования, каждый блок фазирования выполнен в виде последовательно соединенных первого и второго элементов задержки, фазового детектора и интегратора, выход которого подключен к управляющим входам первого и второго элементов задержки, при этом выход первого элемента задержки каждого блока фазирования подключен к соответствующе.му входу выходного триггера, первый и второй выходы блока приоритета подключены к первому элементу задержки и другому входу фазового детектора блока фаэирования соответственно, а выходы первого и второго инверторов подключены к входу первого элемента задержки и другому входу фазового детектора дополнительного блока фаэирования соответственно, при этом входы блока приоритета являются входами первого и второго опорных сигналов.

1185602

Изобретение относится к радиоI технике и может быть использовано для получения синхросигнала по двум опорным сигналам.

Цель изобретения — получение выходного сигнала, среднего по фазе между двумя опорными сигналами.

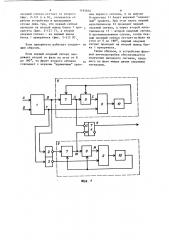

На фиг. изображена структурная электрическая схема устройства фазовой автоподстройки; на фиг. 2 — 10 временные диаграммы работы устройства фазовой автоподстройки; на фиг. 3 — структурная электрическая схема блока приоритета устройства фазовой автоподстройки. 15

Устройство фазовой автоподстройки содержит блок 1 приоритета, первый и второй инверторы 2 и 3, выходной триггер 4, блок 5 фазирования, дополнительный блок 6 фазирования.

Каждый блок фазирования содержит первый и второй элементы 7 и 8 задержки, фазовый детектор 9 и интегратор 10. Блок 1 приоритета содержит

0-триггер 11, первый и второй мульти-25 плексоры 12 и 13.

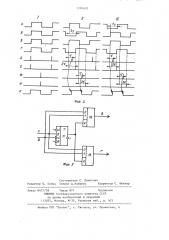

Рассмотрим работу устройства фазовой автоподстройки с помощью временных диаграмм (на фиг. 2 буквами

А, Б, ..., К отмечены эпюры сигналов 30 в одноименных точках А, Б,...,К устройства фазовой автоподстройки частоты).

Пусть форма опорных сигналов А и

Б — меандр, при этом возможны три случая: опорные сигналы синфазны (фиг. 2-I) первый опорный сигнал А опережает второй (фиг. 2-II), второй опорный сигнал Б опережает первый (фиг. 2-III).

4О

Когда опорные сигналы синфазны, то выходные сигналы блока 1 приоритета также синфазны (фиг. 2-I В и Г).

Установившийся режим в обоих блоках

5 и 6 фазирования возможен только при синфазности сравниваемых фазовыми детекторами 9 сигналов, поэтому импульс на втором элементе 8 задержки (фиг. 2-I Е) в блоке 5 фазирования совпадает во времени с фронтом сигнала на первом выходе блока 1 приоритета (фиг. 2-I В), а импульс на выходе второго элемента 8 задержки дополнительного блока 6 фазирования (фиг. 2-1 И) совпадает во времени со спадом сигнала на первом выходе блока 1 приоритета (фиг. 2-I В). Очевидно, что такое положение возможно лишь при нулевом времени задержки элементов 7 и 8 задержки в блоках фазирования. Таким образом, выходные импу. ьсь1 блоков 5 и 6 фазирования (фиг. 2-I Д и Ж), образующиеся на выходах первых элементов 7 задержки, также совпадают соответственно с фрон том и спадом сигнала на первом выходе блока 1 приоритета. Поскольку указанные импульсы управляют установкой и сбросом выходного триггера 4, то на его выходе формируется сигнал, совпадающий пофазе сопорным сигналом.

Когда первый опорный сигнал приходит раньше второго (фиг. 2-II А и Б), то он появляется на первом выходе, блока 1 приоритета, в то время как второй опорный сигнал появляется на втором выходе блока 1 приоритета. J (фиг. 2-II В и Г). В блоке 5 фазирования как и в прежнем случае поддерживается синфазное состояние, т.е. импульс на выходе второго элемента

8 задержки (фиг. 2-II Е)совпадает во времени с фронтом сигнала на втором выходе блока 1 приоритета (фиг . 2-II Г). При этом на выходе фазового детектора 9 блока 5 фазирования фазовой ошибки нет и, следовательно, напряжение на его интеграторе 10 остается постоянным. При изменении времени задержки t3 между опорными сигналами фазовый детектор

9 блока 5 фазирования фиксирует рассогласование, что приводит к соответствующему приращению напряжения на интеграторе 10 и согласованному из/ менению времени задержки с элементов 7 и 8 задержки в направлении компенсации выявленного фазового рассогласования. В результате всегда выполняется соотношение t, =2, и импульс первого элемента 7 задержки блока 5 фазирования (фиг. 2-II Ф) располагается точно между фронтами опорных сигналов. Так как этот импульс взводит выходной триггер 4, то фронт выходного сигнала (фиг. 2-II. К) всегда располагается в центре между фронтами опорных сигналов. Точно также с помощью дополнительного блока 6 фазирования в центре между спадами опорных сигналов обеспечивается сброс выходного триггера 4 (фиг. 2-II Ж), т.е. формируется спад выходного сигнала (фиг. 2-II К).

Работа устройства фазовой автоподстройки в случае, когпа первый з 1l опорный сигнал отстает от второго (фиг. 2-III A и Б), отличается от работы устройства в предыдущем случае srrrrrrr» тем, что первый сигнал проходит на второй выход блока 1 приоритета (фиг. 2-III Г), а второй опорный сигнал — на первый выход блока 1 приоритета (фиг. 2-III В).

Блок приоритета работает следующим образом.

Если первый опорный сигнал опережает второй по фазе на угол от 0

О до 180, то фронт второго сигнала совпадает с верхним "единичным" уров85602 4 нем первого сигнала, и на выходе

D-триггера 11 будет верхний "единичный" уровень. При этом через первый мультиплексор 12 проходит первый опорный сигнал, а через второй мультиплексор 13 - второй опорный сигнал.

В противоположном случае, когда первый опорный сигнал отстает по фазе на угол от 0 до 180, первый опорный сигнал проходит на второй выход блока 1 приоритета.

Таким образом, в устройстве фаэовой автоподстройки обеспечивается получение выходного сигнала, среднего по фазе между двумя опорными сигналами.

1 185602

Составитель С. Даниэлян

Редактор Е. Копча Техред А.Бабинед Корректор С. Шекмар

Заказ 6437/58 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4