Устройство для преобразования разности частот двух электрических сигналов в постоянное напряжение

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО-ДЛЯ ПРЕОБРАЗОВАНИЯ РАЗНОСТИ ЧАСТОТ ДВУХ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ В ПОСТОЯННОЕ НАПРЯЖЕНИЕ , содержащее два формирователя импульсов, входы которых являются входами устройства, RS-триггер, два логических элемента И, семь ключей, два интегратора, выполненные на резисторе и усилителе с конденсатором и ключом в цепи отрицательной обратной связи, одновибратор, выход кот-оPoi;o соединен с входом логического элемента И, усилитель-вычитатель, компаратор, схему выборки-хранения, выполненную на усилителе, конденсаторе и ключе, и источник опорного напряжения, выход схемы выборки-хранения является йыхсдом устройства. от. личаюшееся тем, что, с целью повышения быстродействия, в него дополнительно введены резистивный делитель, две RC-цепи, симметрирующий потенциометр, компаратор, RS-триггер, одновибратор, фильтр нижних частот, логический элемент И и ключ, причем выходы первого и второго формирователей импульсов соответственно соединены с S-входами первого и второго RS-триггеров,- R-входы которых соответственно соединены с выходами первого и второго компараторов , прямой выход первого RS-триггера соединен с первым входом третьего логического элемента И и управляющим входом третьего ключа, инверсный выход первого RS-триггера соединен с входом первого одновибратора и управляющими входами четвертого и шестого ключей, инверсный выход первого одновибратора соединен с вторым входом третьего логического элемен00 сд та И, выход которого соединен с управляющим входом первого ключа, прямой выход второго RS-триггера соединен с первым входом второго логического элемента И, инверсный выход второго RS-триггера соединен с входом второго одновибратора и управляющими входами пятого и седьмого ключей, прямой выход второго одновибратора соединен с вторым входом первого логического элемента И, инверсный выход второго одновибратора соединен с вторым входом второго логического элемента И, выход которо-. го соединен с управляющим входом второго ключа, выход первого логического элемента И соединен с управляющим

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„»SSSOV (51)4 H 03 M 1/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,, „""

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3676014/24-21 (22) 31.10.83 (46) 15.10.85. Бюл. ¹ 38 (72) В.А.Марков и В.К.Стрюцков (/1) Всесоюзный научно-исследователь ский институт электроэнергетики (53) 621.317(088.8) (56) Розенблюм Ф.М. Измерительные органы противоаварийной автоматики энергосистем. М.: Энергоиздат, 1981, с. 142-143.

Авторское свидетельство СССР № 505968, кл. С 01 R 23/06, 1976.

Стрюцков В.К., Рабинович P.Ñ.

Технические средства частотной автоматики энергоси тем. Обзор. Информэнерго, М., 19о2, с. 43.

Ковалев А.М., Барьюдин Э.Л.

Быстродействующий аналоговый измеритель скольжения. — ЭТ в A 1978, вып. 8, с. 268-273. (54)(57) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ РАЗНОСТИ ЧАСТОТ ДВУХ ЭЛЕКТРИЧЕС—

КИХ СИГНАЛОВ В ПОСТОЯННОЕ НАПРЯУ(ЕНИЕ, содержащее два формирователя импульсов, входы которых являются входами устройства, RS-триггер, два логических элемента И, семь ключей, два интегратора, выполненные на резисторе и усилителе с конденсатором и ключом в цепи отрицательной обратной связи, одновибратор, выход которого соединен с входом логического элемента И, усилитель-вычитатель, компаратор, схему выборки-хранения, выполненную на усилителе, конденсаторе и ключе, и источник опорного напряжения, выход схемы выборки-хранения является выходом устройства, о т л и ч а ю ш е е с я тем, что, с целью повышения быстродействия, в него дополнительно введены резистивный делитель, две RC-цепи, симметрирующий потенциометр, компаратор, RS-триггер, одновибратор, фильтр нижних частот, логический элемент И и ключ, причем выходы первого и второго формирователей импульсов соответственно соединены с Б-входами первого и второго RS-триггеров, R-входы которых соответственно соединены с выходами первого и второго компараторов, прямой выход первого RS-триггера соединен с первым входом третье- Е

ro логического элемента И и управляю- уу щим входом третьего ключа, инверсный выход первого RS-триггера соединен С с входом первого одновибратора и управляющими входами четвертого и шестого ключей, инверсный выход перМаЙ вого одновибратора соединен с вторым . Вю 4 входом третьего логического элеменJ та И, выход которого соединен с управляющим входом первого ключа, прямой выход второго RS-триггера, © соединен с первым входом второго логического элемента И, инверсный выход второго RS-триггера соединен с входом второго одновибратора и управляющими входами пятого и седьмого ключей, прямой выход второго одновибратора соединен с вторым входом . В первого логического элемента И, инверсный выход второго одновибратора соединен с вторым входом второго логического элемента И, выход которо-. го соединен с управляющим входом второго ключа, выход первого логического элемента И соединен с управляющим

1i 85607

30 . ходом восьмого ключа, ppэистивный пrëèòель подключен между общей шиной устройства и движком симметрирующего потенциометра, крайние выводы которого соответственно соединены с. входами первой и второй RC-цепей, выходы которых соответственно соединены с первыми входами первого и второго компараторов и соответственно через шестой и седьмой ключи — с общей шиной устройства„ вторые входы первого н второго компараторов соединены со

ll

Изобретение относится к электротехнике и предназначено для использования в регуляторах электрических машин переменного тока и в аппаратуре для их испытаний ° Оно может также найти применение в устройствах противоаварийной автоматики энергосистем.

Цель изобретения — повышение быстродействия у.тройства за счет перехода на однопериоцный цикл преобраэова19 ния .

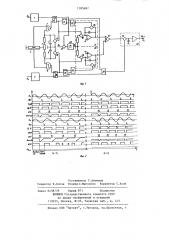

На фиг. 1 изображена схема устройства; на фиг. 2 — временные диаграммы работы устройства.

Устройство содержит формировате15 ли 1 и 2 импульсов, реэистивный делитель 3, симметрирующий потенциометр 4. первую 5 и вторую б RC-цепи, компараторы 7 и 8, RS-триггеры 9 и l0 одновнбраторь. 11 и 12, логические элементы И 13 и 14, ключи 15 — 22, фильтр 23

N нижних частот, интеграторы 24 и 25, логический элемент И 26, усилительвычитатель 2 1, схему 28 выборкихранения.

Входы формирователей 1 и 2 являются входами устройства. Выходы формирователей 1 и 2 соответственно соединены с S-входами RS-триггеров 9 и 10, R-входы RS-триггеров 9 и 10 соответственно соединены с выхоцами компараторов 7 и 8, прямой выход

RS-триггера 9 соединен с входом логического элемента И 13 и управляю— щим входом ключа 17, прямои

К8-триггера 10 соединен с входом логического элемента И 14, инверсные средней точкой реэистивного делителя, источник опорного напряжения через третий ключ соединен с входом фильтра нижних частот, выход которого соединен с входами первого и второго интеграторов, четвертый и пятый ключи включены соответственно между резистором и инвертирующим входом первого и второго интеграторов, выходы интеграторов соединеныс входамиусилителя . вычитателя,выход которого соединен с входом устройства выборки-хранения.

2 выходы RS-триггеров 9 и 10 соответственно соединены с входами одновиб раторов 11 и 12 и соответственно соединены с управляющими входами ключей 15 и 18 и 16 и 19, прямые выходы одновибраторов 11 и 12 соединены с входами логического элемента И 26, инверсные выходы одновибраторов 11 и 12 соответственно соединены с вторыми входами логических элементов И 13 и 14, выходы . огических элементов И 13 и 14 соответственно соединены с управляющими входами ключей 20 и 21, выход логического элемента И 26 соединен с управляющим входом ключа 22,резистивный делитель 3 подключен между общей шиной устройства и движком симметрирующего потенциометра 4, крайние выводы которого соответственно соединены с входами первой 5 и второй б RC-цепей, выходы которых соответственно соединены с входами комлараторов 7 и 8 и соответственно через ключи 15 и 16 с общей шиной устройства, средняя точка резистивного делителя 3 соединена с вторыми входами компараторов 7 и 8, источник опорного напряжения U через ключ 17 соединен с входом фильтра 23 нижних частот, выход которого соединен с входами интеграторов 24 и 25, клю-! чи 18 и 19 соответственно включены между резистором и инвертирующим входом усилителя интеграторов 24 и 25, выходы которых соединены с входами усилителя †вычитате 27, выход

118560 которого соединен с входом схемы 28 выборки-хранения через ключ 22, выход схемы 28 выборки-хранения явля- . ется выходом устройства.

Устройство работает следующим 5 образом.

Один раз в период по переходу синусоидальных напряжений По и Пс через нуль (диаграмма сигналов на фиг. 2) входные формирователи 1 и 2 формируют импульсы на переброс

RS-триггеров 9 и 10 в единичное состояние. При этом сигналами с инверсР ных выходов этих триггеров осуществляется запуск одновибраторов 11 и 12 15 и управление работой двух групп ключей. Так, по сигналу от триггера 9 размыкаются ключи 1.5 и 18, в резуль- тате чего начинается заряд конденсатора RC-цепи 5, а интегратор 24 пере- 20 водится в режим хранения накопленного сигнала. Одновременно по сигналу с прямого выхода триггера 9 замыкается ключ 17, и вход фильтра 23 нижних частот подключается к источ- 25 нику опорного напряжения.

По сигналу с инверсного выхода триггера 10 размыкаются ключи 16 и 19„ чем обеспечивается заряд конденсатора RC-цепи б и перевод в ре- З0 жим запоминания интегратора 25.

Заряд конденсаторов RC-цепей 5 и 6 происходит с одинаковой скоростью (так как постоянные времени двух RC-цепей р .вны) H продолжается 35 до момента срабатывания компараторов 7 и 8, выходные сигналы которых возвращают триггеры 9 и 10 .в исходные состояния.

Время нахождения триггеров 9

40 и 10 в единичном состоянии должно г» удовлетворять соотношению = Т с шЫ(Т /Т,.), где TP и Т вЂ” йериоды входных сигналов. Соответственно длительность временных интервалов, 45 отрабатываемых одновибратбрами 11

7 4 и 12 = 0 9 . При .выполнении а о указанных условий время замыкания ключей 20 и 21 определяется разностью временных интервалов Фо С1 ("1g)

Сигналы такой длительности формируются с помощью элементов И 13 и 14 соответственно. В моменты времени, когда ключи 20 и 21 разомкнуты, а ключи 18 и 19 замкнуты, интеграторы 24 и 25 интегрируют выходной сигнал фильтра 23 нижних частот, который пропорционален частоте напряжения U . В моменты времени, когда оба ийтегратора 24 и 25 находятся в режиме хранения, по факту совпа дения логических сигналов от двух одновибраторов 11 и 12 с помощью элемента И 26 формируется импульс на открытие ключа 22 схемы 28 выборки-хранения, разностный сигнал с выхода усилителя-вычитателя 27 переписывается в эту схему, где хранится до следующего цикла преобразования.

Реализуемый в предлагаемом устройстве процесс преобразования относительной разности двух частот в постоянное напряжение может быть описан следующими выражениями:

U„=U) KP (TP )

Пг =ПзКс(Тс о) ь т 1 . U =U — при К =К ==- и U =К о оТ

P р о о имеем, Применение предлагаемого устройства в энергетике позволяет улучшить качество процесса регулирования асинхронизированных синхронных машки, расширяет их области устойчивости, что в конечном итоге повышает эксплуатационную надежность электрических станций с такими машинами.

1185607

Составитель Г.Антипов

Редактор E,Êîï÷à Техред С.Мигунова Корректор Т.Колб

Заказ 6438/59 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4