Способ когерентного приема сигналов амплитудно-фазовой модуляции и устройство для его осуществления

Иллюстрации

Показать всеРеферат

1. Способ когерентного приема сигналов амплитудно-фазовой модуляции , заключающийся в том, что входной аналоговый сигнал амплитуднофазовой МОДУЛЯ1ДИИ с неизвестной фазой преобразуют в дискретный несинхронный сигнал амплитудно-фазовой модуляции, выделяют дискретный синхронный низкочастотный сигнал амплитудно-фазовой модуляции и преобразуют его в сигнал цифровой информации , отличающийся тем, что, с целью повышения помехоустойчивости при скачкообразном изменении фазы, перед выделением дискретного синхронного низкочастотного сигнала амплитудно-фазовой модуляции дискретный несинхронный сигнал амплитуднофазовой модуляции преобразуют в дискретный несинхронный низкочастотный сигнал амплитудно-фазовой модуляции и выделяют сигнал неизвестной фазы. 2. Устройство для когерентного приема сигналов амплитудно-фазовой модуляции, содержащее блок тактовой синхронизации, опорный генератор, выход которого подключен к входу фазовращателя , а в синфазном и квадратурном подканалах перемножитель, выход которого подключен к входу фильтра, выход которого соединен с первым входом дискретизатора, второй вход которого соединен с выходом блока тактовой синхронизации, вход которого подключен к первому входу перемножителя синфазного подканала и к первому входу перемножителя квадратурного подканала, второй вход которого соединен с выходом фазовращателя, вход которого соединен с вторым входом перемножителя синфазного подка (Л нала, отличающееся тем, что в него введены основной накопитель -и сумматор, а в синфазный и квадратурный подканалы т последовательно соединенные блок снятия манипуляции , дополнительный накопитель, делитель уровня сигнала, линия задержки , блок снятия фазового рассогла00 сования, решающий блок и квадратор, сд выход которого подключен к соответстО ) вующему входу сумматора, выход кото4; рого пoд cлючeн к входу основного накопителя , выход которого подключен к второму входу делителя уровня сигнала синфазного подканала и к второму входу делителя уровня сигнала квадратурного подканала, выходы дискретизаторов синфазного и квадратурного подканалов соединены с первыми входами блоков снятия манипуляции и с вторыми входами блоков снятия фазового рассогласования , выходы решающих блоков подключены к вторым входам блоков снятия манипуляции, при этом второй вход блока снятия манипуляции син-

(21) 3633968/24-09 (22) 05.08.83 (46) 15. 10 . 85. Бюл, У 38 (72) В.А. Балашов, П. Я. Нудельман, В.В. Пантелеев и Ю.В, Шевченко (71) Одесский электротехнический институт связи им. А.С. Попова (53) 621.394.62(088.8) (56) Авторское свидетельство СССР

Р 698151, кл, H 04 L 27/18, 1978.

Патент ФРГ N 2101804, кл. Н 04 ?. 27/22, 1978. (54) СПОСОБ КОГЕРЕНТНОГО IIPHEHA СИГНАЛОВ АМПЛИТУДНО-ФАЗОВОЙ МОДУЛЯЦИИ И

УСТРОИСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ. (57) 1. Способ когерентного приема сигналов амплитудно-фазовой модуляции, заключающийся в том, что входной аналоговый сигнал амплитуднофазовой модуляции с неизвестной фазой преобразуют в дискретный несинхронный сигнал амплитудно-фазовой модуляции, выделяют дискретный синхронный низкочастотный сигнал амплитудно-фазовой модуляции и преобразуют его в сигнал цифровой информации, отличающийся тем, что, с целью повышения помехоустой чивости при скачкообразном изменении фазы, перед выделением дискретного синхронного низкочастотного сигнала амплитудно-фазовой модуляции дискретный несинхронный сигнал амплитуднофазовой модуляции преобразуют в дис кретный несинхронный низкочастотный сигнал амплитудно-фазовой модуляции и выделяют сигнал неизвестной фазы.

2. Устройство для когерентного приема сигналов амплитудно-фазовой модуляции, содержащее блок тактовой синхронизации, опорный генератор, выход которого подключен к входу фазовращателя, а в синфазном и квадратурном подканалах перемножитель, выход которого подключен к входу фильтра, выход которого соединен с первым входом дискретизатора, второй вход которого соединен с выходом блока тактовой синхронизации, вход которого подключен к первому входу перемножителя синфазного подканала и к первому входу леремножителя квадратурного подканала, второй вход которого соединен с выходом фазовращателя, вход которого соединен с вторым вхо дом перемножителя синфазного подка9 нала, отличающееся тем, что в него введены основной накопитель.и сумматор, а в синфаэный и квадратурный подканалы †. последовательно соединенные блок снятия манипуляции, дополнительный накопитель, iaaL делитель уровня сигнала, линия за- :, держки,блок снятия фазового рассогла- . "р сования, решающий блок и квадратор, выход которого подключен к соответствующему входу сумматора, выход которого подключен к входу. основного накопителя, выход которого подключен к второму входу делителя уровня сигнала синфазного подканала и к второму входу делителя уровня сигнала квадратурного подканала, выходы дискретиэато- е ров синфазного и квадратурного подканалов соединены с первыми входами блоков снятия манипуляции и с вторыми входами блоков снятия фазового рассогласования, выходы решающих блоков подключены к вторым входам блоков снятия манипуляции, при этом второй вход блокас снятия манипуляции син1185640 разного подканала соединен с третьим входом блока снятия манипуляции квадратурного подканала, второй вход которого подключен к третьему входу блока снятия манипуляции синфазного подканала, первый вход блока снятия фазового рассогласования которого соединен с третьим входом блока снятия фазового рассогласования квадра. турного подканала,, первый вход которого подключен к. третьему входу блока снятия фазового рассогласования синфазного подканала,второй вход

Изобретение относится к технике связи и может быть использовано в устройствах преобразования сигналов. систем передачи данных, Целью изобретения является повы— шение помехоустойчивости при скачкообразном изменении фазы.

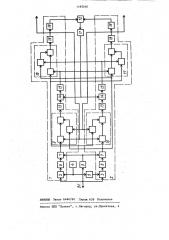

EIa чертеже изображена структурная электрическая схема устройства для .осуществления предлагаемого способа.

Устройство содержит синфазный 1 и квадратурный 2 подканалы, перемножители 3, опорный генератор 4, фазовращатель. 5, фильтры 6, дискретизаторы 7, блок 8 тактовой синхронизации, блок 9 снятия манипуляции синфазного подканала, блок 10 снятия манипуляции квадратурного канала, основной накопитель 11, сумматор 12, дополнительные накопители 13, делители 14 уровня сигнала, линии

15 задержки, блок 16 снятия фазового рассогласования синфазного канала, блок 17 снятия фазового рассогласования квадратурного канала, решающие блоки 18, квадраторы 19, Прием сигналов амплитудно-фазо- вой модуляции осуществляется следующим образом, Принимаемый сигнал амплитуднофазовой модуляции поступает на первый вход перемножителей 3 синфазного 1 и квадратурного 2 подканалов, на вторые входы которых подано напряжение от (несинхронного) опорного генератора 4, частота которого равкоторого соединен с четвертым входом блока снятия фазового рассогласования квадратурного подканала, второй вход которого соединен с четвертым входом блока снятия фазового рассогласования синфазного подканала, выход дискретизатора которого подключен к четвертому входу блока снягия манипуляции квадратурного подканала, выход дискретизатора которого подключен к четвертому входу блока снятия манипуляции синфаэного подкана ла. на частоте принимаемого сигнала, а фаза случайна. Напряжение (несинхронного} опорного генератора 4, поданное на перемножитель 3 квадратурного подканала, сдвинуто по фазе на

90 посредством фаэовращателя 5. Выходы перемножителей 3 параллельно через фильтры 6 поступают на первые входы дискретизаторов 7, на вторые

10 входы которых подано напряжение от блока 8 тактовой синхронизации, работающего по входному сигналу, поступающего на его вход.

15 Входы дискретиэаторов 7 соединены с входами блоков 9 и 10 снятия манипуляции по синфаэному 1 и квадратурному 2 подканалам. ур С другой стороны выходы дискретизаторов 7 соединены с входами блоков 16 и 17 снятия фазового рассогласования по синфазному 1 и квадратурному 2 подканалам. Вторые входы блоков 16 и 17 снятия фазового ра.ссогласования соединены с выходами дискретизаторов 7 синфазного (квадратурного) подканала, а первые их входы через линии 15 задержки соединены с делителем 14 уровня сигнала.

Четвертые входы блоков 16 и 17 снятия фазового рассогласования соединены с выходом дискретизатора 7 квадратурного 2 подканала (синфазного 1 подканала), а третьи их вхо35 ды через линию 15 задержки соединены с делителем 14 уровня сигнала

3 квадратурного 2 подканала 1 (синфазного 1 подканала). Постоянная времени линии 15 задержки равна длительности посылки входного сигнала.

Выходы блоков 16 и 17 снятия фазового рассогласования подключены к входам решающих блоков 18.

Решающие блоки 18 представляют собой ряд пороговых устройств, выносящих решения о синфазной либо квадратурной составляющих входного сигнала в результате минимизации некоторого критерия качества (например, среднеквадратичной ошибки), 1185640

БНИИПИ Заказ 6440/60 ;.Тираж 658 Подписное

Филиал ППП "Патент", г.Ужгород, ул.Проектная, 4