Устройство формирования сигнала для управления столбцами телевизионного матричного экрана

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ФОРМИРОВАНИЯ СИГНАЛА ДЛЯ УПРАВЛЕНИЯ СТОЛБЦАМИ ТЕЛЕВИЗИОННОГО МАТРИЧНОГО ЭКРАНА, содержащее аналогоцифровой преобразователь, вход которого является входом видеосигнала, а разрядные выходы подключены к соответствующим информационным входам первого блока регистров , выходы которого подключены к соответствующим информационным входам второго блока регистров, выходы которого подключены к соответствующим первым информационным входам блока цифроаналоговых преобразователей, а вторые информационные входы блока цифроаналоговых преобразователей поразрядно объединены и подключены к соответствующим выходам счетчика импульсов , первый вход блока сиихронизации соединен с входом сброса счетчика импульсов и является входом синхросигнала, а первый выход блока синхронизации подключен к тактовому входу аналого-цифрового преобразователя и к тактовому входу первого блока регистров, отличающееся тем, что, с целью упрощения устройства путем сокращения разрядности цифроаналоговых преобразователей , в него введены делитель импульсов и логический переключатель, при этом выход логического переключателя соединен с тактовым входом счетчика импульсов, первый информационный вход логического переключателя соединен с тактовым входом делителя импульсов и с тактовым выходом блока синхронизации, второй информационный вход логического переключателя соединен с выходом делителя импульсов, первый управляющий вход логического, переключателя объединен с входом сброса де (Л лителя импульсов и подключен к перрому входу блока синхронизации, а второй управляющий вход логического переключателя объедииен с входом переноса счетчика импульсов и подключен к второму входу блока синхронизации, второй и третий выходы которого подключены соответственно к управляющему и тактовому входам второго блока регистров. 00 СП Од ел ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU „, 1185655 (я)4 Н 04 N 5/66

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, К ABTOPCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3729681/24-09 (22) 21.04.84 (46) 15.10.85. Бюл. 38 (72) А. А. Рысин (53) 621.397(088.8) (56) Kaneko Е. at al. А packet sized liquid сг1з1а!ТЧ display SID, 1981, Digest, р. 84 — 85.

Авторское свидетельство СССР № 1019668, кл. Н 04 N 5/66, 1982. (54) (57) УСТРОИСТВО ФОРМИРОВАНИЯ СИГНАЛА ДЛЯ УПРАВЛЕНИЯ

СТОЛБЦАМИ ТЕЛЕВИЗИОННОГО МАТРИЧНОГО ЭКРАНА, содержащее аналогоцифровой преобразователь, вход которого является входом видеосигнала, а разрядные выходы подключены к соответствующим информационным входам первого блока регистров, выходы которого подключены к соответствующим информационным входам второго блока регистров, выходы которого подключены к соответствующим первым информационным входам блока цифроаналоговых преобразователей, а вторые информационные входы блока цифроаналоговых преобразователей поразрядно объединены и подключены к соответствующим выходам счетчика импульсов, первый вход блока синхронизации соединен с входом сброса счетчика импульсов и является входом синхросигнала, а первый выход блока синхронизации подключен к тактовому входу аналого-цифрового преобразователя и к тактовому входу первого блока регистров, отличающееся тем, что, с целью упрощения устройства путем сокращения разрядности цифроаналоговых преобразователей, в него введены делитель импульсов и логический переключатель, при этом выход логического переключателя соединен с тактовым входом счетчика импульсов, первый информационный вход логического переключателя соединен с тактовым входом делителя импульсов и с тактовым выходом блока синхронизации, второй информационный вход логического переключателя соединен с выходом делителя импульсов, первый управляющий вход логического, пере- @ ключателя объединен с входом сброса делителя импульсов и подключен к первому входу блока синхронизации, а второй управляющий вход логического переключателя { объединен с входом переноса счетчика импульсов и подключен к второму входу блока Я синхронизации, второй и третий выходы которого подключены соответственно к управляющему и тактовому входам второго блока регистров.

МЮ

1185655

Изобретение относится к технике телевидения и может использоваться в устройствах отображения информации на матричных экранах.

Цель изобретения — упрощение устройства путем сокращения разрядности цифроаналоговых преобразователей.

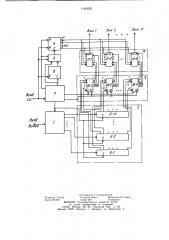

На чертеже приведена структурная электрическая схема устройства формирования сигнала для управления столбцами телевизионного матричного экрана.

Устройство формирования сигнала для управления столбцами телевизионного матричного экрана содержит аналого-цифровой преобразователь 1, первый и второй блоки 2 и 3 регистров, блок 4 цифроаналоговых преобразователей, счетчик 5 импульсов, логический переключатель 6, блок 7 синхронизации и делитель 8 импульсов. При этом первый блок 2 регистров состоит из N последовательно-параллельных К-разрядных сдвиговых регистров 9 — i, где l

2 сравнения кодов.

Устройство работает следующим образом.

Видеосигнал со входа устройства поступает на аналого-цифровой преобразователь 1 на N выходных разрядах которого вырабатывается цифровой код, соответствующий исходному сигналу. С выходов аналогоцифрового преобразователя 1 сигнал поступает на первый блок 2 регистров, состоящий из N последовательно-параллельных К-разрядных сдвиговых регистров 9 — i, где К— число столбцов матричного экрана. За один цикл строчной развертки блок 2 регистров полностью загружается с приходом синхроимпульса на вход блока 7 синхронизации.

Второй блок 3 регистров, состоящий из К последовательно-параллельных N-разрядных сдвиговых регистров 10 вЂ, устанавливается в режим параллельной записи информации.

При этом вся информация, накопленная в блоке 2 регистров одновременно переписывается в блок 3 регистров таким образом, что в каждом регистре 10 — j блока 3 регистров записывается информация с одноименных разрядов блока 2 регистров. При этом старшие N/2 разряды блока 3 регистров подключены к первым информационным входам блока 4 цифроаналоговых преобразователей, в качестве которых использованы

К элементов,11 †сравнения кодов. Одновременно с приходом синхроимпульса осуществляется сброс N/2 разрядного счетчика

5 импульсов в нулевое состояние и переключение логического переключателя 6 в режим, при котором тактовые импульсы с блока 7 синхронизации через делитель 8 с коэффициентом деления 2" — 1 поступают на тактовый вход счетчика 5 импульсов.

Выходы счетчика 5 подключены к поразрядно объединенным вторым информационным входам блока 4 цифроаналоговых преобразователей. В момент сравнения значения кодов на первых и вторых информационных входах любого из элементов 11 †сравнения блока 4 цифроаналоговых преобразователей на его выходе a)b, являющемся одним из

К выходов устройства, происходит переключение сигнала из единичного в нулевое состояние. При этом осуществляется преобразование кода старших разрядов блока 3 регистров в длительность импульсов, пропорциональную этому коду. Максимально возможному значению кода на выходе блока 3 регистров соответствует полная загрузка счетчика 5. При этом на выходе переноса счетчика 5 вырабатывается импульс, по которому осуществляются переход логического переключателя 6 в режим, при котором тактовые импульсы с блока 7 синхронизации через логический переключатель 6, минуя делитель 8, поступают на тактовый вход счетчика 5; выработка блоком 7 синхронизации управляющих сигналов, по которым осуществляется сдвиг информации в блоке 2 регистров на N/2 тактов в сторону старших разрядов, а также стробирование на время сдвига тактовых импульсов, вырабатываемых блоком 7 синхронизации.

При этом младшие разряды блока 3 регистров занимают место старших разрядов и подключаются к первым информационным входам блока 4 цифроаналоговых преобразователей, а на тактовый вход счетчика 5 поступают импульсы с частотой в 2 " — 1 раза выше, чем при обработке старших разрядов. На выходах элементов 11 — j вновь формируются импульсы, длительность которых пропорциональна кодам младших разрядов сигнала, первоначально записанного в блок 3 регистров. Таким образом суммарная длительность двух импульсов на каждом выходе блока 4 цифроаналоговых преобразователей получается пропорциональной значению исходного кода.

1185655 дых 1

Составитель А. Прозоровский

Техред И. Верес Корректор В. Гнрняк

Тираж 658 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 7К вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Реда кто р Т. Колб

Заказ 6441/6!