Устройство для контроля @ -разрядных схем сравнения

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ N-РАЗРЯДНЫХ СХЕМ СРАВНЕНИЯ, содержащее счетчик, элемент И, дешифратор , два триггера, блок анализа выходных сигналов, причем первый вход элемента И подключен к тактовой шине устройства, выход элемента И соединен со счетным входом счетчика, выход сравнения и два выхода несравнения контролируемой N -разрядной схемы сравнения соединены с первым, вторым, третьим информационными входами блока анализа выходных сигналов соответственно, прямые выходы триггеров соединены с четвертым, пятым информационными входами блока анализа выходных сигналов соответственно , выход которого является выходом ошибки, отличающееся тем, что, с целью повышения производительности путем устранения избыточности комбинаций входных переменных для N -разрядной схемы сравнения, в него введен ()-разрядный регистр сдвига, причем выход блока анализа выходных сигналов соединен с вторым входом элемента И, выход которого объединен с синхровходом (N-fl)-раз рядно го регистра сдвига, синхровходами первого и второго триггеров, информационные выходы счетчика соединены с соответству ющими информационными входами дешифратора , первый выход которого объединен с входами 3 и К первого триггера , второй выход дешифратора соединен с входом обнуления счетчика, прямой выход первого триггера объединен с входом К второго триггера и входом последовательной записи (N+1)-разряд00 ного регистра сдвига, инверсный выход -4 первого триггера соединен с входом второго триггера.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4

ОПИСАНИЕ ИЗОБРЕТ

К ABTOPCKOIVlV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3742290/24-24 (22) 18.05.84 (46) 23.10.85. Бюл. ))- 39 (72) В.М.Пермяков (53) 681.3(088.8) (56) Авторское свидетельство СССР

Ф 1012264, кл. С 06 F 11/26, 1981.

Авторское свидетельство СССР

N - 970377, кл. G 06 F 11/26, 1981. (54)(57) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

Й-РАЗРЯДН61Х СХЕМ СРАВНЕНИЯ, содержащее счетчик, элемент И, дешифратор, два триггера, блок анализа выходных сигналов, причем первый вход элемента И подключен к тактовойшине устройства, выход элемента И со. единен со счетным входом счетчика, выход сравнения и два выхода несравнения контролируемой N -разрядной схемы сравнения соединены с первым, вторым, третьим информационными входами блока анализа выходных сигналов соответственно, прямые выходы триггеров соединены с четвертым, пятым информационными входами блока анализа выходных сигналов соответственно, выход которого является выходом ошибки, о т л и ч а ю щ ее с я тем, что, с целью повышения производительности путем устранения избыточности комбинаций входных переменных для )1 -разрядной схемы сравнения, в него введен (М+1)-разрядный регистр сдвига, причем выход блока анализа выходных сигналов соединен с вторым входом элемента И, выход которого объединен с синхровходом (N41)-разрядноro регистра сдвига, синхровходами первого и второго триггеров, информационные выходы счетчика соединены с соответствующими информационными входами дешифратора, первый выход которого объединен с входами 1 и K первого триггера, второй выход дешифратора соединен с входом обнуления счетчика, прямой выход первого триггера объединен с входом 1(второго триггера и входом последовательной записи (Я+1)-разряд— ного регистра сдвига, инверсный выход первого триггера соединен с входом второго триггера.

1 11871

Изобретение относится к автомати" ке и вычислительной технике и может быть использовано для входного конт" роля интегральных микросхем, выполняющих функции сравнения чисел, а также при реализации технических средств контроля электронных блоков дискретной автоматики и вычислительной техники.

Цель изобретения — повышение про-.!О изводительности устройства для контроля N -разрядных схем сравнения двоичных чисел.

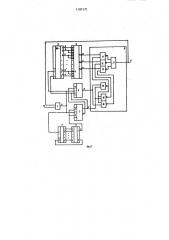

На фиг. 1 приведена функциональная схема; на фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство содержит элемент И 1, счетчик 2, (N +1)-разрядный регистр 3 20 сдвига, контролируемую схему 4 сравнения, дешифратор 5, триггеры 6 и 7, блок 8 анализа выходных сигналов, выход 9 устройства и вход 10 тактовых импульсов, четыре элемента 25

ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 11-14, два элемента И-НЕ 15 и 16 и элемент И 17.

Элемент ИСКГПОЧАЯЩЕЕ ИЛИ-НЕ 11-14, элементы И-НЕ 15 и 16, элемент И 17. входят в состав блока 8 анализа вь1- . З0 ходных сигналов.

Выходы 1,2, ..., N регистра 3 сдвига подключены к первой группе входов контролируемой схемы 4 сравнения, а выходы 2, 3, ..., (N+1) З5 подключены к второй группе ее входов. Первые же три входа блока 8 анализа выходных сигналов подключены к выходам контролируемой схемы 4 сравнения, четвертый и пятый входы 40 соединены соответственно с прямыми выходами триггеров 6 и 7. Прямой выход триггвра 7 подсоединен также к К -входу триггера 6 и входу последовательной записи регистра 3 сдвига. Инверсный вход триггера 7 соединен с 3 -входом триггера 6.

Входы и К триггера 7 соединены с первым выходом дешифратора 5.

Второй выход дешифратора 5 соединен с К вЂ вход счетчика 2, выходы которого соединены с входами дешифратора 5. Выход блока 8 анализа выходных сигналов подключен к первому входу элемента И 1, разрешая прохож- дение тактовых импульсов с шины 10 тактовых импульсов на вход синхронизации регистра 3 сдвига, счетный

71 2 вход счетчика 2 и счетные входы триггеров 6 и 7.

Число А поступает на первую группу входов контролируемой схемы 4 сравнения, число  — на вторую группу входов. Счетчик 2, триггеры

6 и 7, регистр 3 сдвига изменяют свое состояние по заднему фронту тактового импульса.

Устройство работает следующим образом.

В исходном состоянии все разряды регистра 3 сдвига установлены в единичное состояние, а триггеры 6 и 7 и счетчик 2 — в нулевое состояние сигналом "Установка" (цепь сигнала и !Ф

Установка не показана). На четвертом и пятом входах блока 8 анализа выходных сигналов — нулевые уоовни, что соответствует равенству чисел

А и В по "единицам". На выходе 9 устройства — единичный уровень, сигнализирующий об исправности контролируемой схемы 4 сравнения и разрешающий прохождение тактовых импульсов через элемент И -1 на счетные входы триггеров 6 и 7, счетчика 2 и вход синхронизации регистра 3 сдвига. На входе последовательной записи регистра 3 сдвига — нулевой уровень, что является подготовкой записи "нуля" в первый разряд. По заднему фронту первого тактового импульса в первый разряд регистра записывается "нуль", и триггер 6 переключается из

"нуля" в единицу". На четвертом и пятом входе блока 8 анализа выходных сигналов устанавливаются соответственно уровни "1" и "0", что соответствует проверке на неравенство А (В. В случае исправности контролируемой схемы 4 сравнения на выходе блока 8 анализа выходных сигналов сохраняется единичный уровень. По заднему фронту второго тактового импульса нуль сдвигается во второй разряд и снова записывается в первый разряд регистра 3 сдвига.

Неравенство А < В сохраняется, состояние триггеров 6 и 7 также не изменяется. Таким образом, на каждом такте проверяется один разряд на неравенство А (В при равенстве остальных разрядов. Счетчик 2 подсчитывает поступающие импульсы. При поступлении N-го импульса на первом выходе дешифратора 5 появляется еди-, 11871 ничный уровень, устанавливая триг:гер 7 в счетный режим. По (И+1)-му импульсу триггер 7 переключается из "нуля" в "единицу". На первом выходе деши@ратора 5 устанавливается нулевой уровень, который запрещает переключаться триггеру 7 по последующим тактовым импульсам, .а на втором выходе появляется единичный уровень, который устанавливает счет- 10 чик 2 в нулевое состояние. В результате обнуления .счетчика на втором выкоде дешийратора 5 снова устанавливается нулевой уровень.

На четвертом и пятом входе блока 8 ц5 анализа выходных сигналов — единичные уровни, что соответствует этапу проверки схемы 4 сравнения на равенство чисел А и В по всем "нулям". На выходе 9 устройства сохраняется единичный уровень в случае исправности схемы 4 сравнения. На входе последовательности записи регистра 3 сдвига — единичный уровень. Тем самым подготовлена запись "единицы" в пер- 25 вый разряд и, как результат — проверка первого разряда схемы 4 сравнения на неравенство А> В. По (8+2)-му импульсу "единица" записывается в первый разряд регистра 3 сдвига, а триггер 6 переключается . из "единицы" в "нуль". На четвертом и пятом входах блока 8 анализа выходных сигналов. устанавливаются уровни "О™ и "1", что

35 соответствует проверке на неравенство А» В. На выходе блока 8 анализа выходнык сигналов в случае исправной работы сохраняется еди71 4 ничный уровень. Остальные разряды схемы 4 сравнения проверяются таким же образом. По (2М+1)-.му импульсу на первом выходе дешифратора 5 появляется единичный уровень. По 2(И+1)-му импульсу устройство возвращается в исходное состояние. Следовательно, полная проверка схемы 4 сравнения на работоспособность производится sa 2(Я+1)-тактов частоты тактовых импульсов. Для исправной схемы сравнения в каждом такте работы устройства должны выполняться следующие условия соответствия выходных сигналов схемы 4 сравнения выходным сигналам триггеров 6 и 8:

А=В А >В А сВ Тгб Тг7 Вых.9

1 0 0 0 0 1

0 0 1 1 0 1

1 0 0 1 1 1

1 0 О 1 1

При нарушении этих условий соответствия блок 8 анализа выкодных сигналов дюрмирует на выходе 9 устройства сигнал ошибки нулевым уровнем.

Это приводит к тому, что элемент И 1 закрывается, и тактовые импульсы не поступают на вход синхронизации регйстра 3 сдвига, счетные входы триггера 6 и 7 и счетчика 2. В результате Am сируется неисправное состояние на (2Я+1)-ом такте.

1187171

1187! 71 :3 4 ССз ьэ ИЪ СМ % " X

CQ

З

Составитель А. Сиротская

Редактор Н. Данкулич Техред А,Кикемезей Корректор И. Эрдейи

Заказ 6551/54 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4