Устройство для формирования синхронизирующего сигнала

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ФОРМИРОВАН СИНХРОНИЗИРУЮЩЕГО СИГНАЛА, содержа|| трансформатор, первичная обмотка которого соединена с пантографом, и формирователь импульсов, выход к горого подключен к выходной шине, о личающееся. тем, что, с целью повышения помехозащищеннос1 в него введены дешифратор и микроп цессорный блок, вход которого соед| нен с вторичной обмоткой трансфор5 гора , а выход подключен к входу деши| фратора, выход которого соединен с входом формирователя импульсов. 9

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (l9) (II), SU (51)4 Н 03 К 5 13

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

Il0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

I e(;p(ОПИСАНИЕ ИЗОБРЕ ) ЕНИЯ(::: .„. ц - " :т

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

10 (21) 3680538/24-21 (22) 26. 12 ° 83 (46) 23. 10.85. Бюл. 11) 39 (72) А.Г.Вольвич, М.В.Напрасник и А.В.Беляев (71) Всесоюзный научно-исследовательский, проектно-конструкторский и технологический институт электровозостроения (53) 621.374.2(088.8) (56) Писарев А.Л., Деткин Л.П.

Управление тиристорными преобразователями. M.: 1975, с. 22.

Авторское свидетельство СССР

11) 945952, кл. Н 03 К 1/17, 1980. (54)(57) УСТРОЙСТВО ДЛЯ ФОРМИРОВАН

СИНХРОНИЗИРУЮЩЕГО СИГНАЛА, содержа трансформатор, первичная обмотка которого соединена с пантографом, и формирователь импульсов, выход к рого подключен к выходной шине, о л и ч а ю щ е е с я, тем, что, с целью повышения помехозащищеннос в него введены дешифратор и микроп цессорный блок, вход которого соед нен с вторичной обмоткой трансформ ра, а выход подключен к входу деши фратора, выход которого соединен с входом формирователя импульсов.

j 1187

Изобретение относится к импульс-, ной технике и может быть использовано в системе управления электровозами переменного тока.

Целью изобретения является повыше- 5 ние помехоэащищенностц устройства.

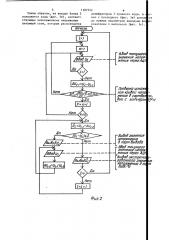

На фиг. 1 приведена функциональная схема устройства для формирования синхронизирующего сигнала; на фиг. 2— блок-схема алгоритма работы микро- 10 процессорного блока; на фиг. 3 - временные диаграммы, поясняющие работу устройства.

Устройство содержит трансформатор 1, вторичная обмотка которого подключена к входу микропроцессорного блока 2, выход которого соединен с входом дешифратора 3, выход которого подключен к входу формирователя 4 импульсов, выход которого соединен с выходной шиной 5, а также пантограф 6,.который соединен с первичной обмоткой трансформатора 1; микропроцессорный блок 2 состоит из АЦП 7, входы которого соединены е шинами 8 и 9 "Ввод" и "Запись адреса", а выход — с шиной 10 адресов-данных, постоянного запоминающего устройства (ПЗУ) 11 входы которого соединены с шинами 8 и 9 "Ввод" и "Запись адреса, а вход-выход — с шиной 10 адресов-данных, порта 12 вывода, входы которого соединены с шиной 9

"Запись адреса", шиной 10 адресовданных и шиной 13 "Вывод", управляющей памяти 14, вход которой соединен З5 с шиной 10 адресов-данных, а выход— с входами системного контроллера 15 и арифметического устройства 16, выход которого соединен с шиной 10 ад40 ресов-данных. Выходы системного контроллера 15 соединены с шинами 8, 9 и 13.

Устройство работает следующим образом. 45

При контакте пантографа 6 с контактным проводом питающей сети во вторичной обмотке трансформатора 1 индуцируется ЭДС (фиг. За). На вход микропроцессорного блока 2 подается 50 напряжение, форма которого повторяет форму напряжения питающей сети и преобразуется АЦП 7 в цифровые коды.

Обработка этих кодов осуществляется арифметическим устройством 16 55 под действием последовательности микрокомаид управляющей памяти 14. Системный контроллер 15 формирует сигналы "Ввод", "Запись! и "Вывод" на шинах 8, 9 и 13, организуя обмен информацией между АЦП 7, ПЗУ 11, портом 12 вывода, арифметическим устройством 16 и управляющей памятью 14.

Цифровые коды обрабатываются в соответствии с блок-схемой алгоритма (фиг. 2). Обработка начинается с "Захватал неискаженной части кривой питающего напряжения. Так как неискаженная кривая представляет собой синусоиду, то проверку искажения можно осуществлять в соответствии с равенством

Sin2x+((sinx5 ) 2=1, ЛП

Цг+()2 П э где U — текущее значение напряжения;

Uff, — амплитуда напряжения; — период преобразования АЦП 7;

ЛБ — приращение напряжения за период преобразования.

Кривая считается "захваченной", если в каждом из m преобразований подряд выполняется неравенство

nUg 1

/U 2 +(-----)-U 2 / Л

Е-1

Ь t

ffl — У где i — номер текущего преобразования;

Л вЂ” величина, соответствующая допустимому искажению кривой напряжения.

После осуществления Захвата" экстраполируется текущее значение напряжения, например, экстраполятором первого порядка д "Ь

Uj =Ц +1 Ц1,-)ht=Ui 1+ Л =П1 1+61- 1. Э °

7t

Если разница между экстраполированным и действительным значениями напряжения меньше или равна допустимой о, то в качестве кода выборки берется код текущего значения напряжения U . Если же неравенство л

/U U;/ b не выполняется, то считается, что в преобразовании произошел сбой, и в качестве результата преобразования принимается значел ние U

При невыполнении неравенства r раз, полагается, что слежение за кривой напряжения утеряно и вновь осуществляется Захват" кривой напряжения. Конкретные значения Л, m о, r определяются частотой преобразования и алгоритмом экстраполяции.

Алгоритм, приведенный на фиг. 2, является одним из возможных. ся

Вброд тпекущег значения налря жВния через АЦ з t

Таким образом, на выходе блока 2 появляются коды (фиг. Зб), соответ-. ствующие неискаженному напряжению питаницей сети, которые распознаются

187252 4 дешифратором 3 нулевого кода. А нал с последнего (фиг. Зв) довод до нужных параметров выходным фо рователем 4 импульсов (фиг. Зг).

Прадерка иская ния криоой нап жения Ф соол7де mIhu c заРх ((ьсп

Вьаод зиачедий напряжения д лопю оидоЯк

Моо 77 жуи его значения набуря жения через Ag

Выдод зкстрало робанного дна я налрярения Фл щ

A Ж- а

1187252 и, Составитель В.Потапов

Редактор 0.1Орковецкая Техред Л.Чартяшова Корректор М.Максимишинец

Заказ 6560/58 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4