Двухполярный стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

ДВУХПОЛЯРНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ, содержащий первый и второй регулирующие элементы, включенные соответственно между первыми входным и выходным и вторыми входным и выходным выводами, первый и второй дифференциальные усилители, выходы которых через первый и второй согласующие каскады соответственно подключены к управляющим входам первого и второго регулирующих элементов соответственно , первый вход первого усилителя и второй вход второго усилителя соединены со средними выводами первого и второго делителей напряжения соответственно, источник опорного напряжения, выполненный на первом, втором, третьем, четвертом и пятом транзисторах и первом и втором резисторах , причем эмиттеры первого и второго транзисторов соединены с первым выходным выводом, базы первого и второго транзисторов объединены, коллектор второго транзистора через третий транзистор связан с вторым выходным выводом и с эмиттером четвертого транзистора, база которого через первый резистор подключена к коллектору пятого транзистора и первому входу второго усилителя, который через пятый транзистор и второй резистор соединен с коллектором первого транзистора, второй делитель включен между вторым выходным выводом и общей щиной, отличающийся тем, что, с целью уменьщения динамической нестабильности выходного напряжения путем (Л уменьшения взаимного влияния каналов, коллектор третьего транзистора соединен с коллектором и базой второго транзистора, база - с базой четвертого транзистора, эмит. тер - с вторым входным выводом через введенный третий резистор, коллектор пятого транзистора соединен с первым входом второго усилителя, база - с общей шиной, эмиттер через второй резистор - с коллектором первого транзистора и вторым входом 00 00 первого усилителя, а первый делитель включен между первым выходным выводом и об to щей щиной.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1188720 A

ug 4 G 05 F 1 585

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3729075/24-07 (22) 18.04.84 (46) 30.10.85. Бюл. № 40 (72) В. И. Анисимов, А. Б. Исаков, М. В. Капитонов, Н. Н. Прокопенко и Ю. М. Соколов (71) Ленинградский ордена Ленина электротехнический институт им. В. И. Ульянова (Ленина) (53) 621.316.722.1 (088.8) (56) Авторское свидетельство СССР № 754394, кл. G 05 F 1/56, 1980.

Полянин К. П. Интегральные стабилизаторы напряжения. — М.: Энергия, 1979, с. 144, рис. 5 — 13. (54) (57) ДВУХПОЛЯРНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ, содержащий первый и второй регулирующие элементы, включенные соответственно между первыми входным и выходным и вторыми входным и выходным выводами, первый и второй дифференциальные усилители, выходы которых через первый и второй согласующие каскады соответственно подключены к управляющим входам первого и второго регулирующих элементов соответственно, первый вход первого усилителя и второй вход второго усилителя соединены со средними выводами первого и второго делителей напряжения соответственно, источник опорного напряжения, выполненный на первом, втором, третьем, четвертом и пятом транзисторах и первом и втором резисторах, причем эмиттеры первого и второго транзисторов соединены с первым выходным выводом, базы первого и второго транзисторов объединены, коллектор второго транзистора через третий транзистор связан с вторым выходным выводом и с эмиттером четвертого транзистора, база которого через первый резистор подключена к коллектору пятого транзистора и первому входу второго усилителя, который через пятый транзистор и второй резистор соединен с коллектором первого транзистора, второй делитель включен между вторым выходным выводом и общей шиной, отличающийся тем, что, с целью уменьшения динамической не- д стабильности выходного напряжения путем уменьшения взаимного влияния каналов, уу коллектор третьего транзистора соединен Ч У с коллектором и базой второго транзистора, база — с базой четвертого транзистора, эмит. тер — с вторым входным выводом через вве- а денный третий резистор, коллектор пятого транзистора соединен с первым входом второго усилителя, база — с общей шиной, эмиттер через второй резистор — с коллектором первого транзистора и вторым входом первого усилителя, а первый делитель включен между первым выходным выводом и об- 00 щей шиной. 3

1188720

Изобретение относится к электротехнике и может использоваться для электропитания радиоэлектронной аппаратуры двухполярным напряжением.

Цель изобретения — уменьшение динамической нестабильности выходного напряжения путем уменьшения взаимного влияния положительного и отрицательного каналов двуполярного стабилизатора постоянного напряжения.

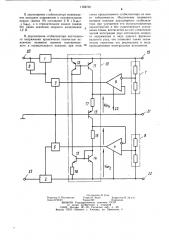

На чертеже приведена принципиальная электрическая схема двуполярного стабилизатора постоянного напряжения.

Стабилизатор содержит первый 1 и второй 2 регулирующие элементы, первый 3 и второй 4 дифференциальные усилители сигнала рассогласования, первый 5 и второй 6 согласующие каскады, первый 7 и второй 8 делители выходного напряжения 8, источник 9 тока и источник 10 опорного напряжения, включающий в себя первый 11, второй 12, третий 13 и четвертый 14 и пятый 15 транзисторы, а также первый 16, второй 17 и третий 18 резисторы. Причем, выход первого регулирующего элемента 1 соединен с эмиттерами транзисторов 11 и 12, входом делителя 7 и первым выходом 19 стабилизатора. Силовой вход регулирующего элемента 1 соединен с первым входом 20 стабилизатора и входом питания источника 9 тока, выход которого связан с управляющим входом регулирующего элемента 1 и через первый согласующий каскад 5 подключен к выходу дифференциального усилителя 3. Первый вход усилителя 3 соединен с выходом первого делителя 7, общий вывод которого связан с общей шиной 21 стабилизатора, к которой также подключены база транзистора 15 и общие выводы согласующих каскадов 5 и 6. Второй вход усилителя 3 соединен с коллектором транзистора 11 и через резистор 17 с эмиттером транзистора 15, коллектор которого подключен к первому входу второго дифференциального усилителя 4 и через резистор 16 связан с коллектором и базами транзисторов 14 и 13. Коллектор транзистора 13 соединен с коллектором транзистора 12 и с базами транзисторов 11 и 12. Эмиттер транзистора 13 через резистор 18 соединен с вторым выходом 22 стабилизатора, к которому также подключены выход второго регулирующего элемента 2, эмиттер транзистора 14, общие выводы первого 3 и второго 4 дифференциальных усилителей и вход делителя 8. Выход делителя 8 соединен с вторым входом усилителя 4, выход которого через согласующий каскад 6 связан с управляющим входом регулирующего элемента 2, а силовой вход элемента 2 соединен с вторым входом 23 стабилизатора.

Источники опорного напряжения положительного и отрицательного каналов выполнены в виде одного функционального узла 10 (элементы 11 — 18).

Статический режим стабилизатора задается источником 9 тока.

Статический режим транзисторов источника 10 опорного напряжения определяется следующим образом.

Транзисторы 13 и 14 выполнены с различными площадями переходов эмиттер — ба за S, причем $э з = ХЯэ«, (где N = 3 — 10)

Тогда, при равных токах эмиттеров этих транзисторов, падение напряжения на прямосмещенных эмиттерных переходах транзисторов 13 и 14 различается на ЬОэ6=

= У,!пМ, где Ут — температурный потенциал.

Таким образом, ток эмиттера транзисторов

11 — 15 однозначно определяется только отношением площадей эмиттерных переходов транзисторов 13 и 14 и значением сопротивления резистора 18: I3 ЬU96/R, . где R

Опорные напряжения Uoa u Uoaqa положительном и отрицательном каналах соответственно определяются следующими соотношениями:

Uoag = 13эб +> 0эб к т/ и 1

U он = U эб «+ Ы зб R 16/3.1 где U>a« U,6, — напряжение эмиттер — база транзисторов 14 и 15 соответственно.

Термокомпенсация опорного напряжения в каждом из каналов стабилизатора осуществляется за счет компенсации отрицательного температурного коэффициента напряжения эмиттер — база транзисторов 14 и 15 положительным температурным коэффициентом разности напряжений эмиттер— база транзисторов 13 и 14. Термостабильность опорного напряжения достигается, если значение опорного напряжения равно экстраполированной ширине запрещенной зоны кремния при абсолютном нуле b.Es « ——

1,205 В.

Стабилизатор постоянного напряжения работает следующим образом. При изменении по какой-либо причине выходного напряжения в положительном канале (вывод 19) часть его через делитель 7 подается на первый вход усилителя 3, где во входной цепи усилителя сравнивается с опорным напряжением U<> Выделенный и усиленный сигнал рассогласования с выхода усилителя 3 через согласующий каскад 5 подается на управляющий вход регулирующего элемента 1, при этом на выходе элемента 1 появляется приращение тока, компенсирующее первоначальное изменение выходного напряжения. Отрицательный канал стабилизатора работает аналогичным образом.

1188720

Составитель В. Есин

Редактор Л. Пчелинская Техред И. Верес Корректор И. Эрдейи

За каз 6744/50 Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и о1крытий! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

В двуполярном стабилизаторе минималь- ное выходное напряжение в положительном канале (вывод 19) составляет 2 В (U o +

+ U zq), а в отрицательном канале (вывод

22) равно значению опорного напряжения

1,2 В.

В двуполярном стабилизаторе постоянного напряжения практически полностью исключено взаимное влияние положительного и отрицательного каналов, при этом схема предлагаемого стабилизатора не имеет избыточности. Исключение взаимного влияния каналов двуполярного стабилизатора при улучшении его эксплуатационных характеристик и без существенного усложнения схемы, достигается за счет схемотехнической интеграции двух источников опорного напряжения в виде единого функционального узла, что позволяет также значительно упростить его реализацию в полупроводниковом интегральном исполнении.