Формирователь синхросигналов

Иллюстрации

Показать всеРеферат

ФОРМИРОВАТЕЛЬ СИНХРОСИГНАЛОВ , содержащий генератор тактовых импульсов, шину запроса и сдвиговый регистр, выходы которого соединены с первыми выходными шинами и первыми вхо3 одами блока элементов И, выходы которого подключены к вторым выходным шинам, отличающийся тем, что, с целью повышения надежности и расширения функциональных возможностей, в него введен регистр памяти , информационные входы которого соединены с выходами сдвигового регистра, вход сброса которого подключен к шине запроса, управляющему входу генератора тактовых импульсов и входу сброса регистра памяти, выходы которого соединены с вторыми входами блока элементов И и дополнительными выходными шинами, а вход записи регистра памяти подключен к одному из выходов генератора тактовых импульсов , другой выход которого соединен с входом сдвига сдвигового регистра. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (5D 4

ОПИСАНИЕ ИЗОБРЕТ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3693951/24-21 (22) 20.01.84 (46) 30.10.85. Бюл. № 40 (72) А. Г. Забуранный и В. Н. Загребной (71) Киевский ордена Трудового Красного

Знамени завод электронных вычислительных и управляющих машин (53) 621.374.2 (088.8) (56) Авторское свидетельство СССР № 767747, кл. G 06 F 1/04, 1978.

Авторское свидетельство СССР № 849187, кл. G 06 F 1/04, 1979. (54) (57) ФОРМИРОВАТЕЛЬ СИНХРОСИГНАЛОВ, содержащий генератор тактовых импульсов, шину запроса и сдвиговый регистр, выходы которого соединены с первыми выходными шинами и первыми вхо„„SU„„1188722 A дами блока элементов И, выходы которого подключены к вторым выходным шинам, отличающийся тем, что, с целью повышения надежности и расширения функциональных возможностей, в него введен регистр памяти, информационные входы которого соединены с выходами сдвигового регистра, вход сброса которого подключен к шине запроса, управляющему входу генератора тактовых импульсов и входу сброса регистра памяти, выходы которого соединены с вторыми входами блока элементов И и дополнительными выходными шинами, а вход записи регистра памяти подключен к одному из выходов генератора тактовых импульсов, другой выход которого соединен с входом сдвига сдвигового регистра.

1188722

Изобретение относится к импульсной технике и может быть использовано в асинхронных и синхронных устройствах, которые выполняют необходимые операции с помощью синхронизирующих сигналов.

Цель изобретения — повышение надежности и расширение функциональных возможностей путем конструктивного упрощения устройства и формирования сигналов с дискретностью, равной полупериоду задающего генератора тактовых импульсов, с возможностью использования устройства в синхронном и асинхронном режимах.

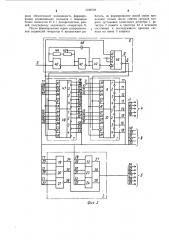

На фиг. 1 — 3 представлена блок-схема формирователя синхросигналов и временные диаграммы.

Формирователь синхросигналов содержит сдвиговый регистр 1, блок элементов

И 2, шину 3 запроса, первые 4 и вторые 5 выходные шины, генератор 6 тактовых импульсов, регистр 7 памяти и дополнительные выходные шины 8.

Шина 3 запроса соединена с управляющим входом генератора 6 тактовых импульсов входами сброса сдвигового регистра 1 и регистра 7 памяти, входы сдвига и записи которых подключены к выходам генератора 6 тактовых импульсов, а выходы сдвигового регистра 1 и регистра 7 памяти соединены соответственно с выходными шинами 4 и 8, а также с входами блока элемейтов И 2, выходы которого подключены к выходным шинам 5.

Пример. Сдвиговый регистр 1 выполнен на восьми 33-триггерах 9 и 10 с общей установкой в «0». Выходы 11 — 17 D-триггеров сдвигового регистра 1 соединены с информационными входами последующих Dтриггеров. Выходы 12 и 17 сдвигового регистра 1 соединены с первыми входами блока элементов И 2. Выходы 11, 13, 14, 16 и 18 сдвигового регистра 1 подключены к выходным шинам 4, а выходы 12, 14 — 17 сдвигового регистра 1 соединены с информационными входами регистра памяти 7.

Блок элементов И 2 содержит элементы

И 19, И-НГ 20 и 21, И 22 — 24, вторые входы 25 — 33 блока элементов И 2 соединены с выходами регистра 7 памяти, а выходы

34 — 39 блока элементов И 2 подключены к выходным шинам 5.

Генератор тактовых импульсов 6 содержит элемент И вЂ” НЕ 40, первый вход которого подключен к шине запроса 3, элемент

И-HE 41, входы которого подключены к выходу элемента И-HE 40, элемент И-НЕ

42, входы которого соединены с выходом элемента И-НЕ 41, 1К-триггер 43, S-вход которого подключен к шине запроса 3, С-вход соединен с выходом элемента И-НЕ

42, на входы 1 и К подается уровень «1», а выходы 1К-триггера 43 являются выходами генератора тактовых импульсов 6 и соедине10

55 ны с вторыми (записи и сдвига) вхс: ами регистра 7 памяти и сдвигового регистра 1.

RC-цепочку генератора 6 составляют резисторы 44 и 45 и конденсатор 46.

Регистр 7 памяти содержит восемь триггеров 47 и 48, выходы 49 — 53 которых подключены к выходным шинам 8. Шина запроса 3 подключена к входам сброса сдвигового регистра 1 и регистра памяти 7.

Формирователь синхросигналов работает следующим образом.

После включения питающего напряжения при отсутствии положительного управляющего сигнала на шине 3 запроса, происходит обнуление сдвигового регистра 1 и регистра 7 памяти, а триггер 43 по S-входу устанавливается в единичное состояние.

При появлении положительного управляющего сигнала на шине 3 запроса начинает работать управляемый задающий генератор

6 тактовых импульсов. Парафазные тактовые импульсы с выхода триггера 43, являющегося делителем частоты и предназначенного для получения импульсов генератора со скважностью два, поступают на вход сдвига сдвигового регистра 1 (с <,)-выхода триггера 43) и на вход записи регистра 7 памяти (с (,)-выхода триггера 43). По первому положительному перепаду серии тактовых импульсов происходит занесение информации в первый триггер сдвигового регистра 1. Высокий уровень сигнала с выхода 17 первого триггера сдвигового регистра 1 подается на информационные входы первого триггера регистра 7 памяти и второго триггера сдвигового регистра 1. Через полпериода тактового интервала происходит занесение единичной информации в первый триггер регистра 7 памяти и через один период — во второй триггер сдвигового регистра 1. Таким образом, через полпериода на выходе первого триггера регистра памяти 7 и через один период на выходе второго триггера сдвигового регистра 1 вырабатываются положительные перепады напряжений. Очередными перепадами сигналов с выходов генератора 6 тактовых импульсов устанавливаются в единичное состояние последующие триггеры сдвигового регистра 1 и регистра 7 памяти, как это показано на фиг. 3.

Наличие парафазных серий, формируемых с помощью триггера 43, позволяет осуществлять занесение информации в сдвиговый регистр 1 и регистр 7 памяти со сдвигом во времени, равным полупериоду генератора 6. Синхроимпульсы с выходов сдвигового регистра 1 и регистра 7 памяти поступают соответственно на выходные шины 4 и 8, а также на входы блока элементов И 2, на выходах которого происходит формирование сигналов необходимой длительности.

Организация работы сдвигового регистра 1 и регистра памяти 7 на парафазных се1188722

Даг. 2 риях обеспечивает возможность формирования управляющих сигналов с помощью блока элементов И 2 с дискретностью, равной полупериоду задающего генератора 6.

После формирования серии синхросигналов задающий генератор 6 продолжает работать, но формирование новой серии происходит только после снятия сигнала запроса (установки сдвигового регистра 1, регистра 7 памяти и триггера 43 в исходное состояние) и последующего прихода сигнала на шину 3 запроса.

1188722

Дуг. 3

Редактор Л. Пчелннская

Заказ 6745/50

&аМ д аЫ

Выпад Р

Рыба 17

Выход77

Выл ад72

Ebisod73 диюд N

Вьиад15 дыхад1E

Змаа1t

РьиадМ

8b/xo028 ю/хаа25

Рькад 26

Eb/Юа 27

Рьаod 29

Bb/хаа 31

8baod32 рь/уад,у

Й/хаа Я

Вью аа 35

Еыхад Я

Рыгад37

Юьчаа 38

Ры,1аЛ9

Составитель В. Потапов

Техред И. Верес Корректор И. Эрдейи

Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4