Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее счетчик адресов, три коммутатора, дешифратор и блок памяти микрокоманд, причем информационный вход первого коммутатора является входом логических условий устройства, управляющий вход первого коммутатора соединен с выходом кода анализируемых логических условий блока памяти микрокоманд , выход кода типа микрокоманды которого соединен с входом дещифратора, первый и второй выходы которого соединены соответственно с первым и вторым стробирующими входами первого коммутатора и с первым и вторым управляющими входами второго коммутатора, выход которого соединен с первым информационным входом третьего коммутатора, второй информационный вход которого является входом кода команды устройства, третий и четвертый выходы дешифратора соединены соответственно с первым управляющим входом третьего коммутатора и вычитающим входом счетчика адресов , выход которого соединен с адресным входом блока памяти микрокоманд, выход кода адреса которого соединен с информационным входом второго коммутатора, п выходов третьего коммутатора соединены с информационными входами счетчика адресов (где п - разрядность адреса блока памяти микрокоманд), (п+П-й выход третьего коммутатора соединен с входом управления режимом записи-счета счетчика адресов, отличающееся тем, что, с целью расширения функциональных возможностей путем реализации режима ожидания и режима возврата по запросам на прерывание, оно дополнительно содержит элемент ИЛИ и сумматор по i модулю два, причем пятый и шестой выходы дещифратора соединены соответственно с (Л первым входом элемента ИЛИ и стробирующим входом сумматора по модулю два, информационный вход которого является входом запросов на прерывание устройства, выход сумматора по модулю два соединен с входом сброса счетчика адресов, суммирующий вход которого соединен с выходом элемента ИЛИ, второй вход которого соединен с инверсным выходом первого коммутатора , прямой выход которого соединен с 00 00 вторым управляющим входом третьего коммутатора . со 4

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

yg 4 G 06 F 9/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3703447/24-24 (22) 07.12.83 (46) 30.10.85. Бюл. № 40 (72) А. В. Баринов, В. Н. Иванидзе, В. Н. Лепков и В. Ю. Поляков (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 291201, кл. G 06 F 9/22, 1969.

Авторское свидетельство СССР № 822 186, кл. G 06 F 9/46, 1979. (54) (57) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее счетчик адресов, три коммутатора, дешифратор и блок памяти микрокоманд, причем информационный вход первого коммутатора является входом логических условий устройства, управляющий вход первого коммутатора соединен с выходом кода анализируемых логических условий блока lIBMHTH микрокоманд, выход кода типа микрокоманды которого соединен с входом дешифратора, первый и второй выходы которого соединены соответственно с первым и вторым стробирующими входами первого коммутатора и с первым и вторым управляющими входами второго коммутатора, выход которого соединен с первым информационным входом третьего коммутатора, второй информационный вход которого является входом кода команды устройства, третий и четвертый выходы дешифратора соединены соответственно с пер„„SU„„1188734 A вым управляющим входом третьего коммутатора и вычитающим входом счетчика адресов, выход которого соединен с адресным входом блока памяти микрокоманд, выход кода адреса которого соединен с информационным входом второго коммутатора, и выходов третьего коммутатора соединены с информационными входами счетчика адресов (где п — разрядность адреса блока памяти микрокоманд), (и+1) -й выход третьего коммутатора соединен с входом управления режимом записи-счета счетчика адресов, отличающееся тем, что, с целью расширения функциональных возможностей путем реализации режима ожидания и режима возврата по запросам на прерывание, оно дополнительно содержит элемент ИЛИ и сумматор по модулю два, причем пятый и шестой выходы щ дешифратора соединены соответственно с первым входом элемента ИЛИ и стробирующим входом сумматора по модулю два, информационный вход которого является вхо- С дом запросов на прерывание устройства, выход сумматора по модулю два соединен с Я входом сброса счетчика адресов, суммирующий вход которого соединен с выходом элемента ИЛИ, второй вход которого соединен с инверсным выходом первого коммутатора, прямой выход которого соединен с 0 вторым управляющим входом третьего ком- Q() мутатора. 00

1188734

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых вычислительных машин и контроллеров с микропрограммным управлением.

Цель изобретения — расширение функциональных возможностей путем реализации режима ожидания и режима возврата по запросам на прерывание.

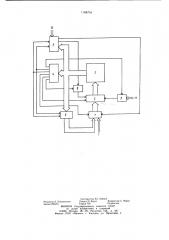

На чертеже представлена функциональная схема устройства.

Устройство содержит вход 1 кода команды, счетчик 2 адресов, блок 3 памяти микрокоманд, дешифратор 4, первый 5, второй 6 и третий 7 коммутаторы, элемент ИЛИ

8, сумматор 9 по модулю два, вход 10 логических условий и вход 11 запросов на п рерывание.

Устройство работает в шести режимах.

Первый режим — последовательное выполнение микропрограммы.

Адрес очередной микрокоманды формируется путем увеличения или уменьшения на единицу содержимого счетчика 2 сигналами с выхода дешифратора 4, подаваемыми на счетные входы счетчика 2.

Второй режим — организация безусловного ветвления микропрограммы.

Микрокоманда содержит поле адреса ветвления, поле микроопераций и поле номера признака ветвления, в котором записан код безусловного ветвления. При этом адрес ветвления подается на информационный вход коммутатора 6, а код безусловного ветвления — на один из информационных входов коммутатора 5. При исполнении микрокоманды безусловного ветвления дешифратор 4 в соответствии с содержимым микроопераций вырабатывает микрооперацию безусловного ветвления, сигналы которой поступают на управляющие входы коммутаторов 5 и 6. В результате этого адрес ветвления через коммутатор 7 записывается в счетчик 2.

Третий режим — организация условного ветвления микропрограммы.

Микрокоманда содержит поле адреса ветвления, поле микроопераций и поле номера признаков ветвления. Дешифратор 4 в соответствии с содержимым поля микроопераций вырабатывает микрооперацию условного ветвления, сигналы которой поступают на соответствующие управляющие входы коммутаторов 5 и 6. В результате этого адрес ветвления в случае наличия соответствующего признака ветвления на входе 10 записывается через коммутатор 7 в счетчик 2.

В случае отсутствия соответствующего признака на входе 10 счетчик увеличивает свое содержимое на единицу.

Четвертый режим — переход к исполнению последующей микропрограммы по

10 окончанию предыдущей.

Каждая исполняемая микропрограмма завершается микрокомандой безусловного ветвления на микрокоманду выбора адреса начала последующей микропрограммы. Пе15 ред тем, как приступить к выбору адреса, разрешается обслуживание запросов прерывания. Если запросов прерывания не поступило, то появляется микрокоманда записи адреса начала последующей микропрограммы, которая поступает с входа 1 через ком20 мутатор 7 на информационный вход счетчика 2.

Пятый режим — обработка внешних заи росов и рерывани й.

Сигналы запросов прерываний подаются на информационные сумматора 9 по модулю два и коммутатора 5. При исполнении микрокоманды обуслуживания запросов прерывания дешифратор 4 в соответствии с содержимым поля микроопераций вырабатывает микрооперацию обслуживания запросов прерывания, сигнал которой поступает на стробирующий вход сумматора 9. При наличии хотя бы одного сигнала запроса прерывания счетчик 2 сбрасывается в исходное состояние, формируя тем самым адрес первой микрокоманды микропрограммы обработ

Шестой режим — организация режима ожидания.

Начало этого режима аналогично третьему режиму. При отсутствии признака ветвления содержимое счетчика 2 увеличивается на

40 единицу. После этого на выходе дешифратора появляется микрооперация уменьшения содержимого счетчика 2 на единицу и происходит возврат к микропрограмме условного ветвления.

Цикл повторяется до тех пор, пока на информационном входе коммутатора 5 не появится признак ветвления, при этом в счетчик 2 запишется адрес ветвления.

I188734

Составитель Ю. Ланцов

Редактор Л. Пчелииская Техред И. Верес Корректор С. Черни

Заказ 6746/51 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4