Управляемый генератор импульсов

Иллюстрации

Показать всеРеферат

УПРАВЛЯЮНРЙ ГЕНЕРАТОР ИМПУЛЬСОВ, содержащий два дифференциальных приемника эмиттерно связанной логики, причем выход первого дифференциального приемника соединен с управляюпщм генератором тока, времязадающим конденсатором, вторая обкладка которого подключена к общей шине, и инвертирующим входом второго дифференциального приемника, выход которого через резистор нагрузки соединен с источником напряжения и инвертирукицим входом первого дифференциального приемника, инвертирующий вход которого соединен с источником опорного напряжения, о т л и чающийся тем, что, с целью расширения диапазона регулирования выходной частоты генератора, в него введены резистивный делитель и конденсатор , причем первый вывод резистивного делителя и первая, обкладка конденсатора соединены с выходом второго дифференциального приемника, второй вывод резистивного делителя (Л соединен с источником опорного напряжения , а средняя точка резистивного делителя и вторая обкладка конденсатора соединены с неинвертирующим входом второго дифференциального приемника. 00 00 00 ел

СОЮЗ СОВЕТСКИХ

РЕСПУБЛИН (l9) (l l) (sl)4 Н 03 К 3 28

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3688459/24-21 (22) 09. 01.84 (46) 30. 10.85. Бюл. В 40 (72) Ю.М.Терешкин (53) 621.373 (088.8) (56) Палм. Высокочастотный генератор на ЭСЛ-схеме. — "Электроника", 1975, В 11, с.61-62.

Чулков В.А. Высокочастотный генератор пилообразного напряжения.

"Приборы и техника эксперимента", 1980, Ф 6, с.96-97. (54)(57) УПРАВЛЯЮЩИЙ ГЕНЕРАТОР

ИМПУЛЬСОВ, содержащий два дифференциальных приемника эмиттерно связанной логики, причем выход первого дифференциального приемника соединен с управляющим генератором тока, времязадающим конденсатором, вторая обкладка которого подключена к общей шине, и инвертирующим входом второго дифференциального приемника, выход которого через .резистор нагрузки соединен с источником напряжения и инвертирующим входом первого диффе« ренциального приемника, инвертирующий вход которого соединен с источником опорного напряжения, о т л ич а ю шийся тем, что, с целью расширения диапазона регулирования выходной частоты генератора, в него введены резистивный делитель и конденсатор, причем первый вывод резистивного делителя и первая обкладка конденсатора соединены с выходом второго дифференциального приемника, второй вывод резистивного делителя соединен с источником опорного напряжения, а средняя точка резистивного делителя и вторая обкладка конденсатора соединены с неинвертирующим входом второго дифференциального приемника.

1188857

Изобретение относится к импульс1 ной технике и может быть использовано в качестве управляемого напряжением генератора в высокочастотных цифровых системах фаэовой автопод- 5 стройки частоты, а также генератора синхроимпульсов в устройствах вычислительной техники и автоматики.

Цель изобретения — расширение диапазона регулирования выходной частоты генератора.

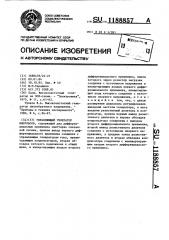

На чертеже изображена электрическая схема управляемого генератора импульсов.

Схема содержит первый дифференци- 15 альный приемник 1 эмиттерно связанной логики, второй дифференциальный приемник 2 эмиттерно связанной логики, времязадающий конденсатор 3, источник 4 опорного напряжения, уп- 2р равляющий генератор 5 тока, источник 6 напряжения, резистор 7 нагрузки, первый резистор 8 резистивного делителя, второй резистор 9 реэистивного делителя, конденсатор 10, инвертирующий вход 11 дифференциального приемника 2, неинвертирующий вход 12 дифференциального приемника

1, неинвертирующий вход 13 дифференциального приемника 2 и инвертирую- ЗО щий вход 14 дифференциального приемника 1.

Выход дифференциального приемника i соединен с выходом управляемого генератора 5 тока, инвертирующим вхо-yg дом 11 дифференциального приемника 2 и времязадающим конденсатором 3, вторая обкладка которого соединена с общей шиной.

Выход дифференциального приемни- 40 ка 2 соединен с инвертирующим входом

12 дифференциального приемника 1, через резистор 8 — с неинвертирую ì входом 13 дифференциального приемника 2 и че» ез нагрузочный резис- 4$ тор 7 — с шиной отрицательного источника 6 питания, Выход дифференциального приемника 2 является выходом генератора. Конденсатор 10 подсоединен между выходом дифферен- Я циального приемника 2 и его неинвертирующим входом 13.

Выход источника 4 опорного напряжения соединен с инвертирующим входом 14 дифференциального приемника 1 ss и через резистор 9 - с неинвертирующим входом 13 дифференциального приемника 2. г

Дифференциальный приемник 1 является стандартным интегральным дифференциальным приемником эмиттерно связанной логики и содержит переключатель тока, выполненный на транзисторах 15 и 16, эмиттеры которых соединены между собой и через генератор 17 тока подключены к шине источника отрицательного напряжения питания. База транзистора 15 соединена с неинвертирующим входом 12 дифференциального приемника 1, а коллектор— с общей шиной. База транзистора 16 соединена с инвертирующим входом 14 дифференциального приемника 1, а коллектор подсоединен к базе эмиттерного повторителя,. выполненного на транзисторе 18 и через резистор 19 к общей шине. Коллектор эмиттерного повторителя 18 соединен с общей шиной, а эмиттер — с выходом дифференциального приемника 1.

Дифференциальный приемник 2 аналогично дифференциальному приемнику

I содержит переключатель тока, выполненный на транзисторах 20 и 21, эмиттеры которых соединены между собой и через генератор 22 тока подключены к шине источника 6 отрицательного напряжения питания. База транзистора 20 соединена с неинвертирующим входом 13, а коллектор — с общей виной. База транзистора 21 соедине- на с инвертирующим входом 11 дифференциального приемника 2, а коллектор подсоединен к базе эмиттерного повторителя, выполненного на транзисторе 23, и через резистор 24— к общей шине. Коллектор эмиттерного повторителя 23 соединен с общей шиной, а эмиттер — с выходом дифференциального приемника 2.

На чертеже показан один из возможных вариантов схематического выполнения генератора 5 тока в виде резистора 25, подключенного между выходом генератора тока и входом 26 управляющего напряжения.

Дифференциальные приемники 1 и 2 формируют на своем выходе напряжение высокого логического уровня (U»») или низкого логического уровня (U„) в зависимости от напряжения на его входах. Например, если напряжение на неинвертирующем входе 12 дифференциального приемника 1 выше, чем на инвертирующем входе !4, то ток генератора 17 тока переключается в тран-.

20 (U „- U,.) ° R. (2) + UÄ °

8 9

55 з 11 знстор 15. На выходе дифференциального приемника будет высокий логический уровень напряжения, равный сумме падения напряжения на резисторе 19 за счет базового тока транзистора 18 и напряжения эмиттер-база транзистора 18. Если же на неинвертирующем входе 12 напряжение ниже, чем на инвертирующем входе 14, то ток генератора 17 тока переключится в транзистор 16. На выходе дифференциального приемника 1 будет напряжение низкого логического уровня, равное сумме падения напряжения на резисторе 19 за счет тока генератора

17 и напряжения эмиттер-база транзистора 18.

Дифференциальный приемник 2 рабо- тает аналогично дифференциальному приемнику 1.

Источник 4 опорного напряжения вырабатывает на выходе напряжение (П „ ), равное средней величине логического перепада выходных сигналов дифференциальных приемников.

Напряжения логических уровней U и U> и опорное напряжение U устанавливаются такой величины, чтобы переключатели токов дифференциальных приемников находились в ненасыщенном режиме, что обеспечивает максимальное быстродействие. Так, для серии К 500 стандартных интегральных схем эмиттерно связанной логики эти напряжения равны Ue †--О, 8 В U =

-1, 8 В, Ппп -1, 3 В.

Управляемый генератор импульсов работает следующим образом.

Времязадающий конденсатор 3 заряжается через малое выходное сапротив ление эмиттерного повторителя дифференциального приемника 1 и разряжается током управляемого генератора

5 тока до уровней напряжений порогов переключения дифференциального приемника 2 на входе 13.

Если на выходе дифференциального приемника 2 установился высокий логи ческий уровень напряжения, то на неинвертирующем входе 13 установится напряжение, которое заведомо ниже высокого логического уровня U, но вьппе напряжения Бвв и равно

«Rå(U в — U ) з д)

+ (1)

Rq + R где Ra u R величины сопротивлений резисторов 8 и 9 соответственно.

88857 4

Поскольку напряжение на входе 12 дифференциального приемника 1 выше, чем на входе 14, на выходе дифференциального приемника произойдет формирование высокого логического уровня и конденсатор 3 будет форсированно заряжаться через малое выходное сопротивление транзистора 18. Как только напряжение на конденсаторе 3 и, следовательно, на входе 11 дифференциального приемника 2 достигнет уровня напряжения на вхоце 13, произойдет переключение дифференциального приемника 2. На его выходе и на входе дифференциального приемника 1 установится напряжение низкого логического уровня U Напряжение на входе 13 диффференциального приемника 2 понизится и станет ниже напряжения U® „, но вьппе напряжения

БН и равным

Поскольку напряжение на входе 12 дифференциального приемника 1 стало ниже, чем на входе 14, ток генератора 17 тока переключится в транзистор 16 и эмиттерный повторитель 18 закроется, так как на его базе напряжение будет ниже, чем на эыиттере.

Конденсатор 3 начнет линейно разряжаться током генератора 5 тока. Скорость разряда конденсатора 3 определяется током генератора 5 тока и может управляться напряжением Епп подаваемым на вход 26. Когда напряжение на конденсаторе 3 станет ниже напряжения на входе 13 дифференциального приемника 2, ток генератора 22 тока переключится в транзистор 20 и на выходе дифференциального приемника 2 установится высокий логический уровень напряжения U>.

Процесс заряда-разряда времязадающего конденсатора 3 будет периодически повторяться и на выходе генератора будут вырабатываться положительные импульсы напряжения. Длительность импульсов будет равна сумме времени распространения сигнала в дифференциальных приемниках 1 и 2

H времени форсированного заряда конденсатора 3.

Время паузы между импульсами равно сумме времени распространения сигнала в дифференциальных приемниках

1188857

1 и 2 и времени разряда конденсатора 3 током генератора 5 тока.

Изменяя ток генератора 5 тока с помощью изменения напряжения Е„й можно изменить длительность паузы выходных импульсов и тем самым управлять частотой повторения выходных имп ул ьс о в.

Выходные логические уровни U u

U дифференциальных приемников 1 и

2 зависят от выходного тока нагрузки и определяются следующими известными упрощенными выражениями: рога переключения на входе 13 заведо10 мо ниже уровня напряжения высокого

45 где U — напряжение высокого уровБВ ня на базе транзисторов 18 и 23 за счет базовых токов;

U „ - напряжение низкого уровня на базе транзисторов 18 и 23 за счет тока генерато ров 17 и 22 тока, соответственно;

1 и I — выходные токи нагрузки соне мй ответственно при высоком и низком логическом уровне на выходе; а и r — параметры нелинейной модеэ ли и эквивалентное сопротивление эмиттерной цепи транзисторов 18 и 23;

Ч вЂ” температурный потенциал.

Выход дифференциального приемника

2 работает на постоянную токовую нагрузку, определяемую величиной нагрузочного резистора 7, а выход дифференциального приемника 1 работает на переменную токовую нагрузку генератора 5 тока, которая в процессе регулирования частоты может изменяться в широких пределах.

Как видно иэ выражений,(3) и (4), если даже пренебречь технологически не

t q +Ь вЂ” "+ ° y (3)

Н ье r а 8 йе

+Я + !и — -+ r ? (4) йи н ей т а э Нйp ми раэбросами элементов схема приемников, выходные логические уровни дифференциальных приемников 1 и 2 могут значительно отличаться друг от друга. Величина сопротивления резисторов 8 и 9 выбирается таким образом, что напряжение.(1) верхнего пологического уровня на выходе дифференциального приемника 1, а напряжение (2) нижнего порога переключения заведомо выше выходного уровня напряжения низкого логического уровня дифференциального приемника 1 во всем динамическом диапазоне регулирования генератора 5 тока и при всех возможных технологических разбросах элементов схемы дифференциальных приемников.

Конденсатор 10, включенный между выходом дифференциального приемника

2 и его неинвертирующим входом 13, форсирует переключение напряжения на входе 13, устраняя влияние паразитной емкости входа, и переключение дифференциального приемника 2 из одного логического состояния в другое. Величина емкости конденсатора 1О выбирается небольшой величины, чтобы постоянная времени перезаряда конденсатора через эквивалентное сопротивление делителя на резисторах

8 и 9 было меньше длительности выходных импульсов.

В предлагаемом управляемом генераторе импульсов верхняя граничная частота определяется временем переключения дифференциальных приемников. Для современных схем эмиттерно связанной логики это время лежит в области единиц и менее наносекунд.

Поэтому верхняя граничная частота данного генератора может достигать величины более сотни мегагерц, что позволяет использовать генератор в самых быстродействующих цифровых системах.

1188857

Составитель Ю. Романовский

Редактор Ю.Ковач Техред Т.Фанта

Корректор С.ШекмаР

Подписное

Филиал ППП "Патент", г.Ужгород, ул.Проектная,4

Заказ 6754/57 Тираж 871

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

313035, Иосква, Ж-35, Раушская наб., д.4/5